# APPLICATION MANUAL RV-8803-C7

# DTCXO Temperature Compensated Real Time Clock / Calendar Module with 12C Interface

# TABLE OF CONTENTS

| 1. | ονι          | ERVIEW                                         | 5    |

|----|--------------|------------------------------------------------|------|

|    | 1.1.         | GENERAL DESCRIPTION                            | 5    |

|    | 1.2.         | APPLICATIONS                                   | 6    |

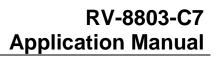

| 2. | BLC          | DCK DIAGRAM                                    | 7    |

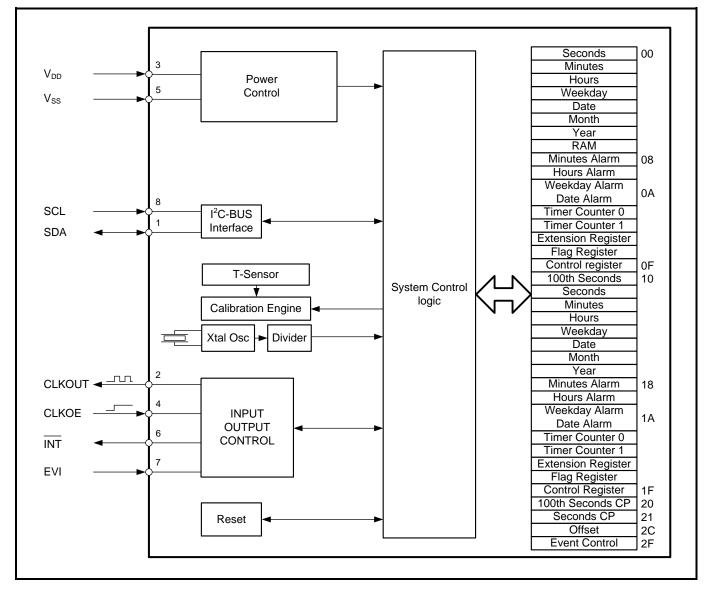

|    | 2.1.         | PINOUT                                         | 8    |

|    | 2.2.         | PIN DESCRIPTION                                | 8    |

|    | <b>2.</b> 3. | FUNCTIONAL DESCRIPTION                         | 9    |

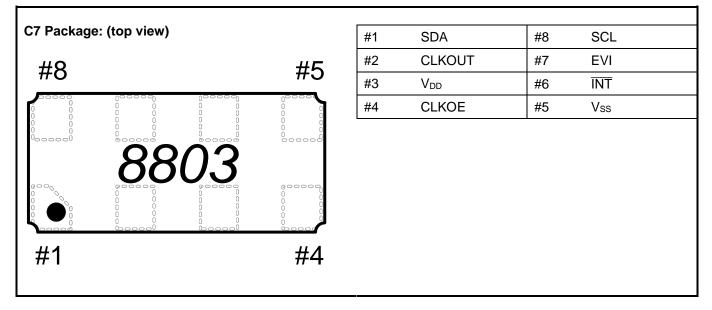

|    | 2.4.         | DEVICE PROTECTION DIAGRAM                      | 9    |

| 3. | REC          | GISTER ORGANIZATION                            | 10   |

|    | 3.1.         | REGISTER OVERVIEW                              | . 10 |

|    | 3.           | 1.1. AUTO-INCREMENTING                         | 11   |

|    | 3.2.         | CLOCK REGISTERS                                | . 12 |

|    | 3.3.         | CALENDAR REGISTERS                             | 13   |

|    | 3.4.         | ALARM REGISTERS                                | 15   |

|    | 3.5.         | PERIODIC COUNTDOWN TIMER CONTROL REGISTERS     | 17   |

|    | 3.6.         | EXTENSION REGISTER                             | 18   |

|    | 3.7.         | FLAG REGISTER                                  | 19   |

|    | 3.8.         | CONTROL REGISTER                               | 20   |

|    | 3.9.         | OFFSET REGISTER                                | 21   |

|    | 3.10.        | CAPTURE BUFFER/EVENT CONTROL REGISTERS         | 22   |

|    | 3.11.        | REGISTER RESET VALUES SUMMARY                  | 24   |

| 4. | DET          | TAILED FUNCTIONAL DESCRIPTION                  | 25   |

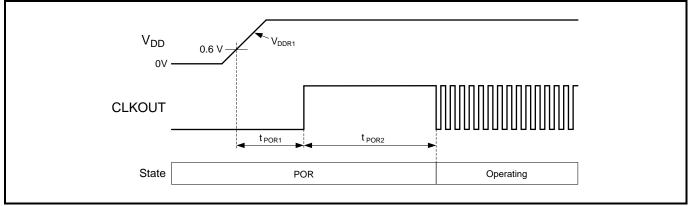

|    | 4.1.         | POWER ON RESET (POR)                           | 25   |

|    | 4.2.         | POWER MANAGEMENT                               | 25   |

|    | 4.3.         | CLOCK SOURCE                                   | 25   |

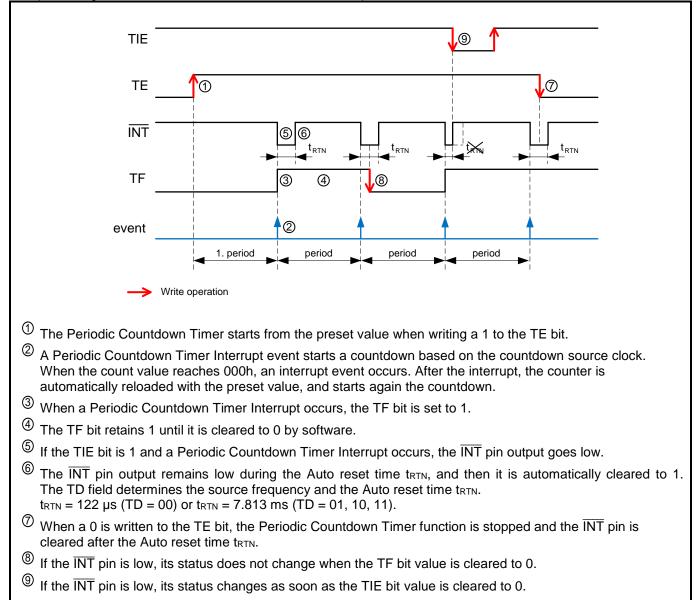

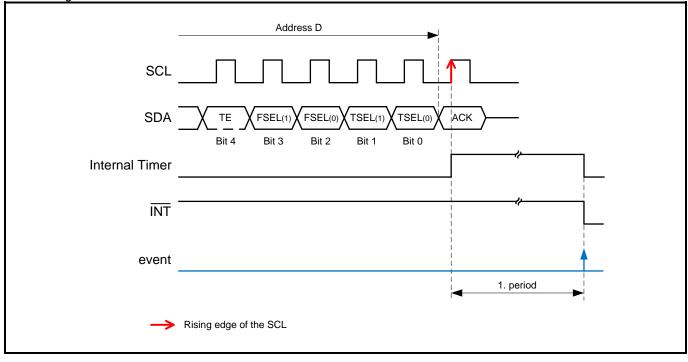

|    | 4.4.         | PERIODIC COUNTDOWN TIMER INTERRUPT FUNCTION    | 25   |

|    | 4.4          | 4.1. COMPLETE PERIODIC COUNTDOWN TIMER DIAGRAM | 26   |

|    | 4.           | 4.2. USE OF THE PERIODIC COUNTDOWN TIMER       | 27   |

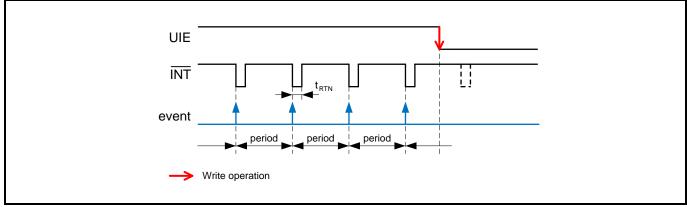

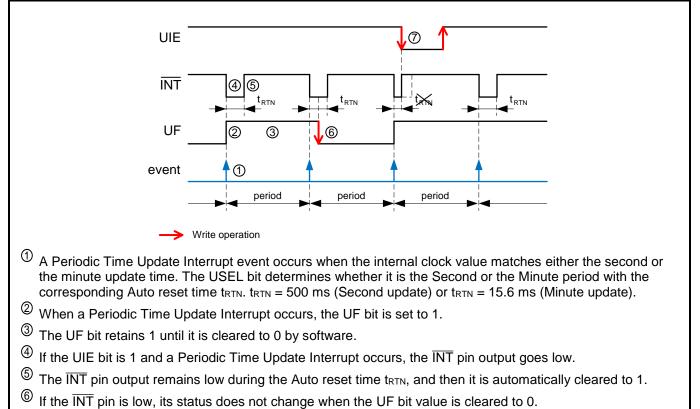

|    | 4.5.         | PERIODIC TIME UPDATE INTERRUPT FUNCTION        | 29   |

|    | 4.           | 5.1. COMPLETE PERIODIC TIME UPDATE DIAGRAM     | 29   |

|    | 4.           | 5.2. USE OF THE PERIODIC TIME UPDATE INTERRUPT | 30   |

|    | 4.6.         | ALARM INTERRUPT FUNCTION                       | 31   |

|    | 4.           | 6.1. COMPLETE ALARM DIAGRAM                    | 31   |

|    | 4.           | 6.2. USE OF THE ALARM INTERRUPT                | 32   |

|    | 4.7.         | EXTERNAL EVENT FUNCTION                        | 33   |

|    | 4.           | 7.1. COMPLETE EXTERNAL EVENT DIAGRAM           | 33   |

|    | 4.           | 7.2. USE OF THE EXTERNAL EVENT FUNCTION        | 34   |

# RV-8803-C7 Application Manual

|        | (R) |

|--------|-----|

|        |     |

| _/U@\_ |     |

|        |     |

|        |     |

|    | 4.8.             | SERVICING INTERRUPTS                                                 | . 35 |

|----|------------------|----------------------------------------------------------------------|------|

|    | 4.9.             | DIGITAL ARCHITECTURE SUMMARY                                         | . 35 |

|    | 4.10             | SYNCHRONICITY BETWEEN INT SIGNALS AND 1 HZ CLKOUT                    | . 36 |

|    | 4.11             | TIME DATA READ-OUT                                                   | . 37 |

|    | 4.               | 11.1. PROCEDURE                                                      | . 37 |

|    | 4.               | 11.2. METHODE TO CONFIRM CORRECT TIME AND CALENDAR READ-OUT          | . 37 |

| 5. | TEN              | IPERATURE COMPENSATION                                               | . 38 |

|    | 5.1 <i>.</i>     | FREQUENCIES                                                          | . 38 |

|    | 5.2 <i>.</i>     | FREQUENCY VS. TEMPERATURE CHARACTERISTICS                            | . 38 |

|    | 5.3 <i>.</i>     | COMPENSATION VALUES                                                  | . 39 |

|    | 5. <i>4.</i>     | AGING CORRECTION                                                     | . 39 |

|    | 5.5 <i>.</i>     | CLOCKING SCHEME                                                      | . 40 |

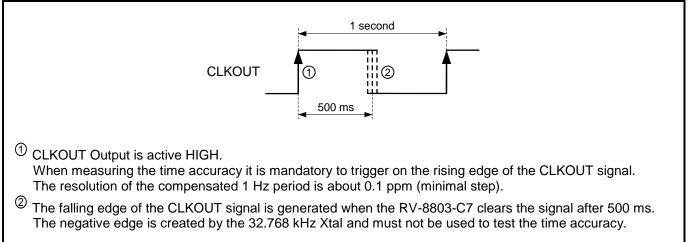

|    | 5.6 <i>.</i>     | MEASURING TIME ACCURACY AT CLKOUT PIN                                | . 41 |

|    | 5.               | 6.1. MEASURING 1 HZ AT CLKOUT PIN                                    | . 41 |

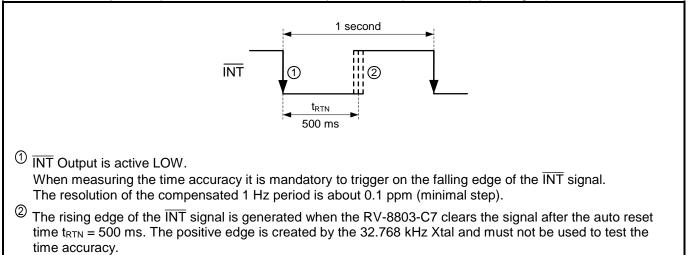

|    | 5.7.             | MEASURING TIME ACCURACY AT INT PIN                                   | . 42 |

|    | 5.               | 7.1. MEASURING 1 HZ WITH THE PERIODIC TIME UPDATE INTERRUPT FUNCTION | . 42 |

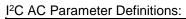

| 6. | I <sup>2</sup> C | INTERFACE                                                            | . 43 |

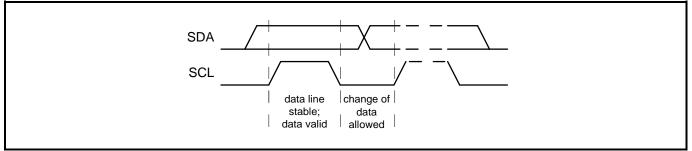

|    | 6.1.             | BIT TRANSFER                                                         | . 43 |

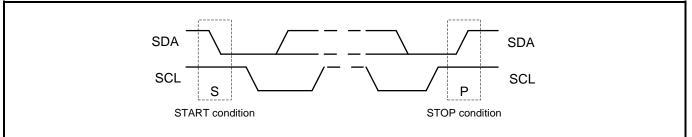

|    | 6.2.             | START AND STOP CONDITIONS                                            | . 43 |

|    | 6.3.             | DATA VALID                                                           | . 44 |

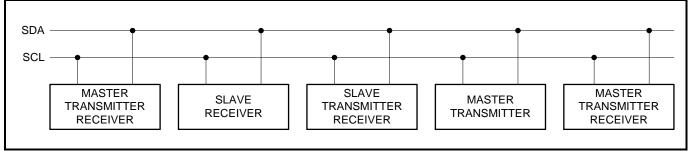

|    | 6.4.             | SYSTEM CONFIGURATION                                                 | . 44 |

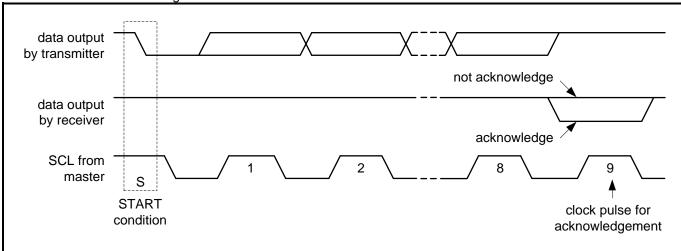

|    | 6.5.             | ACKNOWLEDGE                                                          | . 45 |

|    | 6.6.             | SLAVE ADDRESS                                                        | . 46 |

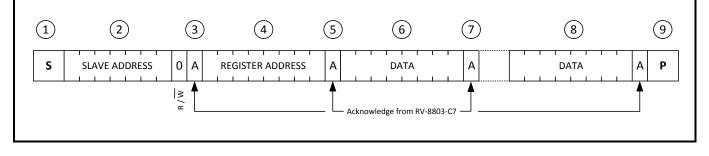

|    | 6.7.             | WRITE OPERATION                                                      | . 46 |

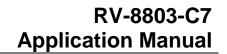

|    | 6.8.             | READ OPERATION AT SPECIFIC ADDRESS                                   | . 47 |

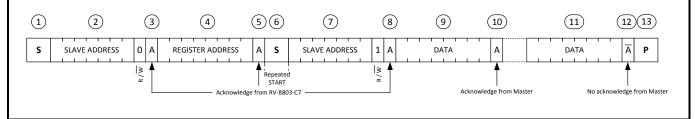

|    | 6.9 <i>.</i>     | READ OPERATION                                                       | . 48 |

| 7. | ELE              | ECTRICAL SPECIFICATIONS                                              | . 49 |

|    | 7.1.             | ABSOLUTE MAXIMUM RATINGS                                             | . 49 |

|    | 7.2.             | OPERATING PARAMETERS                                                 | . 50 |

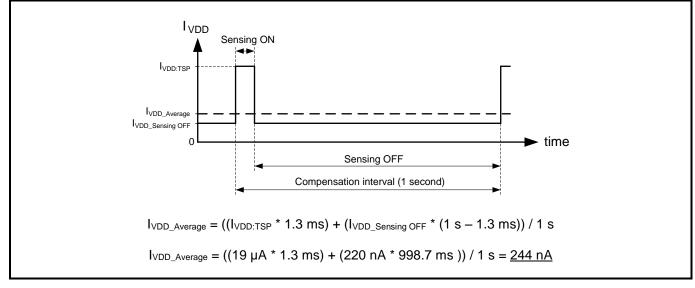

|    | 7.               | 2.1. TEMPERATURE COMPENSATION AND CURRENT CONSUMPTION                | . 51 |

|    | <b>7.3</b> .     | OSCILLATOR PARAMETERS                                                | . 52 |

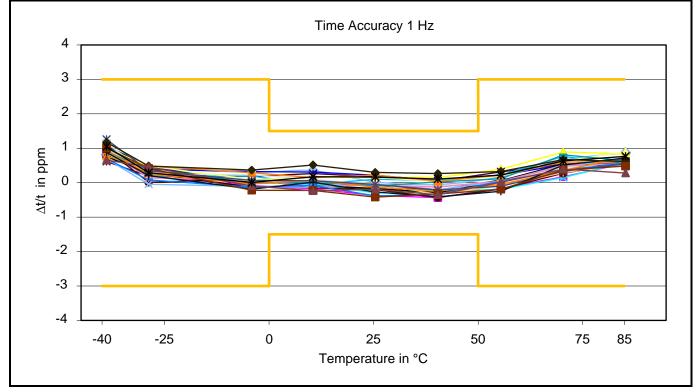

|    | 7.               | 3.1. TIME ACCURACY 1 HZ EXAMPLE                                      | . 52 |

|    | 7.4.             | POWER ON AC ELECTRICAL CHARACTERISTICS                               | . 53 |

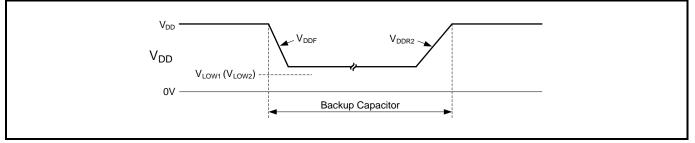

|    | 7.5.             | BACKUP AND RECOVERY                                                  | . 54 |

|    | 7.6.             | PC AC ELECTRICAL CHARACTERISTICS                                     | . 55 |

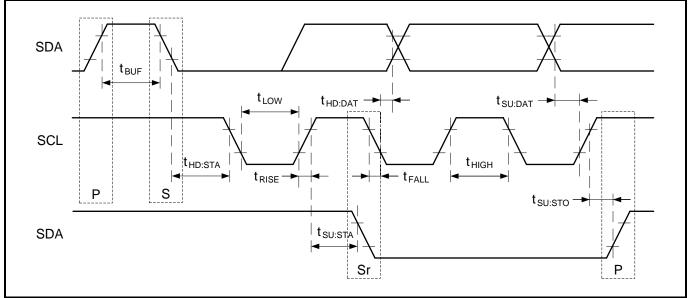

| 8. | API              | PLICATION INFORMATION                                                | . 56 |

|    | 8.1.             | OPERATING RV-8803-C7 WITH BACKUP CAPACITOR                           | . 56 |

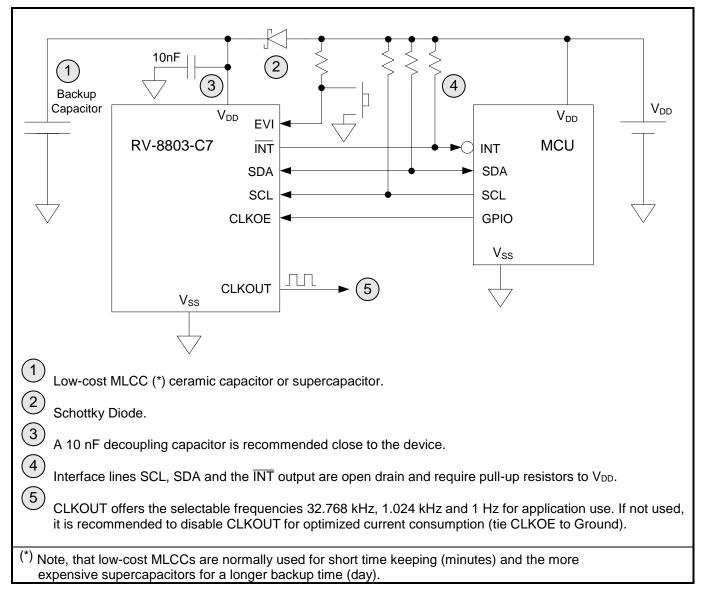

| 9. | RE               | COMMENDED REFLOW TEMPERATURE (LEADFREE SOLDERING)                    | . 57 |

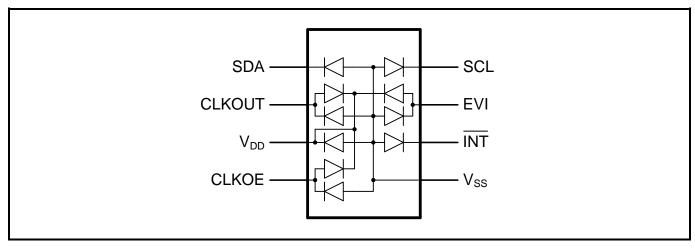

| 10 | ). PA(           | CKAGE                                                                | . 58 |

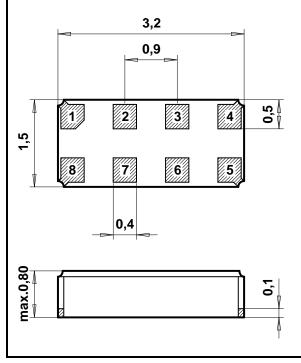

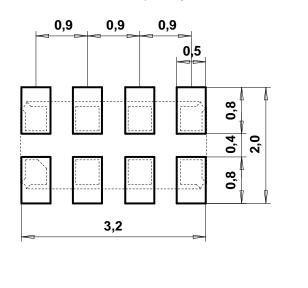

| 10.1. DIMENSIONS AND SOLDER PAD LAYOUT                                    | 58 |

|---------------------------------------------------------------------------|----|

| 10.2. MARKING AND PIN #1 INDEX                                            | 58 |

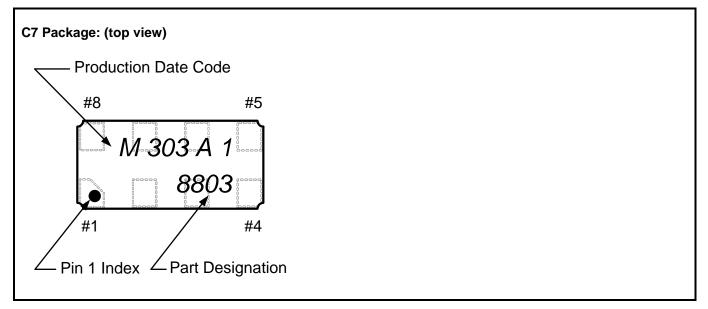

| 11. PACKING INFORMATION                                                   | 59 |

| 11.1. CARRIER TAPE                                                        | 59 |

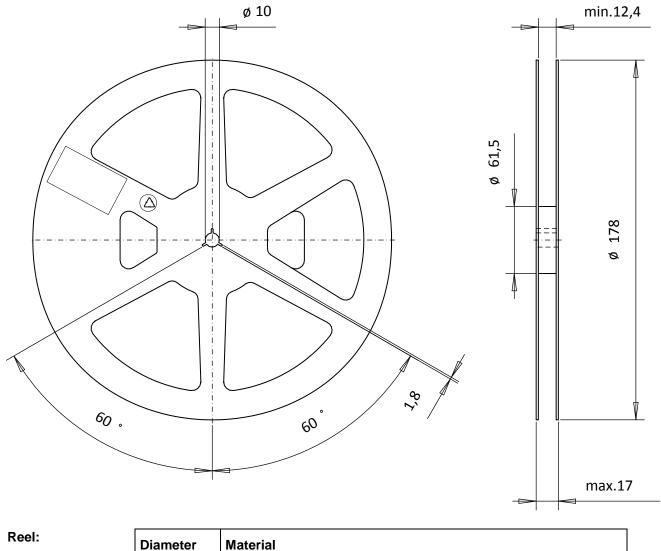

| 11.2. PARTS PER REEL                                                      | 59 |

| 11.3. REEL 7 INCH FOR 12 mm TAPE                                          | 60 |

| 11.4. HANDLING PRECAUTIONS FOR CRYSTALS OR MODULES WITH EMBEDDED CRYSTALS | 61 |

| 12. DOCUMENT REVISION HISTORY                                             | 62 |

# RV-8803-C7

# Highly accurate DTCXO Temperature Compensated Real Time Clock / Calendar Module with I<sup>2</sup>C Interface

# 1. OVERVIEW

.

- 32.768 kHz built-in "Tuning Fork" crystal oscillator

- Counters for hundredths, seconds, minutes, hours, date, month, year, century and weekday

- Factory calibrated temperature compensation

- Very high Time Accuracy

- ± 1.5 ppm 0 to +50°C

- ± 3.0 ppm -40 to +85°C

- Aging compensation with OFFSET value

- I<sup>2</sup>C (up to 400 kHz) serial interface

- Periodic Countdown Timer Interrupt function

- Periodic Time Update Interrupt function (seconds, minutes)

- Alarm Interrupts for date, weekday, hour and minute settings

- External Event Input

- Programmable Clock Output for peripheral devices (32.768 kHz, 1.024 kHz, 1 Hz) with enable/disable function (CLKOE)

- Automatic leap year calculation (2000 to 2099)

- Wide operating voltage range: 1.5 V to 5.5 V

- Very low current consumption: 240 nA ( $V_{DD} = 3.0 \text{ V}$ )

- Operating temperature range: -40 to +85°C

- Ultra-small and compact C7 package size, RoHS-compliant and 100% lead free: 3.2 x 1.5 x 0.8 mm

- Register compatible with Epson RX-8803SA/LC

# **1.1. GENERAL DESCRIPTION**

The RV-8803-C7 is a highly accurate real-time clock/calendar module due to its built-in Thermometer and Digital Temperature Compensation circuitry (DTCXO). The Temperature Compensation circuitry is factory calibrated and results in highest time accuracy of  $\pm$  3.0 ppm across the temperature range from -40 to +85°C, and additionally offers an aging offset correction.

The RV-8803-C7 has the smallest package and the lowest current consumption among all temperature compensated RTC modules. Due to its special architecture the RV-8803-C7 provides a very low current consumption of 240 nA.

# **1.2. APPLICATIONS**

The RV-8803-C7 RTC module combines key functions with outstanding performance in an ultra-small ceramic package:

- Factory calibrated Temperature Compensation with temperature measuring every second

- Ultra-Low Power consumption

- Smallest RTC module (embedded XTAL) in an ultra-small 3.2 x 1.5 x 0.8 mm lead free ceramic package.

These unique features make this product perfectly suitable for many applications:

- Communication: IoT / Wireless Sensors and Tags / Handsets / Communications equipment

- Automotive: Navigation & Tracking Systems / Dashboard / Tachometers / Engine Controller / Car Audio & Entertainment Systems

- Metering: E-Meter / Heating Counter / Smart Meters / PV Converter

- Outdoor: ATM & POS systems / Surveillance & Safety systems / Ticketing Systems

- Medical: Glucose Meter / Health Monitoring Systems

- Safety: DSLR / Security & Camera Systems / Door Lock & Access Control

- Consumer: Gambling Machines / TV & Set Top Boxes / White Goods

- Automation: DSC / Data Logger / Home & Factory Automation / Industrial and Consumer Electronics

# RV-8803-C7 Application Manual

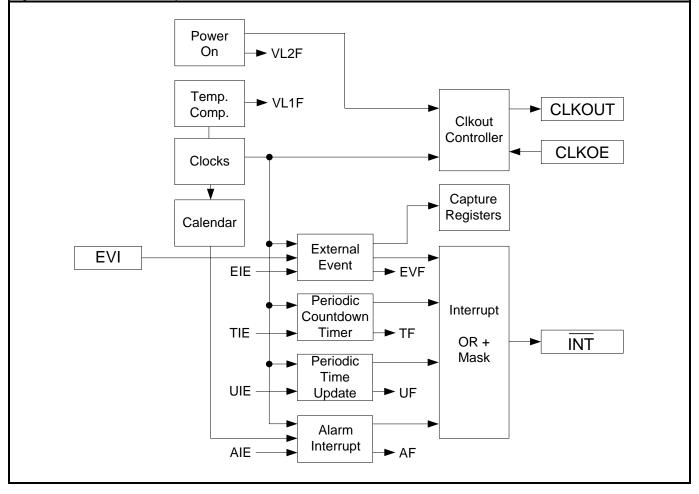

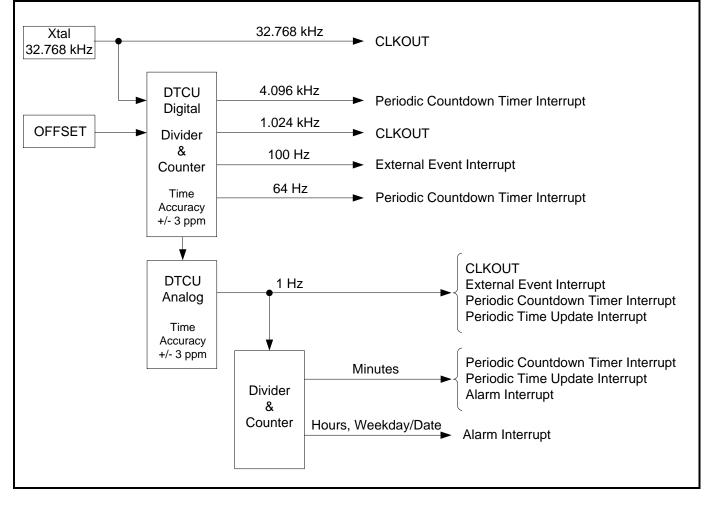

# 2. BLOCK DIAGRAM

# 2.1. PINOUT

# **2.2. PIN DESCRIPTION**

| Symbol          | Pin # | Description                                                                                                                                                                                                                                              |

|-----------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SDA             | 1     | I <sup>2</sup> C Serial Data; open-drain; requires pull-up resistor.                                                                                                                                                                                     |

| CLKOUT          | 2     | Clock Output; push-pull; controlled by CLKOE. If CLKOE is active HIGH, the CLKOUT pin drives the square wave of 32.768 kHz, 1.024 kHz or 1 Hz (Default value is 32.768 kHz). When CLKOE is tied to Ground, the CLKOUT pin is high impedance (tri-state). |

| V <sub>DD</sub> | 3     | Power Supply Voltage.                                                                                                                                                                                                                                    |

| CLKOE           | 4     | Input to enable the CLKOUT pin. If CLKOE is active HIGH, the CLKOUT pin is in output mode.<br>When CLKOE is tied to Ground, the CLKOUT pin is stopped and is high impedance (tri-state).                                                                 |

| V <sub>SS</sub> | 5     | Ground.                                                                                                                                                                                                                                                  |

| ĪNT             | 6     | Interrupt Output; open-drain; requires pull-up resistor; Used to output Alarm, Periodic Countdown<br>Timer, Periodic Time Update and External Event Interrupt signals.                                                                                   |

| EVI             | 7     | External Event Interrupt Input.                                                                                                                                                                                                                          |

| SCL             | 8     | I <sup>2</sup> C Serial Clock Input; open-drain; requires pull-up resistor.                                                                                                                                                                              |

# 2.3. FUNCTIONAL DESCRIPTION

The RV-8803-C7 is a high accurate, ultra-low power CMOS based Real-Time-Clock Module with embedded 32.768 kHz Crystal. The Xtal 32.768 kHz clock itself is not temperature compensated.

The very high Time Accuracy and stability of  $\pm$  3.0 ppm over the full temperature range from -40°C to +85°C is achieved by the built-in Digital Temperature Compensation circuitry (DTCXO). The factory calibrated correction values are located in the EEPROM and are not accessible for the user. Additionally, there is an Offset Register customer use for aging correction.

The RV-8803-C7 provides standard Clock & Calendar function including seconds, minutes, hours (24), weekdays, date, months, years (with leap year calculation) and interrupt functions for an External Event, Periodic Countdown Timer, Periodic Time Update and Alarm. Beside the standard RTC functions, it includes an integrated Temperature Sensor, an External Event Input and 1 Byte of User RAM and offers an I<sup>2</sup>C-bus (2-wire Interface). Further 2 Bytes can be used as User RAM when the Periodic Countdown Timer is not used (Timer Counter registers 0Bh, 1Bh and 0Ch, 1Ch) and further 3 Bytes when the Alarm function is not used (Alarm registers 08h, 18h; 09h, 19h and 0Ah, 1Ah).

The registers are accessed by selecting a register address and then performing read or write operations. Multiple reads or writes may be executed in a single access, with the address automatically incrementing after each byte.

# 2.4. DEVICE PROTECTION DIAGRAM

# 3. REGISTER ORGANIZATION

Registers are accessed by selecting a register address and then performing read or write operations. Multiple reads or writes may be executed in a single access, with the address automatically incrementing after each byte. The following tables Register Definitions (00h to 0Fh), (10h to 1Fh) and (20h to 2Fh) summarize the function of each register. In the table Register Definitions (00h to 0Fh) and (10h to 1Fh) the GPx bits (where x is between 0 and 5) are 6 register bits which may be used as general purpose storage. These bits are not described in the sections below. All of the GPx bits are cleared when the RV-8803-C7 powers up, and they can therefore be used to allow software to determine if a true Power-On-Reset has occurred or hold other initialization data.

- Address 00h to 0Fh: Basic time and calendar register

- Address 10h to 1Fh: Extension register ①

- Adds RAM Adds 100<sup>th</sup> Seconds counter

- Address 20h to 2Fh: Extension register ©

- Adds 100<sup>m</sup> Seconds counter Capture buffer and Event control

- sion register ② Capture

Note: When writing or reading a specific function value into/from the Address range 00h to 0Fh the value will be automatically updated in the Address range 10h to 1Fh and vice versa.

In order to not corrupt the accuracy of the temperature compensation and the Time Capture function on the highest 100<sup>th</sup> Seconds resolution, it is not possible to freeze the clock and calendar register during read-out process, as it is common practice for other RTC's.

Since the time and calendar registers cannot be frozen, there might be a condition that the time registers are incremented while read-out. To avoid reading corrupted (partially incremented) data, special measures and procedures need to be applied (see TIME DATA READ-OUT).

# 3.1. REGISTER OVERVIEW

Register Definitions, Address 00h to 0Fh (Basic time and calendar register):

| Address                              | Function           | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|--------------------------------------|--------------------|-------|-------|-------|-------|-------|-------|-------|-------|

| 00h                                  | Seconds            | 0     | 40    | 20    | 10    | 8     | 4     | 2     | 1     |

| 01h                                  | Minutes            | 0     | 40    | 20    | 10    | 8     | 4     | 2     | 1     |

| 02h                                  | Hours              | 0     | 0     | 20    | 10    | 8     | 4     | 2     | 1     |

| 03h                                  | Weekday            | 0     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

| 04h                                  | Date               | 0     | 0     | 20    | 10    | 8     | 4     | 2     | 1     |

| 05h                                  | Month              | 0     | 0     | 0     | 10    | 8     | 4     | 2     | 1     |

| 06h                                  | Year               | 80    | 40    | 20    | 10    | 8     | 4     | 2     | 1     |

| 07h                                  | RAM                |       |       |       | RAM   | data  |       |       |       |

| 08h                                  | Minutes Alarm      | AE_M  | 40    | 20    | 10    | 8     | 4     | 2     | 1     |

| 09h                                  | Hours Alarm        | AE_H  | GP0   | 20    | 10    | 8     | 4     | 2     | 1     |

| 046                                  | Weekday Alarm      |       | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

| 0Ah                                  | Date Alarm         | AE_WD | GP1   | 20    | 10    | 8     | 4     | 2     | 1     |

| 0Bh                                  | Timer Counter 0    | 128   | 64    | 32    | 16    | 8     | 4     | 2     | 1     |

| 0Ch                                  | Timer Counter 1    | GP5   | GP4   | GP3   | GP2   | 2048  | 1024  | 512   | 256   |

| 0Dh                                  | Extension Register | TEST  | WADA  | USEL  | TE    | F     | D     | Т     | D     |

| 0Eh                                  | Flag Register      | 0     | 0     | UF    | TF    | AF    | EVF   | V2F   | V1F   |

| 0Fh                                  | Control Register   | 2     | X     | UIE   | TIE   | AIE   | EIE   | 0     | RESET |

| <ul> <li>Read only. Alway</li> </ul> | /s 0.              |       |       |       |       |       |       |       |       |

| <b>Register Definitions</b> | Address | 10h to | 1Fh (E) | xtension | register | <b>①):</b> |

|-----------------------------|---------|--------|---------|----------|----------|------------|

| Address | Function                              | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------|---------------------------------------|-------|-------|-------|-------|-------|-------|-------|-------|

| 10h     | 100 <sup>th</sup> Seconds (Read Only) | 80    | 40    | 20    | 10    | 8     | 4     | 2     | 1     |

| 11h     | Seconds                               | 0     | 40    | 20    | 10    | 8     | 4     | 2     | 1     |

| 12h     | Minutes                               | 0     | 40    | 20    | 10    | 8     | 4     | 2     | 1     |

| 13h     | Hours                                 | 0     | 0     | 20    | 10    | 8     | 4     | 2     | 1     |

| 14h     | Weekday                               | 0     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

| 15h     | Date                                  | 0     | 0     | 20    | 10    | 8     | 4     | 2     | 1     |

| 16h     | Month                                 | 0     | 0     | 0     | 10    | 8     | 4     | 2     | 1     |

| 17h     | Year                                  | 80    | 40    | 20    | 10    | 8     | 4     | 2     | 1     |

| 18h     | Minutes Alarm                         | AE_M  | 40    | 20    | 10    | 8     | 4     | 2     | 1     |

| 19h     | Hours Alarm                           | AE_H  | GP0   | 20    | 10    | 8     | 4     | 2     | 1     |

| 146     | Weekday Alarm                         |       | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

| 1Ah     | Date Alarm                            | AE_WD | GP1   | 20    | 10    | 8     | 4     | 2     | 1     |

| 1Bh     | Timer Counter 0                       | 128   | 64    | 32    | 16    | 8     | 4     | 2     | 1     |

| 1Ch     | Timer Counter 1                       | GP5   | GP4   | GP3   | GP2   | 2048  | 1024  | 512   | 256   |

| 1Dh     | Extension Register                    | TEST  | WADA  | USEL  | TE    | F     | D     | Т     | D     |

| 1Eh     | Flag Register                         | 0     | 0     | UF    | TF    | AF    | EVF   | V2F   | V1F   |

| 1Fh     | Control Register                      | )     | κ     | UIE   | TIE   | AIE   | EIE   | 0     | RESET |

# Register Definitions, Address 20h to 2Fh (Extension register <sup>(2)</sup>):

| Address | Function                                 | Bit 7 | Bit 6 | Bit 5  | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------|------------------------------------------|-------|-------|--------|-------|-------|-------|-------|-------|

| 20h     | 100 <sup>th</sup> Seconds CP (Read Only) | 80    | 40    | 20     | 10    | 8     | 4     | 2     | 1     |

| 21h     | Seconds CP (Read Only)                   | 0     | 40    | 20     | 10    | 8     | 4     | 2     | 1     |

| 2Ch     | Offset                                   | 0     | 0     | OFFSET |       |       |       |       |       |

| 2Fh     | Event Control                            | ECP   | EHL   | E      | Т     | 0     | 0     | 0     | ERST  |

# 3.1.1.AUTO-INCREMENTING

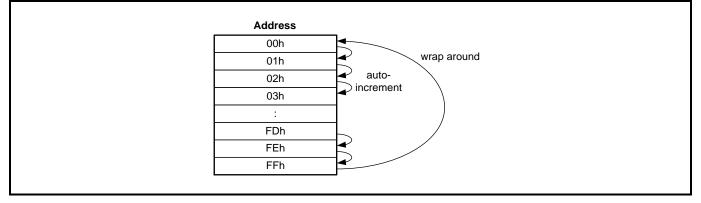

When address is automatically incremented, wrap around occurs from the address FFh to the address 00h (see figure below).

Auto-incrementing of the registers:

# **3.2. CLOCK REGISTERS**

# 10h - 100<sup>th</sup> Seconds (Read Only)

This register holds the count of hundredths of seconds, in two binary coded decimal (BCD) digits. Values will be from 00 to 99.

| Address | Function                              | Bit 7    | Bit 6                               | Bit 5         | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |  |

|---------|---------------------------------------|----------|-------------------------------------|---------------|-------|-------|-------|-------|-------|--|

| 10h     | 100 <sup>th</sup> Seconds (Read Only) | 80       | 40                                  | 20            | 10    | 8     | 4     | 2     | 1     |  |

| TUN     | Reset                                 | 0        | 0                                   | 0             | 0     | 0     | 0     | 0     | 0     |  |

| Bit     | Symbol                                | Value    | Description                         |               |       |       |       |       |       |  |

| 7:0     | 100 <sup>th</sup> Seconds (Read Only) | 00 to 99 | The 100 <sup>th</sup><br>register o | 0 0 0 0 0 0 0 |       |       |       |       |       |  |

# 00h, 11h - Seconds

This register holds the count of seconds, in two binary coded decimal (BCD) digits. Values will be from 00 to 59.

| Addresses               | Function | Bit 7    | Bit 6                                            | Bit 5 | Bit 4 | Bit 3       | Bit 2    | Bit 1 | Bit 0 |

|-------------------------|----------|----------|--------------------------------------------------|-------|-------|-------------|----------|-------|-------|

| 00h, 11h <sup>(1)</sup> | Seconds  | 0        | 40                                               | 20    | 10    | 8           | 4        | 2     | 1     |

| 00n, 11n. <sup>07</sup> | Reset    | 0        | 0                                                | 0     | 0     | 0           | 0        | 0     | 0     |

| Bit                     | Symbol   | Value    |                                                  |       | l     | Descriptior | <u>ו</u> |       |       |

| 7                       | 0        | 0        | Read only. Always 0.                             |       |       |             |          |       |       |

| 6:0                     | Seconds  | 00 to 59 | Holds the count of seconds, coded in BCD format. |       |       |             |          |       |       |

# 01h, 12h - Minutes

This register holds the count of minutes, in two binary coded decimal (BCD) digits. Values will be from 00 to 59.

| Addresses               | Function | Bit 7    | Bit 6                | Bit 5                                            | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |  |

|-------------------------|----------|----------|----------------------|--------------------------------------------------|-------|-------|-------|-------|-------|--|

| 01h, 12h <sup>(1)</sup> | Minutes  | 0        | 40                   | 20                                               | 10    | 8     | 4     | 2     | 1     |  |

| 0111, 1211.7            | Reset    | 0        | 0                    | 0                                                | 0     | 0     | 0     | 0     | 0     |  |

| Bit                     | Symbol   | Value    | Description          |                                                  |       |       |       |       |       |  |

| 7                       | 0        | 0        | Read only. Always 0. |                                                  |       |       |       |       |       |  |

| 6:0                     | Minutes  | 00 to 59 | Holds the            | Holds the count of minutes, coded in BCD format. |       |       |       |       |       |  |

# 02h, 13h - Hours

This register holds the count of hours, in two binary coded decimal (BCD) digits. Values will be from 00 to 23.

| Addresses               | Function | Bit 7    | Bit 6                                          | Bit 5       | Bit 4 | Bit 3       | Bit 2 | Bit 1 | Bit 0 |

|-------------------------|----------|----------|------------------------------------------------|-------------|-------|-------------|-------|-------|-------|

| 02h, 13h <sup>(1)</sup> | Hours    | 0        | 0                                              | 20          | 10    | 8           | 4     | 2     | 1     |

| 020, 130                | Reset    | 0        | 0                                              | 0           | 0     | 0           | 0     | 0     | 0     |

| Bit                     | Symbol   | Value    |                                                |             | I     | Descriptior | า     |       |       |

| 7:6                     | 0        | 0        | Read only                                      | /. Always 0 |       |             |       |       |       |

| 5:0                     | Hours    | 00 to 23 | Holds the count of hours, coded in BCD format. |             |       |             |       |       |       |

# **3.3. CALENDAR REGISTERS**

# 03h, 14h - Weekday

This register holds the current day of the week. Each bit represents one weekday that is assigned by the user. Values will range from 1 to 7. Do not set 1 to more than one bit.

| Addresses               | Function                  | Bit 7  | Bit 6     | Bit 5                | Bit 4       | Bit 3       | Bit 2        | Bit 1        | Bit 0 |  |  |  |

|-------------------------|---------------------------|--------|-----------|----------------------|-------------|-------------|--------------|--------------|-------|--|--|--|

| 0.2h 4.4h(1)            | Weekday                   | 0      | 7         | 6                    | 5           | 4           | 3            | 2            | 1     |  |  |  |

| 03h, 14h <sup>(1)</sup> | Reset                     | 0      | 1         | 0                    | 0           | 0           | 0            | 0            | 0     |  |  |  |

| Bit                     | Symbol                    | Value  |           |                      |             | Descriptior | า            |              |       |  |  |  |

| 7                       | 0                         | 0      | Read only | Read only. Always 0. |             |             |              |              |       |  |  |  |

| 6:0                     | Weekday                   | 1 to 7 | Holds the | weekday c            | ounter valu | e. Do not s | et 1 to more | e than one b | oit.  |  |  |  |

| Weekday                 |                           | Bit 7  | Bit 6     | Bit 5                | Bit 4       | Bit 3       | Bit 2        | Bit 1        | Bit 0 |  |  |  |

| Weekday 1               |                           |        | 0         | 0                    | 0           | 0           | 0            | 0            | 1     |  |  |  |

| Weekday 2               |                           |        | 0         | 0                    | 0           | 0           | 0            | 1            | 0     |  |  |  |

| Weekday 3               |                           |        | 0         | 0                    | 0           | 0           | 1            | 0            | 0     |  |  |  |

| Weekday 4               |                           | 0      | 0         | 0                    | 0           | 1           | 0            | 0            | 0     |  |  |  |

| Weekday 5               |                           |        | 0         | 0                    | 1           | 0           | 0            | 0            | 0     |  |  |  |

| Weekday 6               | ,                         |        | 0         | 1                    | 0           | 0           | 0            | 0            | 0     |  |  |  |

| Weekday 7 – Defau       | /eekday 7 – Default value |        | 1         | 0                    | 0           | 0           | 0            | 0            | 0     |  |  |  |

#### 04h, 15h – Date

This register holds the current day of the month, in two binary coded decimal (BCD) digits. Values will range from 00 to 31. The Reset value 00 after POR has to be replaced by a valid initial value (01 to 31). Leap years are correctly handled from 2000 to 2099.

| Addresses               | Function | Bit 7    | Bit 6     | Bit 5       | Bit 4 | Bit 3       | Bit 2 | Bit 1                        | Bit 0 |

|-------------------------|----------|----------|-----------|-------------|-------|-------------|-------|------------------------------|-------|

| 04h, 15h <sup>(1)</sup> | Date     | 0        | 0         | 20          | 10    | 8           | 4     | 2                            | 1     |

| 04n, 15n. <sup></sup> / | Reset    | 0        | 0         | 0           | 0     | 0           | 0     | 0                            | 0     |

| Bit                     | Symbol   | Value    |           |             | I     | Description | ı     |                              |       |

| 7:6                     | 0        | 0        | Read only | y. Always 0 |       |             |       |                              |       |

| 5:0                     | Date     | 00 to 31 |           |             |       |             |       | mat. The Re<br>I value (01 t |       |

#### 05h, 16h - Month

This register holds the current month, in two binary coded decimal (BCD) digits. Values will range from 01 to 12.

| Addresses               | Function | Bit 7    | Bit 6                                         | Bit 5      | Bit 4 | Bit 3       | Bit 2 | Bit 1 | Bit 0 |

|-------------------------|----------|----------|-----------------------------------------------|------------|-------|-------------|-------|-------|-------|

| 05h, 16h <sup>(1)</sup> | Month    | 0        | 0                                             | 0          | 10    | 8           | 4     | 2     | 1     |

| Uon, 10n. <sup>,</sup>  | Reset    | 0        | 0                                             | 0          | 0     | 0           | 0     | 0     | 1     |

| Bit                     | Symbol   | Value    |                                               |            |       | Descriptior | 1     |       |       |

| 7:5                     | 0        | 0        | Read only                                     | . Always 0 |       |             |       |       |       |

| 4:0                     | Month    | 01 to 12 | Holds the current month, coded in BCD format. |            |       |             |       |       |       |

# 06h, 17h - Year

This register holds the current year, in two binary coded decimal (BCD) digits. Values will range from 00 to 99.

| Addresses               | Function | Bit 7    | Bit 6     | Bit 5       | Bit 4        | Bit 3       | Bit 2 | Bit 1 | Bit 0 |

|-------------------------|----------|----------|-----------|-------------|--------------|-------------|-------|-------|-------|

| 06h 17h <sup>(1)</sup>  | Year     | 80       | 40        | 20          | 10           | 8           | 4     | 2     | 1     |

| 06h, 17h <sup>(1)</sup> | Reset    | 0        | 0         | 0           | 0            | 0           | 0     | 0     | 0     |

| Bit                     | Symbol   | Value    |           |             | [            | Descriptior | ı     |       |       |

| 7:0                     | Year     | 00 to 99 | Holds the | current yea | ar, coded in | BCD forma   | at.   |       |       |

# 07h - RAM

This register holds the bits for general purpose use.

| Address | Function | Bit 7         | Bit 6    | Bit 5 | Bit 4 | Bit 3       | Bit 2 | Bit 1 | Bit 0 |

|---------|----------|---------------|----------|-------|-------|-------------|-------|-------|-------|

| 07h     | RAM      |               |          |       | RAM   | data        |       |       |       |

| 07h     | Reset    | 0             | 0        | 0     | 0     | 0           | 0     | 0     | 0     |

| Bit     | Symbol   | Value         |          |       | I     | Description | า     |       |       |

| 7:0     | RAM      | 00h to<br>FFh | User RAM | 1     |       |             |       |       |       |

# **3.4. ALARM REGISTERS**

# 08h, 18h – Minutes Alarm

This register holds the Minutes Alarm Enable bit AE\_M and the alarm value for minutes, in two binary coded decimal (BCD) digits. Values will range from 00 to 59.

| Addresses               | Function      | Bit 7    | Bit 6                                                                                                  | Bit 5        | Bit 4  | Bit 3       | Bit 2 | Bit 1 | Bit 0 |  |

|-------------------------|---------------|----------|--------------------------------------------------------------------------------------------------------|--------------|--------|-------------|-------|-------|-------|--|

| 08h, 18h <sup>(1)</sup> | Minutes Alarm | AE_M     | 40                                                                                                     | 20           | 10     | 8           | 4     | 2     | 1     |  |

| 000, 100                | Reset         | 0        | 0                                                                                                      | 0            | 0      | 0           | 0     | 0     | 0     |  |

| Bit                     | Symbol        | Value    |                                                                                                        |              | I      | Description | า     |       |       |  |

| _                       |               | Minutes  | Minutes Alarm Enable bit. Enables alarm together with AE_H and AE_WD (see USE OF THE ALARM INTERRUPT). |              |        |             |       |       |       |  |

| 7                       | AE_M          | 0        | Minutes A                                                                                              | Alarm is ena | abled. |             |       |       |       |  |

|                         |               | 1        | Minutes Alarm is disabled.                                                                             |              |        |             |       |       |       |  |

| 6:0                     | Minutes Alarm | 00 to 59 | Holds the alarm value for minutes, coded in BCD format.                                                |              |        |             |       |       |       |  |

### 09h, 19h – Hours Alarm

This register holds the Hours Alarm Enable bit AE\_H and the alarm value for hours, in two binary coded decimal (BCD) digits. Values will range from 00 to 23.

| Addresses               | Function    | Bit 7     | Bit 6                                                                                               | Bit 5        | Bit 4 | Bit 3      | Bit 2 | Bit 1 | Bit 0 |  |

|-------------------------|-------------|-----------|-----------------------------------------------------------------------------------------------------|--------------|-------|------------|-------|-------|-------|--|

| 09h, 19h <sup>(1)</sup> | Hours Alarm | AE_H      | GP0                                                                                                 | 20           | 10    | 8          | 4     | 2     | 1     |  |

| 091, 1911               | Reset       | 0         | 0                                                                                                   | 0            | 0     | 0          | 0     | 0     | 0     |  |

| Bit                     | Symbol      | Value     |                                                                                                     |              |       | Descriptio | า     |       |       |  |

|                         |             | Hours Ala | Hours Alarm Enable bit. Enables alarm together with AE_M and AE_WD (see USE O THE ALARM INTERRUPT). |              |       |            |       |       |       |  |

| 7                       | AE_H        | 0         | Hours Ala                                                                                           | arm is enab  | led.  |            |       |       |       |  |

|                         |             | 1         | Hours Ala                                                                                           | arm is disab | led.  |            |       |       |       |  |

| 6                       | GP0         | 0 or 1    | Register bit for general purpose use.                                                               |              |       |            |       |       |       |  |

| 5:0                     | Hours Alarm | 00 to 23  |                                                                                                     |              |       |            |       |       |       |  |

# 0Ah, 1Ah – Weekday/Date Alarm

This register holds the Weekday/Date Alarm Enable bit AE\_WD. If the WADA bit is 0 (Bit 6 in Register 0Dh, 1Dh), it holds the alarm value for the day of the week (weekdays assigned by the user). Multiple days can be selected. Values will range from 0000001 to 1111111. If the WADA bit is 1, it holds the alarm value for the date, in two binary coded decimal (BCD) digits. Values will range from 01 to 31. Leap years are correctly handled from 2000 to 2099.

# Weekday Alarm when WADA = 0 (Bit 6 in Register 0Dh, 1Dh)

| Addresses               | Function      | Bit 7                    | Bit 6                                                         | Bit 5       | Bit 4       | Bit 3      | Bit 2 | Bit 1      | Bit 0    |

|-------------------------|---------------|--------------------------|---------------------------------------------------------------|-------------|-------------|------------|-------|------------|----------|

| 00h 10h(1)              | Weekday Alarm | AE_WD                    | 7                                                             | 6           | 5           | 4          | 3     | 2          | 1        |

| 0Ah, 1Ah <sup>(1)</sup> | Reset         | 0                        | 0                                                             | 0           | 0           | 0          | 0     | 0          | 0        |

| Bit                     | Symbol        | Value                    |                                                               |             |             | Descriptio | n     |            |          |

| _                       |               | Weekda                   | y/Date Alar                                                   |             |             | alarm toge |       | E_M and Al | E_H (see |

| 7                       | AE_WD         | 0                        | Weekday                                                       | /Date Alarn | n is enable | d.         |       |            |          |

|                         |               | 1                        | Weekday/Date Alarm is disabled.                               |             |             |            |       |            |          |

| 6:0                     | Weekday Alarm | 0000001<br>to<br>1111111 | Holds the weekday alarm value. Multiple days can be selected. |             |             |            |       |            |          |

| Weekday Alarm           | ·             | Bit 7                    | Bit 6                                                         | Bit 5       | Bit 4       | Bit 3      | Bit 2 | Bit 1      | Bit 0    |

| Weekday 1 Alarm         |               |                          | 0                                                             | 0           | 0           | 0          | 0     | 0          | 1        |

| Weekday 2 Alarm         |               |                          | 0                                                             | 0           | 0           | 0          | 0     | 1          | 0        |

| Weekday 3 Alarm         |               |                          | 0                                                             | 0           | 0           | 0          | 1     | 0          | 0        |

| Weekday 4 Alarm         |               | 0 or 1                   | 0                                                             | 0           | 0           | 1          | 0     | 0          | 0        |

| Weekday 5 Alarm         |               |                          |                                                               |             |             |            |       |            | 0        |

| Weekday 6 Alarm         |               |                          | 0                                                             | 1           | 0           | 0          | 0     | 0          | 0        |

| Weekday 7 Alarm         |               |                          | 1                                                             | 0           | 0           | 0          | 0     | 0          | 0        |

# Date Alarm when WADA = 1 (Bit 6 in Register 0Dh, 1Dh)

|                         | · · · · · · · · · · · · · · · · · · · |                   |                                                                                                               |             |              |              |            |       |       |  |

|-------------------------|---------------------------------------|-------------------|---------------------------------------------------------------------------------------------------------------|-------------|--------------|--------------|------------|-------|-------|--|

| Addresses               | Function                              | Bit 7             | Bit 6                                                                                                         | Bit 5       | Bit 4        | Bit 3        | Bit 2      | Bit 1 | Bit 0 |  |

| 0Ah. 1Ah <sup>(1)</sup> | Date Alarm                            | AE_WD             | GP1                                                                                                           | 20          | 10           | 8            | 4          | 2     | 1     |  |

| UAN, TAN <sup>®</sup>   | Reset                                 | 0                 | 0                                                                                                             | 0           | 0            | 0            | 0          | 0     | 0     |  |

| Bit                     | Symbol                                | Value Description |                                                                                                               |             |              |              |            |       |       |  |

|                         |                                       | Weekda            | /eekday/Date Alarm Enable bit. Enables alarm together with AE_M and AE_H (see<br>USE OF THE ALARM INTERRUPT). |             |              |              |            |       |       |  |

| 7                       | AE_WD                                 | 0                 | Weekday                                                                                                       | /Date Alarn | n is enabled | ł            |            |       |       |  |

|                         |                                       | 1                 | Weekday                                                                                                       | /Date Alarn | n is disable | d            |            |       |       |  |

| 6                       | GP1                                   | 0 or 1            | Register bit for general purpose use.                                                                         |             |              |              |            |       |       |  |

| 5:0                     | Date Alarm                            | 01 to 31          | Holds the                                                                                                     | alarm valu  | e for the da | te, coded ir | n BCD form | at.   |       |  |

# **3.5. PERIODIC COUNTDOWN TIMER CONTROL REGISTERS**

# 0Bh, 1Bh – Timer Counter 0

This register is used to set the lower 8 bits of the preset value for the Periodic Countdown Timer.

| Addresses               | Function        | Bit 7         | Bit 6 | Bit 5 | Bit 4 | Bit 3       | Bit 2 | Bit 1        | Bit 0   |

|-------------------------|-----------------|---------------|-------|-------|-------|-------------|-------|--------------|---------|

| 0Bh. 1Bh <sup>(1)</sup> | Timer Counter 0 | 128           | 64    | 32    | 16    | 8           | 4     | 2            | 1       |

|                         | Reset           | 0             | 0     | 0     | 0     | 0           | 0     | 0            | 0       |

| Bit                     | Symbol          | Value         |       |       | I     | Descriptior | า     |              |         |

| 7:0                     | Timer Counter 0 | 00h to<br>FFh |       |       |       | c Countdow  |       | wer 8 bit) ( | see USE |

# 0Ch, 1Ch - Timer Counter 1

This register is used to set the upper 4 bits of the preset value for the Periodic Countdown Timer.

| Addresses               | Function        | Bit 7       | Bit 6       | Bit 5                    | Bit 4       | Bit 3 | Bit 2 | Bit 1         | Bit 0   |

|-------------------------|-----------------|-------------|-------------|--------------------------|-------------|-------|-------|---------------|---------|

| 0Ch, 1Ch <sup>(1)</sup> | Timer Counter 1 | GP5         | GP4         | GP3                      | GP2         | 2048  | 1024  | 512           | 256     |

|                         | Reset           | 0           | 0           | 0                        | 0           | 0     | 0     | 0             | 0       |

|                         | -               |             |             |                          |             |       |       |               |         |

| Bit                     | Symbol          | Value       | Description |                          |             |       |       |               |         |

| 7                       | GP2             | 0 or 1      | Register I  | bit for gene             | ral purpose | use.  |       |               |         |

| 6                       | GP3             | 0 or 1      | Register I  | bit for gene             | ral purpose | use.  |       |               |         |

| 5                       | GP4             | 0 or 1      | Register I  | bit for gene             | ral purpose | use.  |       |               |         |

| 4                       | GP5             | 0 or 1      | Register I  | bit for gene             | ral purpose | use.  |       |               |         |

| 3:0                     | Timer Counter 1 | 0h to<br>Fh |             | et value for<br>PERIODIC |             |       |       | pper 4 bit) ( | see USE |

# **3.6. EXTENSION REGISTER**

### 0Dh, 1Dh - Extension Register

This register is used to specify the target for the Alarm Interrupt function and the Periodic Time Update Interrupt function and to select or set operations for the Periodic Countdown Timer.

| Addresses               | Function                  | Bit 7                                                                                                                                                                      | Bit 6                                                                                                                                                                                                                                                                                                  | Bit 5                       | Bit 4                       | Bit 3                          | Bit 2           | Bit 1        | Bit 0      |  |  |

|-------------------------|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|-----------------------------|--------------------------------|-----------------|--------------|------------|--|--|

| 0Dh, 1Dh <sup>(1)</sup> | Extension Register        | TEST                                                                                                                                                                       | WADA                                                                                                                                                                                                                                                                                                   | USEL                        | TE                          | F                              | D               | ٦            | ٢D         |  |  |

|                         | Reset                     | 0                                                                                                                                                                          | 0                                                                                                                                                                                                                                                                                                      | 0                           | 0                           | 0                              | 0               | 0            | 0          |  |  |

| Bit                     | Symbol                    | Value                                                                                                                                                                      | Description                                                                                                                                                                                                                                                                                            |                             |                             |                                |                 |              |            |  |  |

| 7                       | TEST                      | 0                                                                                                                                                                          | a 1 to this                                                                                                                                                                                                                                                                                            | s bit when v                | vriting in thi              | . Its value s<br>s register. Z | Zero for nor    | mal operati  | ion.       |  |  |

|                         |                           | Weel                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                        |                             |                             | bit. This bit<br>for the Ala   |                 |              | ner the    |  |  |

| 6                       | WADA                      | 0                                                                                                                                                                          | Weekday                                                                                                                                                                                                                                                                                                | is the sour                 | ce for the A                | larm Interro                   | upt function    | . – Default  | value      |  |  |

|                         |                           | 1                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                        |                             |                             | Interrupt fu                   |                 |              |            |  |  |

| _                       |                           | Update                                                                                                                                                                     | Interrupt Se                                                                                                                                                                                                                                                                                           |                             |                             | er Second on<br>terrupt fund   |                 | date for the | e Periodic |  |  |

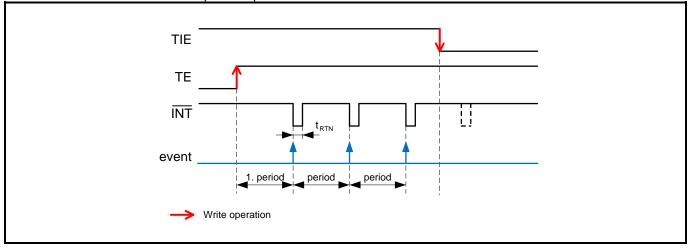

| 5                       | USEL                      | 0                                                                                                                                                                          | Second u                                                                                                                                                                                                                                                                                               | pdate (Auto                 | o reset time                | e t <sub>RTN</sub> = 500       | ms). – Defa     | ault value   |            |  |  |

|                         |                           | 1                                                                                                                                                                          | Minute up                                                                                                                                                                                                                                                                                              | odate (Auto                 | reset time                  | t <sub>RTN</sub> = 15.6        | ms).            |              |            |  |  |

|                         |                           | Periodi                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                        |                             |                             | nis bit contro<br>ner Interrup |                 |              | ig for the |  |  |

| 4                       | TE                        | <ul> <li>Stops the Periodic Countdown Timer Interrupt function. – Default value</li> <li>Starts the Periodic Countdown Timer Interrupt function (a countdown st</li> </ul> |                                                                                                                                                                                                                                                                                                        |                             |                             |                                |                 |              |            |  |  |

|                         |                           | 1                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                        | e Periodic C<br>eset value) |                             | Timer Interr                   | upt functior    | n (a countd  | own starts |  |  |

|                         |                           | CLKOUT frequency selection. Sets the output frequency on the CLKOUT pin.                                                                                                   |                                                                                                                                                                                                                                                                                                        |                             |                             |                                |                 |              |            |  |  |

|                         |                           | 00                                                                                                                                                                         | 00 32.768 kHz – Default value                                                                                                                                                                                                                                                                          |                             |                             |                                |                 |              |            |  |  |

| 3:2                     | FD                        | 01                                                                                                                                                                         | 1.024 kH                                                                                                                                                                                                                                                                                               | Z                           |                             |                                |                 |              |            |  |  |

|                         |                           | 10                                                                                                                                                                         | 1 Hz                                                                                                                                                                                                                                                                                                   |                             |                             |                                |                 |              |            |  |  |

|                         |                           | 11                                                                                                                                                                         | 32.768 kl                                                                                                                                                                                                                                                                                              |                             |                             |                                |                 |              |            |  |  |

| 1:0                     | тр                        | 00 to 11                                                                                                                                                                   | Timer source frequency selection. Sets the countdown source clock for the Periodic Countdown Timer Interrupt function. With this setting the Auto reset time t <sub>RTN</sub> and the effect of the RESET bit is also defined. See table below (see also PERIODIC COUNTDOWN TIMER INTERRUPT FUNCTION). |                             |                             |                                |                 |              | e Auto     |  |  |

| TD Value                | Timer source frequency    | cy Countdown period t <sub>RTN</sub> RESET bit                                                                                                                             |                                                                                                                                                                                                                                                                                                        |                             |                             |                                |                 | bit          |            |  |  |

| 00                      | 4.096 kHz – Default value | 244.14 µs                                                                                                                                                                  | 6                                                                                                                                                                                                                                                                                                      | 12                          | 22 µs                       |                                | The F<br>effect | RESET bit I  | nas no     |  |  |

| 01                      | 64 Hz                     | 15.625 m                                                                                                                                                                   | S                                                                                                                                                                                                                                                                                                      | 7.                          | 7.183 ms If the RESET bit = |                                |                 | = 1, the     |            |  |  |

| 10                      | 1 Hz                      | 1 s                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                        | 7.                          | 183 ms                      |                                | interr          | upt functior |            |  |  |

| 11                      | 1/60 Hz                   | 60 s                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                        | 7.                          | 183 ms                      |                                | stopp           | ed.          |            |  |  |

# 3.7. FLAG REGISTER

# 0Eh, 1Eh – Flag Register

This register holds a variety of status bits. The register may be written at any time to clear any status flag.

| Addresses               | Function      | Bit 7                                                                                              | Bit 6                                                                                                                                                                                                                                                                                                                                                                                                                        | Bit 5                       | Bit 4        | Bit 3             | Bit 2       | Bit 1       | Bit 0   |  |  |

|-------------------------|---------------|----------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|--------------|-------------------|-------------|-------------|---------|--|--|

| 0Eh. 1Eh <sup>(1)</sup> | Flag Register | 0                                                                                                  | 0                                                                                                                                                                                                                                                                                                                                                                                                                            | UF                          | TF           | AF                | EVF         | V2F         | V1F     |  |  |

| UEN, TEN                | Reset         | 0                                                                                                  | 0                                                                                                                                                                                                                                                                                                                                                                                                                            | 0                           | 0            | 0                 | Х           | 1           | 1       |  |  |

| Bit                     | Symbol        | Value                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                              |                             |              | Descriptior       | ı           |             |         |  |  |

| 7:6                     | 0             | 0                                                                                                  | Read only                                                                                                                                                                                                                                                                                                                                                                                                                    | y. Always 0                 |              |                   |             |             |         |  |  |

|                         |               | Periodic                                                                                           | Periodic Time Update Flag (see PERIODIC TIME UPDATE INTERRUPT FUNCTION                                                                                                                                                                                                                                                                                                                                                       |                             |              |                   |             |             |         |  |  |

| 5                       | UF            | 0                                                                                                  | It can be cleared by writing a 0 to the bit.<br>If set to 0 beforehand, indicates the occurrence of a Periodic T                                                                                                                                                                                                                                                                                                             |                             |              |                   |             |             |         |  |  |

|                         |               | 1                                                                                                  | Interrupt                                                                                                                                                                                                                                                                                                                                                                                                                    | event.                      |              |                   |             |             | •       |  |  |

|                         |               | Periodic                                                                                           | Countdown                                                                                                                                                                                                                                                                                                                                                                                                                    | Timer Flag                  |              | ODIC COU<br>TION) | NTDOWN      | TIMER INT   | ERRUF   |  |  |

| 4                       | TF            | 0                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                              | cleared by v                |              |                   |             |             |         |  |  |

|                         |               | 1 If set to 0 beforehand, indicates the occurrence of a Periodic Countdo<br>Timer Interrupt event. |                                                                                                                                                                                                                                                                                                                                                                                                                              |                             |              |                   |             |             | ntdown  |  |  |

|                         |               |                                                                                                    | Ala                                                                                                                                                                                                                                                                                                                                                                                                                          | arm Flag (se                | e ALARM      | INTERRUP          | T FUNCTIO   | ON)         |         |  |  |

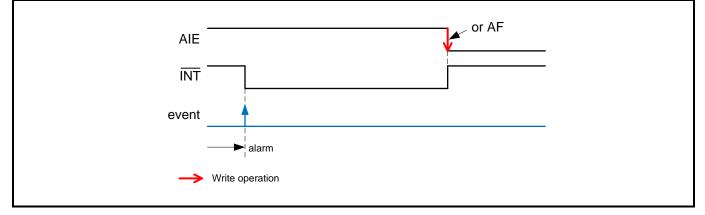

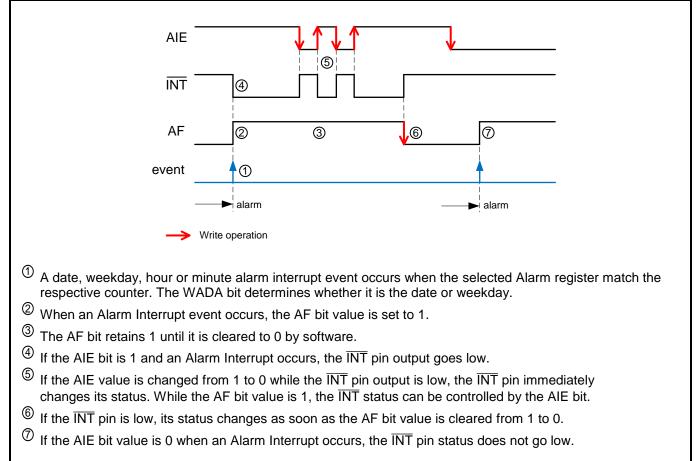

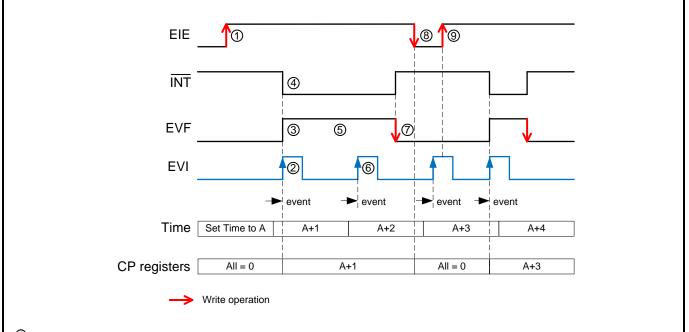

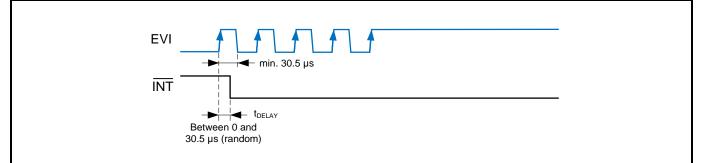

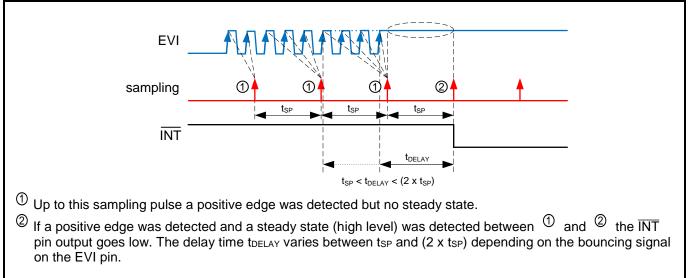

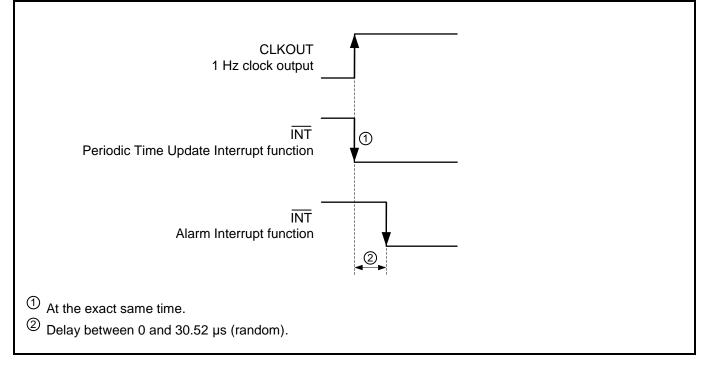

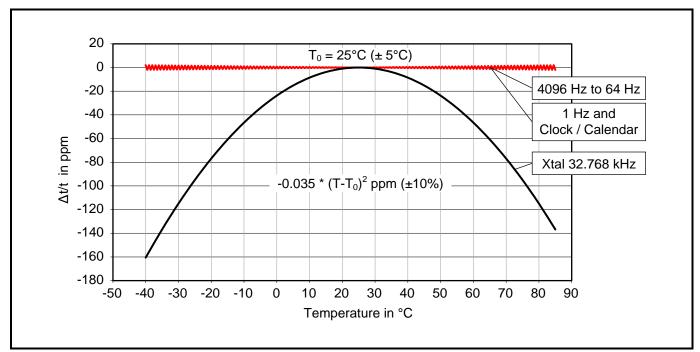

| 3                       | AF            | 0                                                                                                  | It can be                                                                                                                                                                                                                                                                                                                                                                                                                    | cleared by                  | writing a 0  | o the bit.        |             |             |         |  |  |