## **EM6126**

## Digitally programmable 65 and 81 multiplex rate LCD **Controller and Driver**

#### **Features**

- Slim IC for COG, COF and COB technologies

- I<sup>2</sup>C & Serial bus interface

- Internal display data RAM

- 2 digitally programmable multiplex rates :

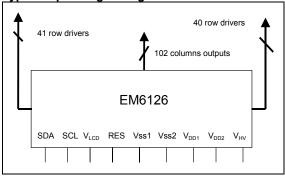

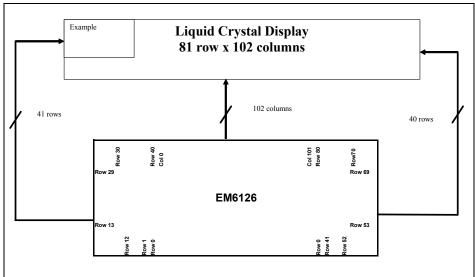

- 81 rows x 102 columns

- 65 rows x 118 columns

- LCD supply voltage internally generated and digitally programmable from 4.5V to 11V

- Low operating current consumption: 140μA (typ)

- No external components needed except one V<sub>LCD</sub> and one VDD capacitor

- On chip

- 4 intermediate bias voltages generation

- Oscillator for LCD refresh (no external components required)

- High noise immunity on inputs

- Row and column drivers mirroring for COG or COF connections flexibility

- Partial display mode with 17 active rows for current consumption reduction

- Sleep mode for a nearly zero current consumption

- Wide V<sub>DD</sub> supply voltage from 2.4V to 3.3V

- Wide temperature range: -40°C to +85°C

#### **Description**

The EM6126 is a bit map controller and driver for full dot matrix monochrome STN LCD displays. The driving capability is 81 rows x 102 columns (10 rows of characters + one row of icons) or 65 rows x 118 columns (8 rows of characters + one row of icons). There is a one to one relation between LCD pixels and bits of the Display Data RAM.

The EM6126 is an extremely low power consumption LCD controller and driver product. The typical current consumption is about 140µA with no external component except the capacitors connected to  $V_{\text{LCD}}$  and VDD. One important feature on EM6126 is the partial display mode, which enables important current consumption reduction. With this function selected, only 17 rows remain active, needed  $V_{\text{LCD}}$  decreases and the commutation frequencies of row and column drivers are also decreased. These three effects of partial display mode reduce drastically current consumption.

## **Typical Applications**

- Mobile phones

- Smart cards

- Portable, battery operated products

- Balances and scales, utility meters

#### **Typical Operating Configuration**

Figure 1

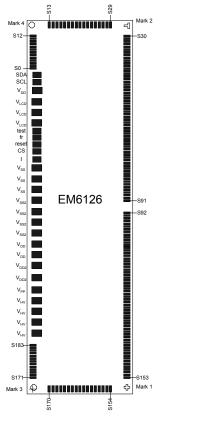

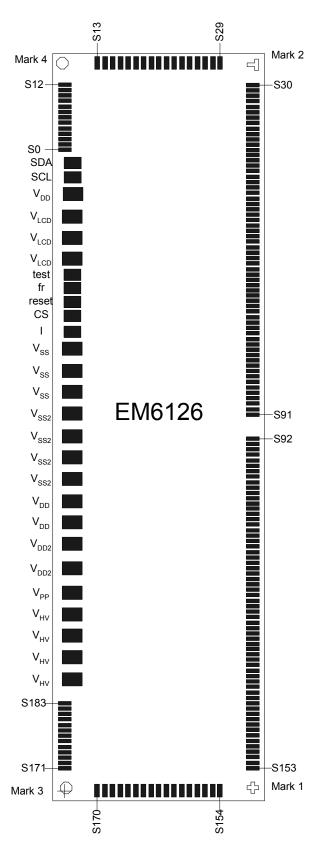

#### Pin Configuration

Figure 2

| Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1                                                                                                                                                                                            |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1                                                                                                                                                                                            |

| Typical Applications Typical Operating Configuration Pin Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | <b>1</b><br>1                                                                                                                                                                                |

| 1 Absolute Maximum Ratings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 4                                                                                                                                                                                            |

| 2 Handling Procedures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4                                                                                                                                                                                            |

| 3 Operating Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4                                                                                                                                                                                            |

| 4 Electrical Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 4                                                                                                                                                                                            |

| 5 Timing Characteristics 5.1 Timing Waveforms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <b>5</b>                                                                                                                                                                                     |

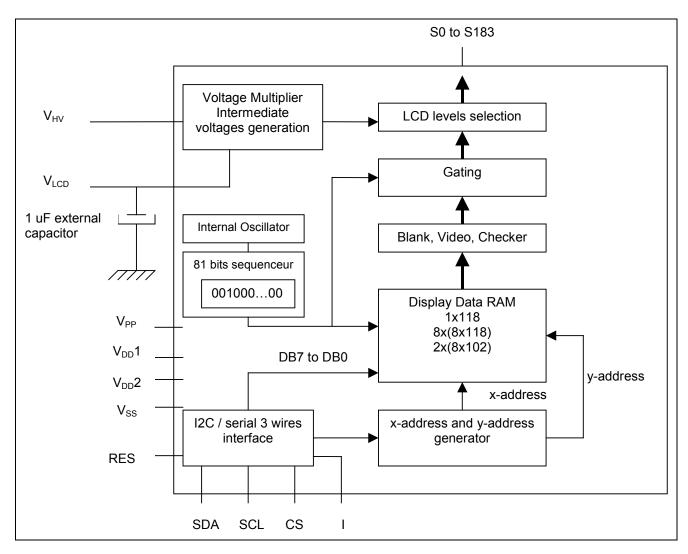

| 6 Block diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 8                                                                                                                                                                                            |

| 7 Pin description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 9                                                                                                                                                                                            |

| 8 Functional description 8.1 Selection of interface type 8.2 Serial interface 8.3 I °C interface 8.3.1 Start and stop conditions 8.3.2 Bit transfer 8.3.3 Acknowledge 8.4 I °C protocol 8.4.1 Write mode 8.4.2 Read Mode (RW = 1) 8.5 Display Data RAM 8.5.1 DDRAM description 8.5.2 DDRAM addressing 8.6 Initialization of EM6126 8.7 Description of instructions 8.7.1 Initialization 0 8.7.1.2 TC[1:0] 8.7.1.3 Inv. Row 8.7.1.4 MX 8.7.1.5 Blank 8.7.1.6 Checker 8.7.1.7 Inv. Video 8.7.2 Initialization 1 8.7.2.1 X[6:0] 8.7.2.2 V 8.7.3 Initialization 2 8.7.3.3 DEC 8.7.3.3 DEC 8.7.3.3 DEC 8.7.3.3 DEC 8.7.4.1 Vide Level[7:0] 8.7.4.1 Initialization 3 8.7.4.1 Vide Level[7:0] 8.7.5 Initialization 4 | 10<br>10<br>10<br>12<br>12<br>12<br>12<br>13<br>13<br>13<br>13<br>13<br>13<br>23<br>23<br>24<br>25<br>25<br>25<br>28<br>28<br>28<br>28<br>28<br>28<br>28<br>28<br>28<br>28<br>28<br>28<br>28 |

# **EM6126**

| 8.7.5.2 Partial Display              | 29 |

|--------------------------------------|----|

| 8.7.5.3 First Row PD[3:0]            | 29 |

| 8.7.5.4 Sleep                        | 29 |

| 8.7.6 Test 0 to 3                    | 29 |

| 8.8 LCD outputs                      | 30 |

| 8.9 LCD refresh frequency            | 31 |

| $8.10~V_{LCD}$ depending on $V_{HV}$ | 31 |

| 8.11 LCD driver waveforms            | 32 |

| 8.11.1 Partial Display               | 35 |

| 9 Typical Application                | 37 |

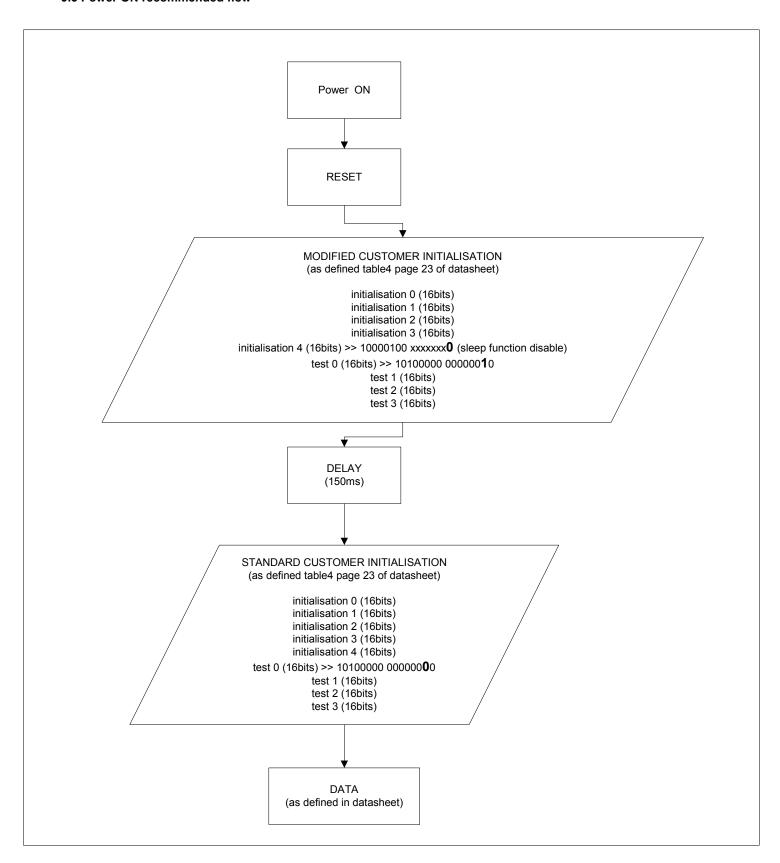

| Power ON recommended flow            | 42 |

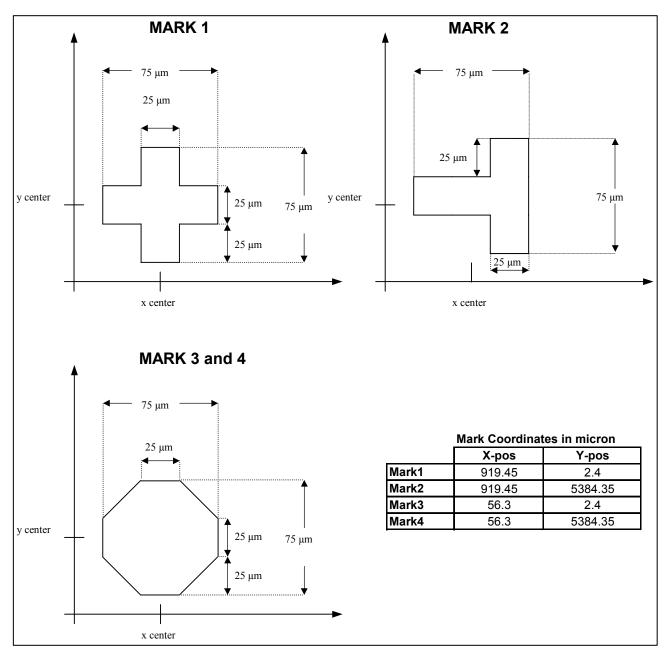

| 10 Pad location                      | 43 |

| 11 Ordering Information              | 46 |

#### 1 Absolute Maximum Ratings

| Parameter                                      | Symbol               | Conditions                  |

|------------------------------------------------|----------------------|-----------------------------|

| Supply voltage range                           | $V_{\mathrm{DD1,2}}$ | -0.3V to +3.6V              |

| Supply voltage range                           | $V_{HV}$             | -0.3V to +3.6V              |

| Supply voltage range                           | $V_{LCD}$            | $V_{HV}$ -0.3V to +12V      |

| All input voltages                             | $V_{LOGIC}$          | $-0.3V$ to $V_{DD1,2}+0.3V$ |

| Voltages at S <sub>0</sub> to S <sub>184</sub> | $V_{\text{DISPLAY}}$ | $-0.3V$ to $V_{LCD} + 0.3V$ |

| Storage temperature range                      | $T_{STO}$            | -65°C to +150 °C            |

| Maximum soldering conditions                   | T <sub>SMAX</sub>    | 250°C×10 s                  |

Stresses above these listed maximum ratings may cause permanent damage to the device. Exposure beyond specified electrical characteristics may affect device reliability or cause malfunction.

#### 2 Handling Procedures

This device has built-in protection against high static voltages or electric fields; however, anti-static precautions should be taken as for any other CMOS component. Unless otherwise specified, proper operation can only occur when all terminal voltages are kept within the supply voltage range.

## **3 Operating Conditions**

| Parameter                             | Symbol             | Min. | Тур. | Max. |          |

|---------------------------------------|--------------------|------|------|------|----------|

| Operating temperature                 | T <sub>A</sub>     | -40  |      | +85  | °C       |

| Logic supply voltage                  | V <sub>DD1,2</sub> | 2.4  | 2.5  | 3.3  | ٧        |

| High voltage generator supply voltage | V <sub>HV</sub>    | 2.4  | 2.5  | 3.3  | <b>V</b> |

| LCD supply voltage                    | V <sub>LCD</sub>   | 4.5  | 8    | 11   | V        |

#### **4 Electrical Characteristics**

$V_{SS1,2}$  = 0V,  $V_{DD1}$  =  $V_{DD2}$  = 2.4V,  $V_{HV}$  = 2.4V, unless otherwise specified.  $T_A$  = -40°C to +85 °C unless otherwise specified. Minimum required capacitor: 1µF on  $V_{LCD}$ , 100nF on  $V_{DD1,2}$  and  $V_{HV}$ .

| Parameter                                                                           | Symbol                         | Test conditions                     | Min.          | Тур. | Max.          | Units    |

|-------------------------------------------------------------------------------------|--------------------------------|-------------------------------------|---------------|------|---------------|----------|

| Supply Current                                                                      |                                |                                     |               |      |               |          |

| Sleep mode                                                                          | I <sub>DD</sub>                | T <sub>A</sub> = 25°C, Sleep = 1    |               | 100  |               | nA       |

| Sleep mode                                                                          | I <sub>HV</sub>                | T <sub>A</sub> = 25°C, Sleep = 1    |               | 8.0  |               | μА       |

| Normal LCD refresh mode                                                             | I <sub>DD</sub>                | $T_A = 25^{\circ}C$ , (note 1)      |               | 17   | 22            | μА       |

| Normal LCD refresh mode                                                             | I <sub>HV</sub>                | $T_A = 25^{\circ}C$ , (note 2)      |               | 124  | 180           | μΑ       |

| Partial LCD refresh mode                                                            | I <sub>HV</sub>                | T <sub>A</sub> = 25°C, (note 3)     |               | 50   | 90            | μА       |

| Control Input Signals                                                               |                                |                                     |               |      |               |          |

| Input leakage                                                                       | I <sub>IN</sub>                | $V_i = V_{ss1} \text{ or } V_{DD1}$ | -1            |      | 1             | μА       |

| Low level input voltage                                                             | V <sub>IL</sub>                |                                     |               |      | $0.3xV_{DD1}$ | V        |

| High level input voltage                                                            | V <sub>IH</sub>                |                                     | $0.7xV_{DD1}$ |      |               | V        |

| Low Level Output Current SDA                                                        | I <sub>OL_SDA</sub>            | V <sub>OL_SDA</sub> = 0.4V          |               | 1.6  |               | mA       |

| LCD Outputs                                                                         |                                |                                     |               |      |               |          |

| Internally generated LCD supply voltage                                             | $T_A = 25^{\circ}C, V_{LCD}$   | 00101011b (Hex: 2B)                 |               | 4.53 |               | V        |

|                                                                                     | $T_A = 25^{\circ}C, V_{LCD}$ 1 | 10001110b (Hex: 8E)                 |               | 8.02 |               | V        |

| V <sub>LCD</sub> step between 2<br>consecutive programmed<br>V <sub>LCD</sub> Level | V <sub>LCD</sub> step          |                                     |               | 35.2 |               | mV       |

| V bias tolerance                                                                    | V bias tol.                    | (note 4)                            | -80           |      | 80            | mV       |

| Typical load                                                                        | C <sub>LOAD</sub>              |                                     |               | 1.2  |               | pF/pixel |

- Note 1: Measured on  $V_{DD1}$  +  $V_{DD2}$ , all outputs open, SDA and SCL at  $V_{SS}$ , RES at  $V_{DD1}$ , multiplex rate 81, x5 voltage multiplier,  $V_{LCD}$  = 10001110b, DDRAM loaded with checker pattern

- Note 2: Measured on V<sub>HV</sub>, same conditions as (note 1).

- Note 3: Measured on  $V_{HV}$ , all outputs open, SDA and SCL at  $V_{SS}$ , RES at  $V_{DD1}$ , partial display mode,  $\times 2$  voltage multiplier,  $V_{LCD}$  = 00101011b, DDRAM loaded with checker pattern.

- Note 4:  $V_1$ ,  $V_2$ ,  $V_3$  and  $V_4$  bias levels measured with  $V_{LCD}$  = 7V, on 1 LCD row driver output and 1 LCD column driver output, multiplex rate 81,  $T_A$  = 25 °C, load =  $\pm 10 \mu A$ ,  $I_{load}$  =  $10 \mu A$  to  $V_{SS}$  or  $V_{LCD}$  V bias\_tol is:  $\frac{1}{2}(Vbias_{-10\mu A} + Vbias_{-10\mu A}) Vbias_{theor}$

(Vbias\_theor: see § 8.8; e.g. for V1: 0.9xV<sub>LCD</sub> at Mux=81)

## **5 Timing Characteristics**

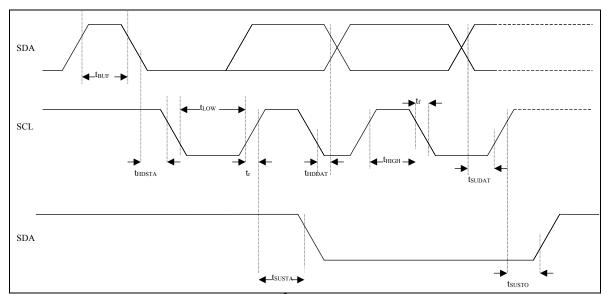

$V_{SS1,2}$  = 0V,  $V_{DD1}$ =  $V_{DD2}$  = 2.4V,  $V_{HV}$  = 2.4V,  $T_A$  = -40°C to +85 °C unless otherwise specified.

| Parameter                                                       | Symbol             | Test conditions | Min. | Тур.        | Max. | Units |

|-----------------------------------------------------------------|--------------------|-----------------|------|-------------|------|-------|

| Internal frame frequency for LCD refresh                        | f <sub>FR</sub>    | (note 1)        |      | 75 x<br>mux |      | Hz    |

| Minimum reset pulse width                                       | t <sub>RW</sub>    |                 | 1    |             |      | us    |

| I2C timing characteristics                                      |                    |                 |      | •           |      |       |

| SCL frequency                                                   | f <sub>I2C</sub>   |                 |      |             | 1600 | kHz   |

| SCL low period                                                  | $t_{LOW}$          |                 | 350  |             |      | ns    |

| SCL high period                                                 | t <sub>HIGH</sub>  |                 | 100  |             |      | ns    |

| SDA setup time                                                  | t <sub>SUDAT</sub> |                 | 10   |             |      | ns    |

| SDA hold time                                                   | t <sub>HDDAT</sub> |                 | 20   |             |      | ns    |

| SCL and SDA rise time                                           | t <sub>R</sub>     |                 |      |             | 200  | ns    |

| SCL and SDA fall time                                           | t <sub>F</sub>     |                 |      |             | 200  | ns    |

| Setup time for a repeated start condition                       | t <sub>SUSTA</sub> |                 | 20   |             |      | ns    |

| Hold time for a start condition                                 | t <sub>HDSTA</sub> |                 | 20   |             |      | ns    |

| Setup time for a stop condition                                 | tsusто             |                 | 20   |             |      | ns    |

| Spike width on SCL and SDA                                      | t <sub>SW</sub>    |                 |      |             | 10   | ns    |

| Time before a new transmission can start                        | t <sub>BUF</sub>   |                 | 100  |             |      | ns    |

| Capacitive bus line load                                        | C <sub>b</sub>     |                 |      |             | 400  | pF    |

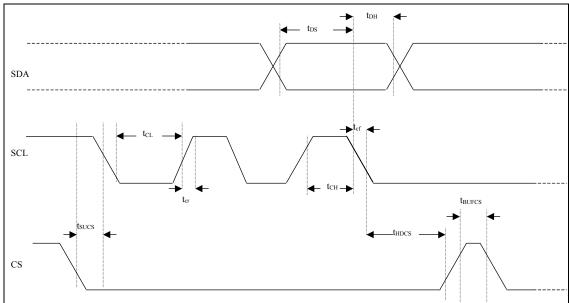

| Serial bus timing characteristics                               | ·                  | 1               | 1    | 1           | 1    |       |

| SCL frequency                                                   | f <sub>SER</sub>   |                 |      |             | 4    | MHz   |

| SCL low period                                                  | t <sub>CL</sub>    |                 | 80   |             |      | ns    |

| SCL high period                                                 | tсн                |                 | 130  |             |      | ns    |

| SDA setup time                                                  | t <sub>DS</sub>    |                 | 20   |             |      | ns    |

| SDA hold time                                                   | $t_{DH}$           |                 | 70   |             |      | ns    |

| SCL rise time                                                   | t <sub>CR</sub>    |                 |      |             | 200  | ns    |

| SCL fall time                                                   | t <sub>CF</sub>    |                 |      |             | 200  | ns    |

| CS setup time                                                   | t <sub>sucs</sub>  |                 | 10   |             |      | ns    |

| CS hold time                                                    | t <sub>HDCS</sub>  |                 | 130  |             |      | ns    |

| Time before a new transmission can start, CS minimum high time. | t <sub>BUFCS</sub> |                 | 70   |             |      | ns    |

Note 1: Measured on pad FR.

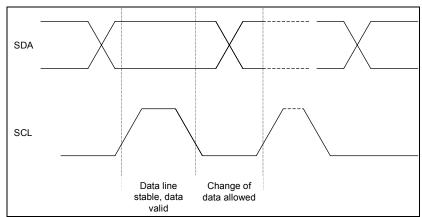

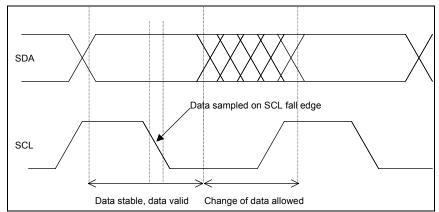

## **5.1 Timing Waveforms**

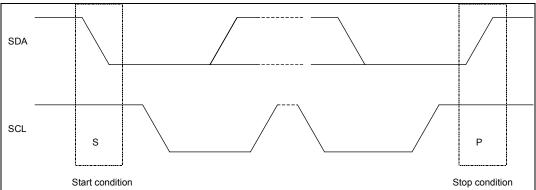

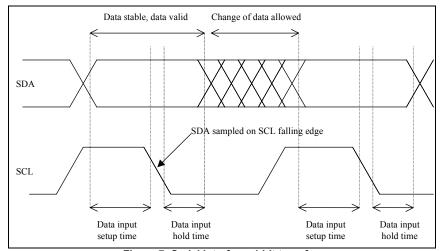

Figure 3: I<sup>2</sup>C 1 bit transfer

Figure 4: I<sup>2</sup>C start and stop conditions

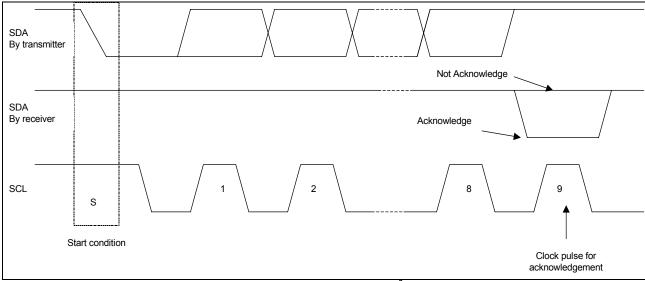

Figure 5: Acknowledgement on the I<sup>2</sup>C bus

Figure 6: I<sup>2</sup>C timing diagram.

Figure 7: Serial interface, 1 bit transfer.

Figure 8: Serial interface timing diagram.

## 6 Block diagram

Figure 9: Block diagram.

#### 7 Pin description

| Symbol                                                                         | Pad Type              | Description                                                                                                            |  |  |  |  |

|--------------------------------------------------------------------------------|-----------------------|------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| S <sub>0</sub> to S <sub>183</sub>                                             | Output                | LCD driver outputs                                                                                                     |  |  |  |  |

| $S_0$ to $S_{32}$ and $S_{151}$ to $S_{183}$                                   | Output                | LCD row driver outputs $S_0 = S_{183}$                                                                                 |  |  |  |  |

| S <sub>33</sub> to S <sub>40</sub><br>and S <sub>143</sub> to S <sub>150</sub> | Output                | LCD row driver outputs when multiplex rate 81 is selected LCD column driver outputs when multiplex rate 65 is selected |  |  |  |  |

| S <sub>41</sub> to S <sub>142</sub>                                            | Output                | LCD column driver outputs                                                                                              |  |  |  |  |

| $V_{HV}$                                                                       | Positive power supply | Supply voltage for internal voltage multiplier                                                                         |  |  |  |  |

| $V_{DD1,2}$                                                                    | Positive power supply | Supply voltage for logical and analog parts                                                                            |  |  |  |  |

| $V_{PP}$                                                                       | Positive power supply | Supply voltage for OTP                                                                                                 |  |  |  |  |

| V <sub>SS1,2</sub>                                                             | Ground power supply   | Ground power supply                                                                                                    |  |  |  |  |

|                                                                                | Input                 | Interface protocol selection input                                                                                     |  |  |  |  |

| RES                                                                            | Input                 | External reset input, active low                                                                                       |  |  |  |  |

| CS                                                                             | Input                 | Chip select input                                                                                                      |  |  |  |  |

| FR                                                                             | Input/output          | Frame frequency input/output                                                                                           |  |  |  |  |

| TEST                                                                           | Input/output          | Test                                                                                                                   |  |  |  |  |

| SDA                                                                            | Input/output          | Serial data input                                                                                                      |  |  |  |  |

| SCL                                                                            | Input                 | Serial clock                                                                                                           |  |  |  |  |

| $V_{LCD}$                                                                      | Positive power supply | LCD supply voltage                                                                                                     |  |  |  |  |

Table 1: Pin description

S0 to S183: Connected to LCD electrodes, it should be left open if not used. S0 and S183 are internally connected

together.

V<sub>HV</sub>: Supply voltage for internal voltage multiplier, it could be a different voltage value than for V<sub>DD1,2</sub>.

V<sub>DD1,2</sub> V<sub>PP</sub>: Logic and analog power supplies. V<sub>DD1</sub>, V<sub>DD2</sub> and V<sub>PP</sub> are not connected inside EM6126but have to be

connected outside to the same potential. For chip on glass application, it is advised to keep V<sub>DD1</sub> and V<sub>DD2</sub>

separated until their connection to 1  $\mu\text{F}$  capacitor.

V<sub>SS1,2</sub>: Ground supply for logic and high voltage generator. V<sub>SS1</sub> is connected to substrate. Same precautions

than for  $V_{DD1,2}$  should be taken to connect these pads.

I: Selects the chosen interface protocol. For chip on glass applications, it can be directly connected to V<sub>SS1</sub>

or  $V_{DD1}$  on glass.

**RES:** External reset, a reset cycle must be applied at power on (reset at low level when power on).

Note that the outputs  $S_0 = S_{183}$  are at VLCD level when reset is active. If this static state is applied during

long time the LCD could be damaged.

CS: Active low chip select, when serial interface is used it enables data transfer. If  $l^2C$  is used, it must be

connected at V<sub>SS1</sub> or V<sub>DD1</sub> pads.

FR: Outputs LCD refresh frame frequency, used for test. It must be left open.

**TEST:** Test pad, it must be left open.

**SDA:** Serial data input used for I<sup>2</sup>C interface as for 3 wires serial interface.

SCL: Serial clock input used to latch SDA for I<sup>2</sup>C interface as for 3 wires serial interface.

V<sub>LCD</sub>: LCD voltage supply (generation of LCD waveforms applied to S0 to S183). It is normally internally

generated from  $V_{HV}$  supply voltage. 1  $\mu F$  capacitor is required between  $V_{LCD}$  and  $V_{SS}$ . A forward biased

diode is connected between  $V_{\text{HV}}$  and  $V_{\text{LCD}}$ , therefore  $V_{\text{LCD}}$  must be programmed higher than  $V_{\text{HV}}$ .

External power supply is also possible; in this configuration,  $V_{\text{LCD}}$  must be programmed at its lowest value

and  $V_{HV}$  connected to  $V_{SS2}$ .

#### 8 Functional description

#### 8.1 Selection of interface type

There are two different serial interfaces available on EM6126. Selection depends on logical value applied on input I.

- If I = 0, serial interface is selected: 3 wires with Chip Select CS, Serial Clock SCL and Serial Data SDA.

- If I = 1, I<sup>2</sup>C protocol is selected: 2 wires with Serial Clock SCL and Serial Data SDA. CS must be connected to V<sub>SS</sub> or V<sub>DD1</sub>.

| I | Interface                |  |  |  |  |  |  |

|---|--------------------------|--|--|--|--|--|--|

| 0 | 3 wires serial interface |  |  |  |  |  |  |

| 1 | I <sup>2</sup> C         |  |  |  |  |  |  |

Table 2: Interface selection

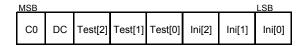

#### 8.2 Serial interface

The serial interface consists of 3 wires: Chip Select CS, Serial Clock SCL and Serial Data SDA. The information is exchanged byte-wide and is shifted serially in the LCD driver at SCL falling edge.

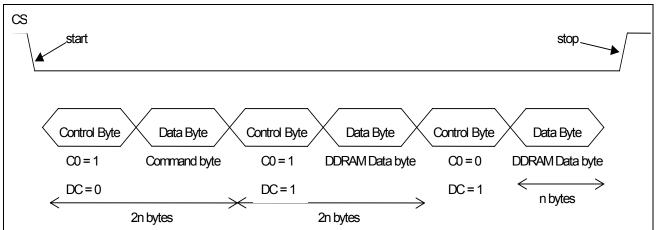

Figure 10: Serial interface, 1 bit transfer

Transfer data direction is from microcontroller to EM6126. When CS is activated at low level, the communication is enabled and CS must stay low for the rest of the transmission. Data transfer begins with one control byte. This control byte is transfered MSB first; it consists in:

C<sub>0</sub> is the continuation bit:

- If  $C_0 = 1$ , the control byte is followed by 1 data byte only, the next byte is a new control byte.

- If C<sub>0</sub> = 0, all the following bytes are data bytes until data transfer is stopped.

DC selects data bytes or command bytes to be sent after the control byte:

- If DC = 1, the following data byte(s) is (are) written into the Display Data RAM. First data byte is stored at the address specified by the x-address and y-address pointers. Data pointers are automatically updated for each byte written in the DDRAM (see DDRAM description).

- IF DC = 0, the following data byte is a command byte. It enables initialization of functions (multiplex rate, number of voltage multiplier stages, V<sub>LCD</sub> programming, partial display settings…).

Bytes ini2, ini1 and ini0 select the initialization register which will be set by the following command byte (see Table 4: EM6126 instructions).

Figure 11: serial interface protocol

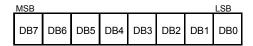

Data byte is transfered with MSB bit first, LSB bit last:

If CS goes high during a byte transfer, this byte is invalid, but all previously transmitted data are valid. While CS is high, the serial interface is kept in reset and data transfer is disabled. To prevent transmission errors, CS should be at high level when transfer is stopped.

#### 8.3 I<sup>2</sup>C interface

The EM6126 can be interfaced with a slave  $I^2C$  protocol (see description I2C protocol). The  $I^2C$  bus consists in 2 wires: SCL (Serial Clock Line) and SDA (Serial Data Line). Both lines must be connected to  $V_{DD1,2}$  via pull up resistors. EM6126 pad SCL is input, pad SDA is bi-directional with open drain NMOS driver. EM6126 supports initialization and RAM write and status read access.

#### 8.3.1 Start and stop conditions

Data transfer begins by a falling edge on SDA when SCL is at high level, this is the start condition (S), initiated by the I<sup>2</sup>C bus master. It is stopped with a rising edge on SDA when SCL isat high level, this is the stop condition (P) (see Figure 4: I2C start and stop conditions).

#### 8.3.2 Bit transfer

One data bit is transfered by each SCL pulse. The data on the SDA line must remain stable during the high period of SCL pulses, as any changes at this time would be interpreted as start or stop conditions. Data is always transfered with MSB first.

#### 8.3.3 Acknowledge

After a start condition, data bits are transfered to EM6126. Each byte is followed by an acknowledge bit: the transmitter lets the SDA line at high level (by pull up resistor) and generates an SCL pulse; if transfer concerns the EM6126 slave receiver and has performed correctly, EM6126 generates a low SDA level (NMOS activated). SDA remains stable during the high period of the acknowledge related SCL pulse. After acknowledge, EM6126 lets SDA line free, enabling the transmitter to continue transfer or to generate a stop condition.

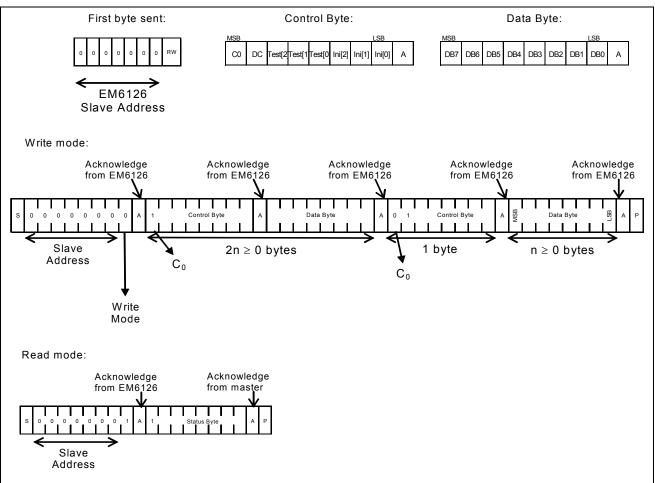

#### 8.4 I<sup>2</sup>C protocol

The FM6126 has the slave address coded on 7 bits: 0000000.

After a start condition, the slave address + RW bit must be sent first. If the slave address does not match with the EM6126 one, there is no acknowledge from LCD driver and the following data transfer will not affect the EM6126.

If the slave address corresponds to EM6126 slave address, it will acknowledge (pull SDA down to logical low level) and data transfer is enabled.

The 8th bit RW sets the chip in write mode or read status mode, it is read for data transfer.

#### 8.4.1 Write mode

If RW = 0, data are written into EM6126 by the microcontroller.

Data transfer bytes can be either control bytes or data bytes. Data transfer always begins with a control byte (described in fig.12). It sets bits C0, DC, ini2, ini1 and ini0

C0 is the continuation bit:

- If  $C_0 = 1$ , the control byte is followed by 1 data byte only, the next byte is a new control byte.

- If  $C_0 = 0$ , all the following bytes are data bytes until data transfer is stopped.

DC selects data bytes or command bytes to be sent after the control byte:

- If DC = 1, the following data byte(s) is (are) written into the Display Data RAM. First data byte is stored at the address specified by the x-address and y-address pointers. Data pointers are automatically updated for each byte written in the DDRAM (see DDRAM description).

- IF DC = 0, the following data byte is a command byte. It enables initialization of functions (multiplex rate, number of voltage multiplier stages, V<sub>LCD</sub> programming, partial display settings...).

Bytes ini2, ini1 and ini0 select the initialization register to be set by the following command byte (see Table 4: EM6126 instructions).

#### 8.4.2 Read Mode (RW = 1)

EM6126 will output one status byte after slave address. This status byte consists in 8 initialization bits previously set by command bytes or the reset cycle (see Table 4: EM6126 instructions).

Figure 12: I<sup>2</sup>C protocol description

## 8.5 Display Data RAM

The EM6126 contains a RAM, which stores the display data; there is a one to one correspondence between the bit stored in the RAM and one LCD pixel.

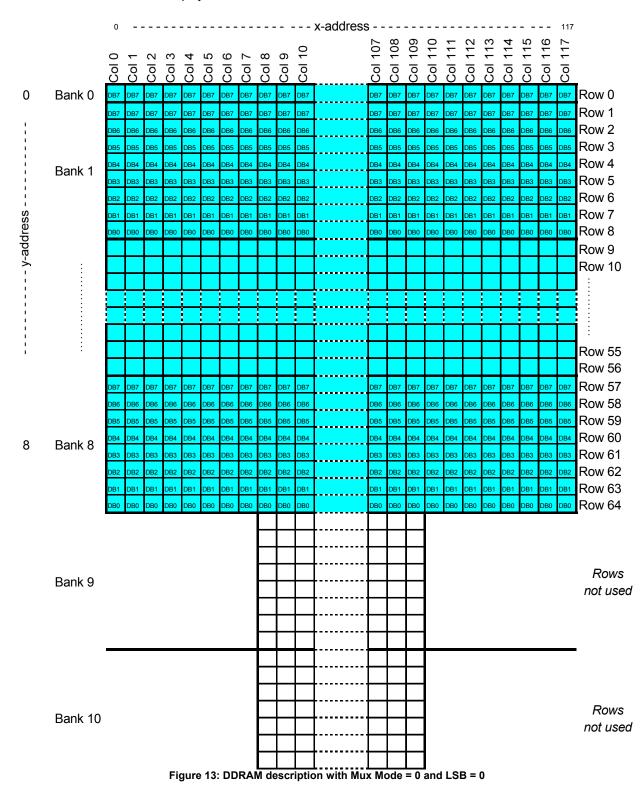

#### 8.5.1 DDRAM description

DDRAM consists in:

- 1 bank of 118 bits (row 0)

- 8 banks of 118 bytes (rows 1 to 64)

- 2 banks of 102 bytes (rows 65 to 80)

DDRAM is read row by row for display refresh. Each row corresponds to one row output pad, which is activated when the corresponding row in the DDRAM is read.

DDRAM is accessed via the serial interface. Bytes are stored at the column specified by x-address pointer and the bank specified by y-address pointer. These pointers are set by the corresponding instruction "Initialization 1" and "Initialization 2" and are automatically incremented or decrement after each byte written in the DDRAM (see

DDRAM addressing and Table 5: Internal functions after reset.)

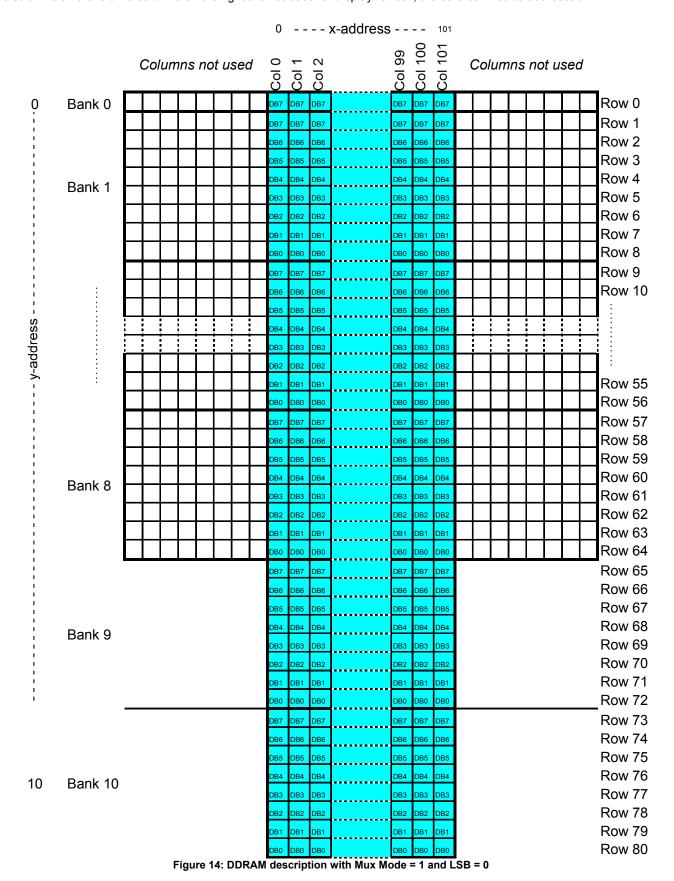

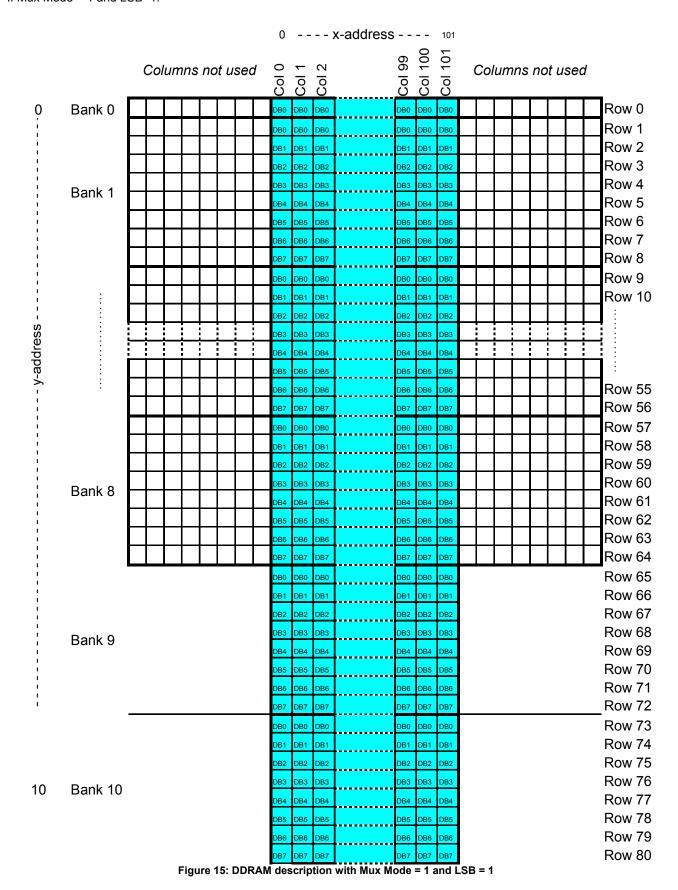

For bank 0 only data byte 7 (DB7) is stored in row 0, DB6 to DB0 are not used. For bank 1 to 10 (y-address = 1 to 10), DBX is stored at row ((8 x y-address)-X).

If Mux Mode = 0, the DDRAM provides a 65 rows and 118 columns matrix. Bank 9 and 10 are not used for display refresh, the cells can not be addressed.

If Mux Mode = 1, the DDRAM provides a 81 rows and 102 columns matrix. 8 columns on the left + 8 columns on the right are not used for display refresh, the cells can not be addressed.

If Mux Mode = 1 and LSB=1.

#### 8.5.2 DDRAM addressing

The x-address and the y-address pointers are used to address RAM cells. They are set by instructions "initialization 1" and "initialization 2". As EM6126 offers 2 digitally programmable multiplex rates, number of row drivers and number of column drivers are not fixed.

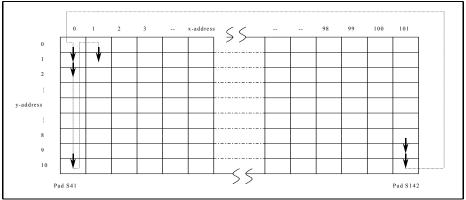

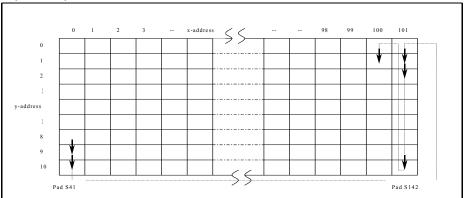

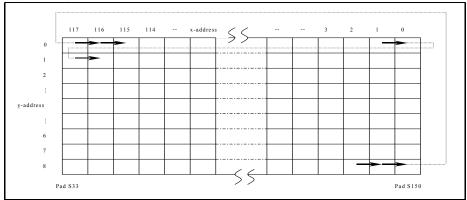

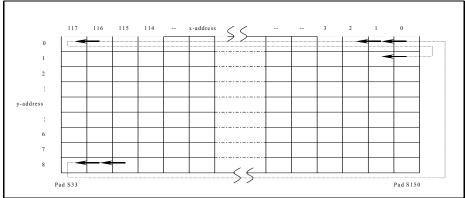

As DDRAM is an image of LCD display, address ranges also depend on multiplex rate (Mux Mode):

If Mux Mode = 0: 0 ≤ x-address ≤ 117 0 ≤ y-address ≤ 8

If Mux Mode = 1: 0 ≤ x-address ≤ 101 0 ≤ y-address ≤ 10

Addresses outside these ranges are not allowed.

There are three functions that affects the pointers: DEC, V and MX. They are set by instructions "initialization 1" and "initialization 2" (see Table 4: EM6126 instructions).

- Instruction DEC increment or decrement x-address:

- If DEC = 0, x-address increments after each byte written into the RAM. After the last x-address, x-address is reset to 0 and y-address increments.

- If DEC = 1, x-address decrements after each byte written to the RAM. After x-address=0, x-address is set back to the highest x-address for the selected mux mode and y-address increments.

DEC allows writing easily to the RAM in two ways, right and left.

- Instruction V horizontal or vertical mode addressing:

- If V = 0 (horizontal mode addressing), x-address increments or decrements after each byte written into the RAM. After the last x-address, x-address is reset to 0 or to the highest x-address, and y-address increments.

- If V = 1 (vertical mode addressing), y-address increments after each byte written to the RAM. After the last y-address, y-address is set back to 0 and x-address increments or decrements.

- Instruction MX mirrored the DDRAM columns:

- If MX = 0, x-address 0000000b corresponds to DDRAM column 0.

- If MX = 1, x-address 0000000b corresponds to DDRAM column 117 or 101.

The table below represents the next address selected after pointers are in the last allowed address:

| Mux  | DEC | Last allowe | ed address | Next address |           |  |  |

|------|-----|-------------|------------|--------------|-----------|--|--|

| Mode |     | x-address   | y-address  | x-address    | y-address |  |  |

| 0    | 0   | 117         | 8          | 0            | 0         |  |  |

| 1    | 0   | 101         | 10         | 0            | 0         |  |  |

| 0    | 1   | 0           | 8          | 117          | 0         |  |  |

| 1    | 1   | 0           | 10         | 101          | 0         |  |  |

Table 3

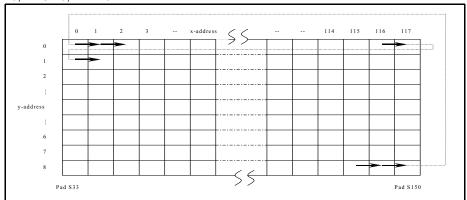

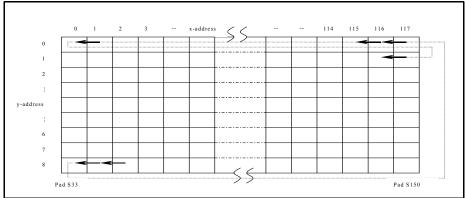

The following tables represent the way that the pointers x-address and y-address are working according to the setting of the instructions Mux Mode, V, MX and DEC.

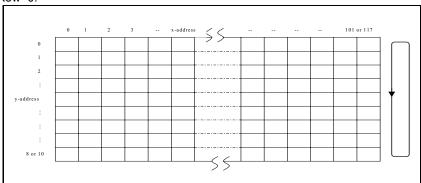

Mux Mode = 0, V = 0, DEC =0, MX = 0:

Figure 16

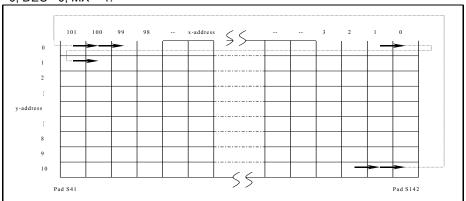

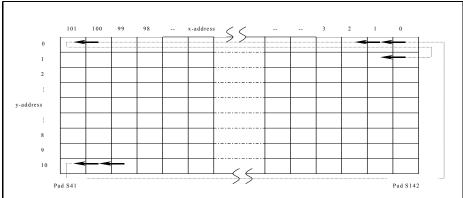

Mux Mode = 0, V = 0, DEC = 1, MX = 0:

Figure 17

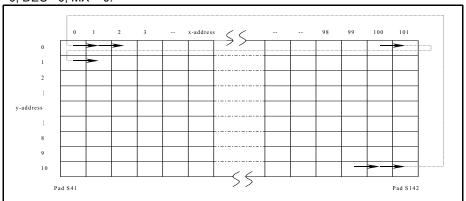

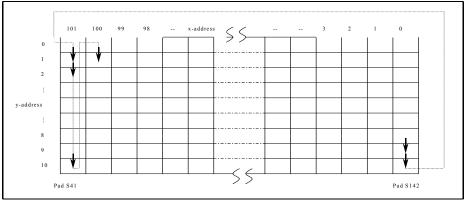

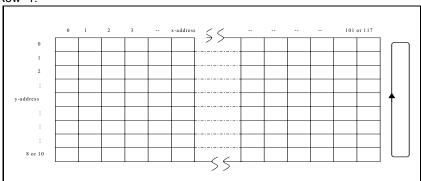

Mux Mode = 1, V = 0, DEC =0, MX = 0:

Figure 18

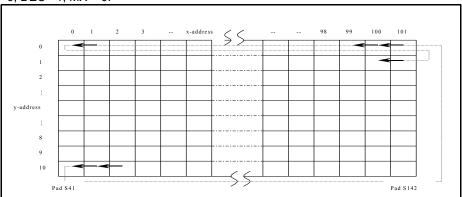

Mux Mode = 1, V = 0, DEC =1, MX = 0:

Figure 19

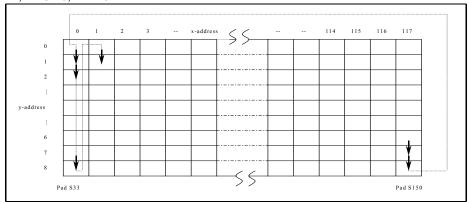

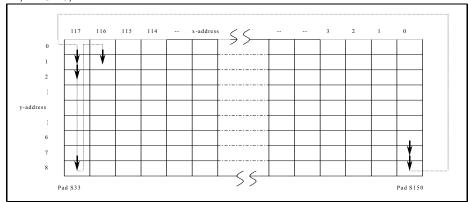

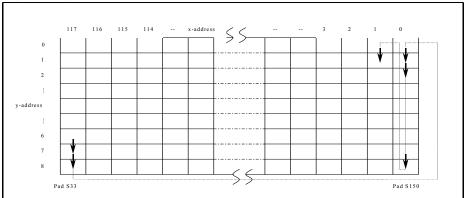

Mux Mode = 0, V = 1, DEC =0,MX = 0:

Figure 20

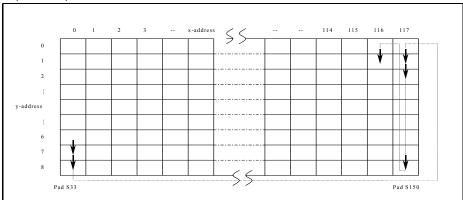

Mux Mode = 0, V = 1, DEC =1,MX = 0:

Figure 21

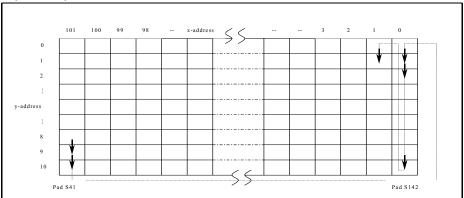

Mux Mode = 1, V = 1, DEC =0, MX = 0:

Figure 22

Mux Mode = 1, V = 1, DEC =1, MX = 0:

Figure 23

Mux Mode = 0, V = 0, DEC =0, MX = 1:

Figure 24

Mux Mode = 0, V = 0, DEC =1, MX = 1:

Figure 25

Mux Mode = 1, V = 0, DEC =0, MX = 1:

Figure 26

Mux Mode = 1, V = 0, DEC =1, MX = 1:

Figure 27

Mux Mode = 0, V = 1, DEC =0,MX = 1:

Figure 28

Mux Mode = 0, V = 1, DEC =1,MX = 1:

Figure 29

Mux Mode = 1, V = 1, DEC =0, MX = 1:

Figure 30

Mux Mode = 1, V = 1, DEC =1, MX = 1:

Figure 31

#### 8.6 Initialization of EM6126

Data loaded into EM6126 can be divided in two parts:

- The bits stored in the DDRAM, which are corresponding to LCD pixels.

- The command bits, which are used to set functions of the LCD controller.

The way of addressing these bits is described in table below:

|                |                               |    |     |    | Со      | ntro    | ol B    | yte    |        |        |                      |                      |                      | Contro                    | ol Byte                   | l                         |                           |                      |                                                                                                    |

|----------------|-------------------------------|----|-----|----|---------|---------|---------|--------|--------|--------|----------------------|----------------------|----------------------|---------------------------|---------------------------|---------------------------|---------------------------|----------------------|----------------------------------------------------------------------------------------------------|

|                | Instruction                   | RW | 00  | DC | test[2] | test[1] | test[0] | ini[2] | ini[1] | [0]iui | DB7                  | DB6                  | DB5                  | DB4                       | DB3                       | DB2                       | DB1                       | DB0                  | Description                                                                                        |

| ø              | Initialization 0              | 0  | 1   | 0  | 0       | 0       | 0       | 0      | 0      | 0      | Mux<br>Mode          | TC<br>[1]            | TC<br>[0]            | Inv.<br>Row               | MX                        | Blank                     | Checker                   | Inv.<br>Video        | Set functions                                                                                      |

| of functions   | Initialization 1              | 0  | 1   | 0  | 0       | 0       | 0       | 0      | 0      | 1      | X[6]                 | X[5]                 | X[4]                 | X[3]                      | X[2]                      | X[1]                      | X[0]                      | ٧                    | Set column adress for DDRAM write<br>access and vertical/horizontal<br>addressing                  |

|                | Initialization 2              | 0  | 1   | 0  | 0       | 0       | 0       | 0      | 1      | 0      | Y[3]                 | Y[2]                 | Y[1]                 | Y[0]                      | 0                         | Vlcd<br>Dischg            | DEC                       | LSB                  | Set bank adress for DDRAM write<br>access, increment /decrement<br>pointer and LSB/MSB mode        |

| Initialization | Initialization 3              | 0  | 1   | 0  | 0       | 0       | 0       | 0      | 1      | 1      | VIcd<br>Level<br>[7] | VIcd<br>Level<br>[6] | VIcd<br>Level<br>[5] | VIcd<br>Level<br>[4]      | Vlcd<br>Level<br>[3]      | Vlcd<br>Level<br>[2]      | Vlcd<br>Level<br>[1]      | Vlcd<br>Level<br>[0] | Programming the internally generated LCD voltage supply $V_{\text{LCD}}$                           |

| Initia         | Initialization 4              | 0  | 1   | 0  | 0       | 0       | 0       | 1      | 0      | 0      | Mult<br>[1]          | Mult<br>[0]          | Partial<br>Display   | First<br>Row<br>PD<br>[3] | First<br>Row<br>PD<br>[2] | First<br>Row<br>PD<br>[1] | First<br>Row<br>PD<br>[0] | Sleep                | Number of voltage multiplier stages<br>Partial display parameters<br>Sleep mode                    |

|                | Test 0                        | 0  | 1   | 0  | 1       | 0       | 0       | 0      | 0      | 0      | 0                    | 0                    | 0                    | 0                         | 0                         | 0                         | 0                         | 0                    | Byte test 0, all bits must be set to 0                                                             |

| Test           | Test 1                        | 0  | 1   | 0  | 1       | 0       | 1       | 0      | 0      | 0      | 0                    | 0                    | 0                    | 0                         | 0                         | 0                         | 0                         | 0                    | Byte test 1, all bits must be set to 0                                                             |

| ₽              | Test 2                        | 0  | 1   | 0  | 1       | 1       | 0       | 0      | 0      | 0      | 0                    | 0                    | 0                    | 0                         | 0                         | 0                         | 0                         | 0                    | Byte test 2, all bits must be set to 0                                                             |

|                | Test 3                        | 0  | 1   | 0  | 1       | 1       | 1       | 0      | 0      | 0      | 0                    | 0                    | 0                    | 0                         | 0                         | 0                         | 0                         | 0                    | Byte test 3, all bits must be set to 0                                                             |

| Write<br>DDRAM | Write 1 byte in DDRAM         | 0  | 1/0 | 1  | 0       | 0       | 0       | 0      | 0      | 0      | DB7                  | DB6                  | DB5                  | DB4                       | DB3                       | DB2                       | DB1                       | DB0                  | Write data byte to the<br>Display Data Ram                                                         |

| Read<br>Status | Read 1 byte in initialization | 1  | -   | -  | -       | -       | -       | 1      | -      | -      | Mux<br>Mode          | TC<br>[1]            | TC<br>[0]            | Inv.<br>Row               | MX                        | Blank                     | Checker                   | Inv.<br>Video        | Read Status Byte from EM6126<br>Status Byte = initialization 0 using I <sup>2</sup> C<br>interface |

Table 4: EM6126 instructions

Instruction bits from Table 4, active levels and state after reset:

| Bits                        | 0                                   | 1                                   | State after reset |

|-----------------------------|-------------------------------------|-------------------------------------|-------------------|

| Mux Mode                    | Multiplex rate 65                   | Multiplex rate 81                   | 0                 |

| TC[1:0]                     | Select V <sub>LCD</sub> Temp        | erature Coefficient                 | 00b               |

| Inv. Row.                   | Normal row drivers                  | Mirrored row drivers                | 0                 |

| MX                          | Normal column drivers               | Mirrored column drivers             | 0                 |

| Blank                       | Display DDRAM content               | LCD blanked (all OFF)               | 0                 |

| Checker                     | Display DDRAM content               | LCD = checker board                 | 0                 |

| Inv. Video                  | LCD = DDRAM                         | LCD = NOT (DDRAM)                   | 0                 |

| X[6:0]                      | x-address pointer. Selects DD       | 000000b                             |                   |

| V                           | Horizontal addressing               | 0                                   |                   |

| Y[3:0]                      | y-address pointer. Selects D        | 0000b                               |                   |

| V <sub>LCD</sub> Dischg     | Normal Mode                         | Discharge Capacitor                 | 0b                |

| DEC                         | x-address pointer incremented       | x-address pointer decrement         | 0                 |

| LSB                         | DB7 copied to the higher row of the | DB0 copied to the higher row of the | 0                 |

|                             | selected bank                       | selected bank                       |                   |

| V <sub>LCD</sub> Level[7:0] | Program the required                | d LCD supply voltage                | 0000000b          |

| Mult[1:0]                   | Number of voltage                   | 00b                                 |                   |

| Partial Display             | Mux Mode multiplex rate             | 0                                   |                   |

| First RowPD[3:0]            | Position of first active row        | 0000b                               |                   |

| Sleep                       | Normal mode                         | Sleep mode: No LCD pixel active,    | 0                 |

|                             |                                     | low power consumption               |                   |

Table 5: Internal functions after reset.

## 8.7 Description of instructions

#### 8.7.1 Initialization 0

#### 8.7.1.1 Mux Mode

Set the multiplex rate.

| Mux Mode                 | 0           | 1           |

|--------------------------|-------------|-------------|

| Multiplex rate           | 65          | 81          |

| (number of row drivers)  |             |             |

| Row drivers              | S0→S32      | S0→S40      |

|                          | S151 → S182 | S143 → S182 |

| Number of column drivers | 118         | 102         |

| Column drivers           | S33 → S150  | S41 → S142  |

| Bias system              | 1/9         | 1/10        |

Table 6

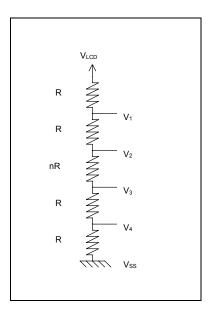

The bias system sets the voltages  $V_1$ ,  $V_2$ ,  $V_3$  and  $V_4$  applied to row and column drivers. Assuming these voltages come from a resistive divider, we have:

The value of the corresponding bias system is:  $V_1/V_{LCD} = 1/(n+4)$ .

The value of the RMS voltage, applied to an LCD pixel ON, divided by the RMS voltage, applied to an LCD pixel OFF,  $(V_{ON})_{RMS}/(V_{OFF})_{RMS}$ , is optimized.

This condition leads to:

$$\frac{1}{(n+4)} = \frac{1}{(1+\sqrt{MultiplexRate})}$$

- bias systems  $\approx$  1/5 for multiplex rate 17 (partial display mode)

- bias systems ≈ 1/9 for multiplex rate 65

- bias systems = 1/10 for multiplex rate 81

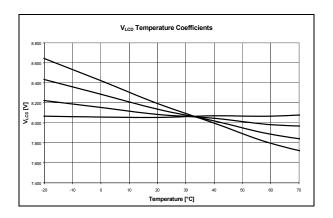

## 8.7.1.2 TC[1:0]

These two bits set the  $V_{\text{LCD}}$  temperature compensation.

4 temperature coefficients are available for the internally generated voltage supply  $V_{LCD}$ . One of these coefficients is selected depending on the LCD display needs. The temperature coefficient is proportional to  $V_{LCD}$ .

| TC[1] | C[1] TC[0] V <sub>LCD</sub> Temperature coefficient (mV/°C) |                          |  |  |  |  |  |

|-------|-------------------------------------------------------------|--------------------------|--|--|--|--|--|

| 0     | 0                                                           | 0                        |  |  |  |  |  |

| 0     | 1                                                           | -0.39×V <sub>LCD</sub>   |  |  |  |  |  |

| 1     | 0                                                           | -0.86×V <sub>LCD</sub>   |  |  |  |  |  |

| 1     | 1                                                           | -1 34 × V <sub>LCD</sub> |  |  |  |  |  |

Table 7

#### 8.7.1.3 Inv. Row

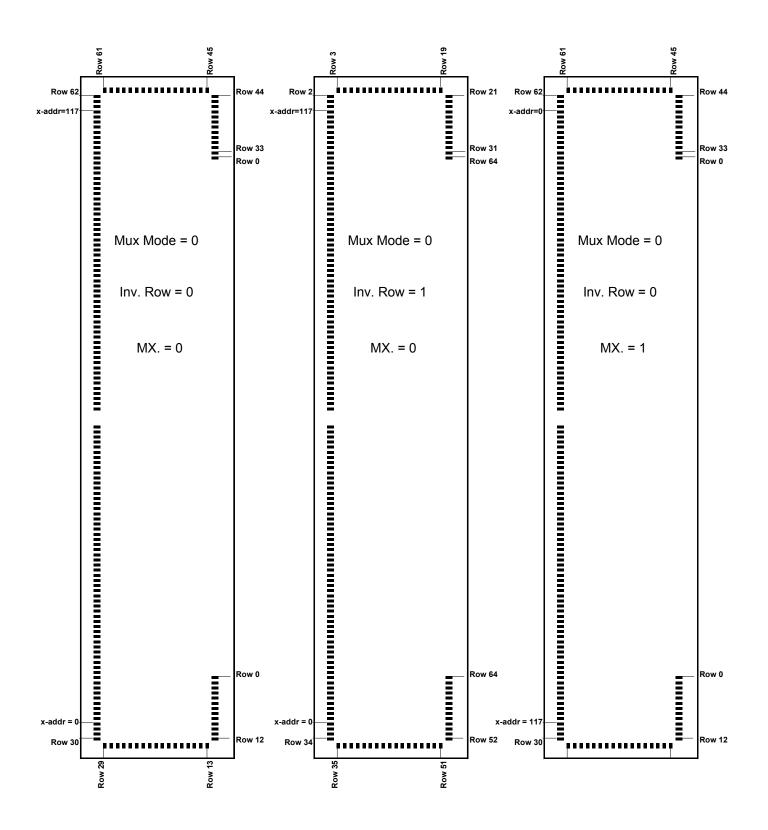

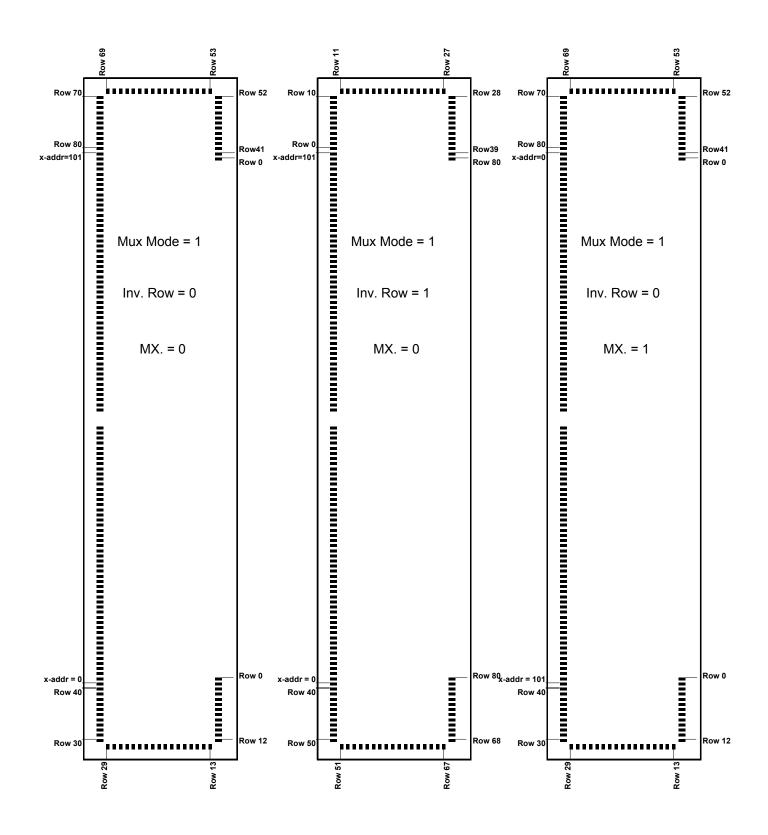

Row driver read direction in the DDRAM can be mirrored to give more flexibility for LCD interconnects. This function acts on the row driver that is activated when a given DDRAM row is read: it becomes active with no need of rewriting the RAM (see Table 8 and Figure 34: LCD output pads configuration in mux 65 depending on Inv. Row and MX).

Read data when Inv. Row=0:

Figure 32

Read data when Inv. Row=1:

Figure 33

|          | Inv. Row    | 0                 | 1                | 0                 | 1                |

|----------|-------------|-------------------|------------------|-------------------|------------------|

|          | Mux Mode    | 0                 | 0                | 1                 | 1                |

|          | S0          | Row 0             | Row 64           | Row 0             | Row 80           |

|          | S1          | Row 1             | Row 63           | Row 1             | Row 79           |

|          | •           | 1<br>1<br>1       | 1                | 1<br>1<br>1       | !                |

|          | S32         | Row 32            | Row 32           | Row 32            | Row 48           |

|          | S33         | x-addre           | ess = 0          | Row 33            | Row 47           |

|          | S34         | x-addre           | ess = 1          | Row 34            | Row 46           |

|          | S35         | x-addre           | ess = 2          | Row 35            | Row 45           |

|          | S36         | x-addre           | ess = 3          | Row 36            | Row 44           |

|          | S37         | x-addre           | ess = 4          | Row 37            | Row 43           |

|          | S38         | x-addre           | ess = 5          | Row 38            | Row 42           |

|          | S39         | x-addre           | ess = 6          | Row 39            | Row 41           |

| <u>e</u> | S40         | x-addre           | ess = 7          | Row 40            | Row 40           |

| name     | S41 to S142 | x-addreess = 8 to | x-addreess = 109 | x-addreess = 0 to | x-addreess = 101 |

| Pad      | S143        | x-addree          | ss = 110         | Row 80            | Row 0            |

|          | S144        | x-addree          | ss = 111         | Row 79            | Row 1            |

|          | S145        | x-addree          | ss = 112         | Row 78            | Row 2            |

|          | S146        | x-addree          | ss = 113         | Row 77            | Row 3            |

|          | S147        | x-addree          | ss = 114         | Row 76            | Row 4            |

|          | S148        | x-addree          | ss = 115         | Row 75            | Row 5            |

|          | S149        | x-addree          | ss = 116         | Row 74            | Row 6            |

|          | S150        | x-addree          | ss = 117         | Row 73            | Row 7            |

|          | S151        | Row 64            | Row 0            | Row 72            | Row 8            |

|          | S152        | Row 63            | Row 1            | Row 71            | Row 9            |

|          |             | 1                 |                  |                   |                  |

|          | S182        | Row 33            | Row 31           | Row 41            | Row 39           |

|          | S183 = S0   | Row 0             | Row 64           | Row 0             | Row 80           |

Table 8

#### 8.7.1.4 MX

Column driver pads can also be mirrored to give more flexibility for LCD interconnects.

This function changes the x-address pointer to reverse columns of the DDRAM accessed during a write cycle: a rewrite cycle is required to observe changes on outputs (see Figure 34: LCD output pads configuration in mux 65 depending on Inv. Row and MX)

Table 9 shows how the DDRAM is connected to LCD output pads, depending on bits Mux Mode, MX and Inv. Row.

|      | MX        | 0                | 1                 | 0               | 1                 |  |  |  |

|------|-----------|------------------|-------------------|-----------------|-------------------|--|--|--|

|      | Mux Mode  | 0                | 0                 | 1               | 1                 |  |  |  |

|      | S0        | Ro               | w 0               | Ro              | w 0               |  |  |  |

|      | -         |                  |                   |                 | 1<br>1<br>1       |  |  |  |

|      | S32       | Rov              | v 32              | Rov             | v 32              |  |  |  |

|      | S33       | x-address = 0    | x-address = 117   | Row 33          |                   |  |  |  |

|      | S34       | x-address = 1    | x-address = 116   | Rov             | v 34              |  |  |  |

|      | S35       | x-address = 2    | x-address = 115   | Rov             | v 35              |  |  |  |

|      | S36       | x-address = 3    | x-address = 114   | Rov             | v 36              |  |  |  |

|      | S37       | x-address = 4    | x-address = 113   | Rov             | v 37              |  |  |  |

|      | S38       | x-address = 5    | x-address = 112   | Rov             | v 38              |  |  |  |

|      | S39       | x-address = 6    | x-address = 111   | Rov             | v 39              |  |  |  |

|      | S40       | x-address = 7    | x-address = 110   | Rov             |                   |  |  |  |

|      | S41       | x-address = 8    | x-address = 109   | x-address = 0   | x-address = 101   |  |  |  |

|      | S42       | x-address = 9    | x-address = 108   | x-address = 1   | x-address = 100   |  |  |  |

| a)   | S43       | x-address = 10   | x-address = 107   | x-address = 2   | x-address = 99    |  |  |  |

| name | S44 to    | x-address =11 to | x-address =106 to | x-address =3 to | x-address = 98 to |  |  |  |

| ű    | S139      | x-address =106   | x-address =11     | x-address = 98  | x-address = 3     |  |  |  |

| Pad  | S140      | x-address = 107  | x-address = 10    | x-address = 99  | x-address = 2     |  |  |  |

|      | S141      | x-address = 108  | x-address = 9     | x-address = 100 | x-address = 1     |  |  |  |

|      | S142      | x-address = 109  | x-address = 8     | x-address = 101 | x-address = 0     |  |  |  |

|      | S143      | x-address = 110  | x-address = 7     | Rov             | v 80              |  |  |  |

|      | S144      | x-address = 111  | x-address = 6     | Rov             | v 79              |  |  |  |

|      | S145      | x-address = 112  | x-address = 5     | Rov             | v 78              |  |  |  |

|      | S146      | x-address = 113  | x-address = 4     | Rov             | v 77              |  |  |  |

|      | S147      | x-address = 114  | x-address = 3     | Rov             | v 76              |  |  |  |

|      | S148      | x-address = 115  | x-address = 2     | Rov             | v 75              |  |  |  |

|      | S149      | x-address = 116  | x-address = 1     | Rov             | v 74              |  |  |  |

|      | S150      | x-address = 117  | x-address = 0     | Rov             | v 73              |  |  |  |

|      | S151      | Rov              | v 64              | Row 72          |                   |  |  |  |

|      |           |                  |                   |                 |                   |  |  |  |

|      | S182      | Rov              | v 33              | Rov             | Row 41            |  |  |  |

|      | S183 = S0 | Ro               | w 0               | Ro              | w 0               |  |  |  |

Table 9: Relation between LCD output pads and row and columns of DDRAM

The combination of Mux Mode, Inv. Row and MX gives the following figures (next page) of output pads.

#### 8.7.1.5 Blank

Sets all the LCD pixels OFF.

Every row driver and column driver is at V<sub>SS</sub> level.

DDRAM content is not affected by this instruction.

#### 8.7.1.6 Checker

Sets all the LCD pixels in a checker board pattern, LCD displays alternately ON and OFF pixels. DDRAM content is not affected by this instruction.

#### 8.7.1.7 Inv. Video

Sets an inverse video mode.

- If Inv. Video = 0, a logical 1 level stored in the DDRAM leads to an "ON" pixel displayed on the LCD.

- If Inv. Video = 1, a logical 1 level stored in the DDRAM leads to an "OFF" pixel displayed on the LCD.

DDRAM content is not affected by this instruction.

Figure 34: LCD output pads configuration in mux 65 depending on Inv. Row and MX

Figure 35: LCD output pads configuration in mux 81 depending on Inv. Row and MX

#### 8.7.2 Initialization 1

#### 8.7.2.1 X[6:0]

These 7 bits set the x-address pointer of the DDRAM.

Data are written into column "x-address" with: X[6] = MSB, X[0] = LSB.

As the number of column drivers depends on the selected multiplex rate, the DDRAM x-address pointer should also satisfy the following conditions:

- If Mux Mode = 0 then 0 ≤ x-address ≤ 1110101b. (117).

- If Mux Mode = 1 then 0 ≤ x-address ≤ 1100101b. (101).

#### 8.7.2.2 V

Vertical addressing:

- If V = 0, DDRAM x-address pointer is incremented or decremented after each data byte sent.

- If V = 1, DDRAM y-address pointer is incremented or decremented after each data byte sent.

#### 8.7.3 Initialization 2

#### 8.7.3.1 YI3:01

These 4 bits set the y-address pointer of the DDRAM.

Data are written into bank "y-address" with Y[3]= MSB, Y[0]= LSB.

As the multiplex rate is digitally programmable, the DDRAM y-address pointer should also satisfy the following conditions:

- If Mux Mode = 0 then  $0 \le y$ -address  $\le 1000b$ .

- If Mux Mode = 1 then  $0 \le v$ -address  $\le 1010b$ .

#### 8.7.3.2 Vlcd Dischg.

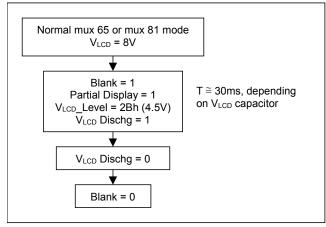

The  $V_{LCD}$  discharge function can discharge the capacitor connected to PAD  $V_{LCD}$ . This operation becomes necessary when changing from Mux 65 or 81 mode to Partial Display Mode. In this case, a lower  $V_{LCD}$  is required than the voltage used for Mux 65 or 81 operation, the display at beginning of partial mode operation could be completely 'ON' until  $V_{LCD}$  has decreased to its new correct value.

To avoid this effect, an internal pull down helps the  $V_{LCD}$  voltage to drop down and to reach the new optimum value in a short time. This pull down is active until bit 'Vlcd Dischg' is reset to low level.

Typical use of 'Vlcd Dischg' command:

Using this command with external power supply on  $V_{LCD}$  can damage the IC.

## 8.7.3.3 DEC

DEC controls the DDRAM writing direction:

- If DEC = 0 then x-address pointer increments after each byte written into the DDRAM.

- If DEC = 1 then x-address pointer decrements after each byte written into the DDRAM.

#### 8.7.3.4 LSB

This instruction changes the bytes send to the DDRAM before writing them. For instance, for bank 1 we have:

- If LSB = 0 then DB7 is written on Row 1.

- If LSB = 1 then DB0 is written on Row 1 (see Figure 14 and Figure 15).

## 8.7.4 Initialization 3

### 8.7.4.1 Vlcd Level[7:0]

This byte sets the internally generated voltage level.

These 8 bits generate integer "V<sub>LCD</sub> Level", V<sub>LCD</sub> Level [7] = MSB, V<sub>LCD</sub> Level [0] = LSB.

V<sub>LCD</sub> is given by the following formula:

$$V_{\text{LCD}} = 3.02 + 0.0352 \times V_{\text{LCD}} \text{Level}$$

#### 8.7.5 Initialization 4

#### 8.7.5.1 Mult[1:0]

These two bits set the internal voltage multiplier factor.

These bits should be defined depending on the  $V_{HV}$  supply voltage level and the current consumption due to LCD load, to have a correct  $V_{LCD}$  voltage.

If low V<sub>LCD</sub> is required, for instance when partial display mode is enabled, lower voltage multiplier range should be used, resulting in a current consumption reduction (due to better voltage multiplier efficiency at lower multiplication rate).

| Mult1 | Mult0 | Voltage multiplier |

|-------|-------|--------------------|

| 0     | 0     | × 2                |

| 0     | 1     | ×3                 |

| 1     | 0     | × 4                |

| 1     | 1     | ×5                 |

Table 10

#### 8.7.5.2 Partial Display

Set the partial display configuration of the driver (multiplex ratio 17).

In this configuration, 17 rows are active:

- The row which corresponds to RAM address 0.

- 16 selectable rows, first one is defined by First Row PD [3:0].

| Partial Display | Multiplex rate                   |

|-----------------|----------------------------------|

| 0               | 65 or 81 (depending on Mux Mode) |

| 1               | 17                               |

Table 11

#### 8.7.5.3 First Row PD[3:0]

Partial display mode yields to an LCD with 2 activated banks.

Row 0 is always active, it could be used to drive icons.

The 16 other active rows are selected from 64 or 80 rows, as shown in following table:

| Mux<br>Mode | First<br>Row<br>PD[3] | First<br>Row<br>PD[2] | First<br>Row<br>PD[1] | First<br>Row<br>PD[0] | First active row (DDRAM) | Last active row<br>(DDRAM) | Activated banks |

|-------------|-----------------------|-----------------------|-----------------------|-----------------------|--------------------------|----------------------------|-----------------|

| 0 or 1      | 0                     | 0                     | 0                     | 0                     | Row 1                    | Row 16                     | 0,1,2           |

|             | 0                     | 0                     | 0                     | 1                     | Row 9                    | Row 24                     | 0,2,3           |

|             | 0                     | 0                     | 1                     | 0                     | Row 17                   | Row 32                     | 0,3,4           |

|             | 0                     | 0                     | 1                     | 1                     | Row 25                   | Row 40                     | 0,4,5           |

|             | 0                     | 1                     | 0                     | 0                     | Row 33                   | Row 48                     | 0,5,6           |

|             | 0                     | 1                     | 0                     | 1                     | Row 41                   | Row 56                     | 0,6,7           |

|             | 0                     | 1                     | 1                     | 0                     | Row 49                   | Row 64                     | 0,7,8           |

| 1           | 0                     | 1                     | 1                     | 1                     | Row 57                   | Row 72                     | 0,8,9           |

|             | 1                     | 0                     | 0                     | 0                     | Row 65                   | Row 80                     | 0,9,10          |

Table 12

- If Mux Mode = 0, 0 ≤ First Row PD [3:0] ≤ 0110b.

- If Mux Mode = 1, 0 ≤ First\_Row PD [3:0] ≤ 1000b.

Values for "First\_Row PD [3:0]" outside these ranges are not allowed.

#### 8.7.5.4 Sleep

This function stops all functionality, internal oscillator and voltage multiplier are off, and LCD is blanked. It yields to a very low current consumption with leakage currents only.

#### 8.7.6 Test 0 to 3

All bits must be set to 0 (see example in typical application page 37).

#### 8.8 LCD outputs

The LCD output signals and voltages are optimized for the best LCD contrast and minimum DC component of voltage applied to the LCD display. Table 13 gives bias voltages referring to  $V_{\text{LCD}}$ .

| Multiplex Rate           | V <sub>LCD</sub> | V <sub>1</sub>                            | V <sub>2</sub>                            | V <sub>3</sub>         | V <sub>4</sub>         | V <sub>SS</sub> |

|--------------------------|------------------|-------------------------------------------|-------------------------------------------|------------------------|------------------------|-----------------|

| n                        | 1                | $1 - \left(\frac{1}{\sqrt{n} + 1}\right)$ | $1 - \left(\frac{2}{\sqrt{n} + 1}\right)$ | $\frac{2}{\sqrt{n}+1}$ | $\frac{1}{\sqrt{n}+1}$ | 0               |

| 81 (Mux Mode = 1)        | 1                | 0.90                                      | 0.80                                      | 0.20                   | 0.10                   | 0               |

| 65 (Mux Mode = 0)        | 1                | 0.89                                      | 0.78                                      | 0.22                   | 0.11                   | 0               |

| 17 (Partial Display = 1) | 1                | 0.80                                      | 0.60                                      | 0.40                   | 0.20                   | 0               |

Table 13: Values of intermediate bias voltages

Table 14 gives ratios of  $V_{LCD}$  in reference to RMS voltage of an OFF pixel, and the RMS voltage ratios between an ON pixel and an OFF pixel (achievable contrasts). These values correspond to bias voltages described in Table 13.

| Programmed multiplex rate | LCD Bias<br>configuration | $\frac{V_{LCD}}{V_{OFF}(RMS)}$                                | $\frac{V_{ON}(RMS)}{V_{OFF}(RMS)}$           |

|---------------------------|---------------------------|---------------------------------------------------------------|----------------------------------------------|

| 81                        | 6 levels                  | $\sqrt{\frac{\sqrt{n}(\sqrt{n}+1)^2}{2(\sqrt{n}-1)}} = 7.500$ | $\sqrt{\frac{\sqrt{n}+1}{\sqrt{n}-1}}=1.118$ |

| 65                        | 6 levels                  | $\sqrt{\frac{\sqrt{n}(\sqrt{n}+1)^2}{2(\sqrt{n}-1)}} = 6.847$ | $\sqrt{\frac{\sqrt{n}+1}{\sqrt{n}-1}}=1.133$ |

| 17                        | 6 levels                  | $\sqrt{\frac{\sqrt{n}(\sqrt{n}+1)^2}{2(\sqrt{n}-1)}} = 4.162$ | $\sqrt{\frac{\sqrt{n}+1}{\sqrt{n}-1}}=1.281$ |

Table 14: Required LCD supply voltage and achieved LCD contrast

The selected LCD display gives the value of  $V_{OFF}(RMS)$  and the value of  $\frac{V_{LCD}}{V_{OFF}(RMS)}$  gives the needed  $V_{LCD}$  voltage

supply. The Partial Display mode decreases  $V_{LCD}$ , leading to lower power consumption. Lower  $V_{LCD}$  decreases consumption because less stages for voltage multiplier can be selected.

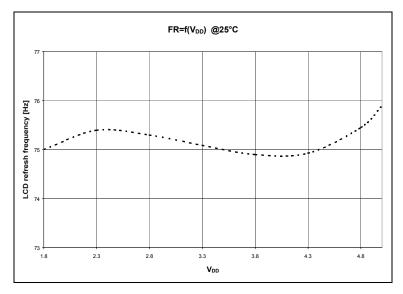

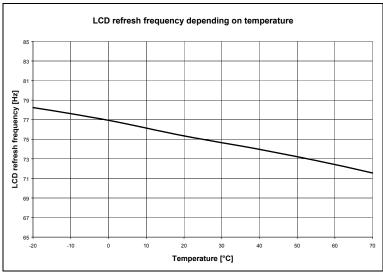

## 8.9 LCD refresh frequency

LCD refresh frequency depends on an internal RC oscillator. Pad FR outputs this frequency, multiplied by the multiplex rate. Following figures display typical variations depending on  $V_{DD}$  power supply and temperature.

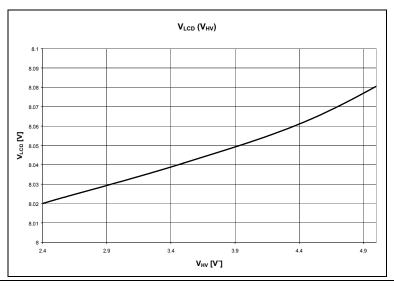

## 8.10 $V_{\text{\tiny LCD}}$ depending on $V_{\text{\tiny HV}}$

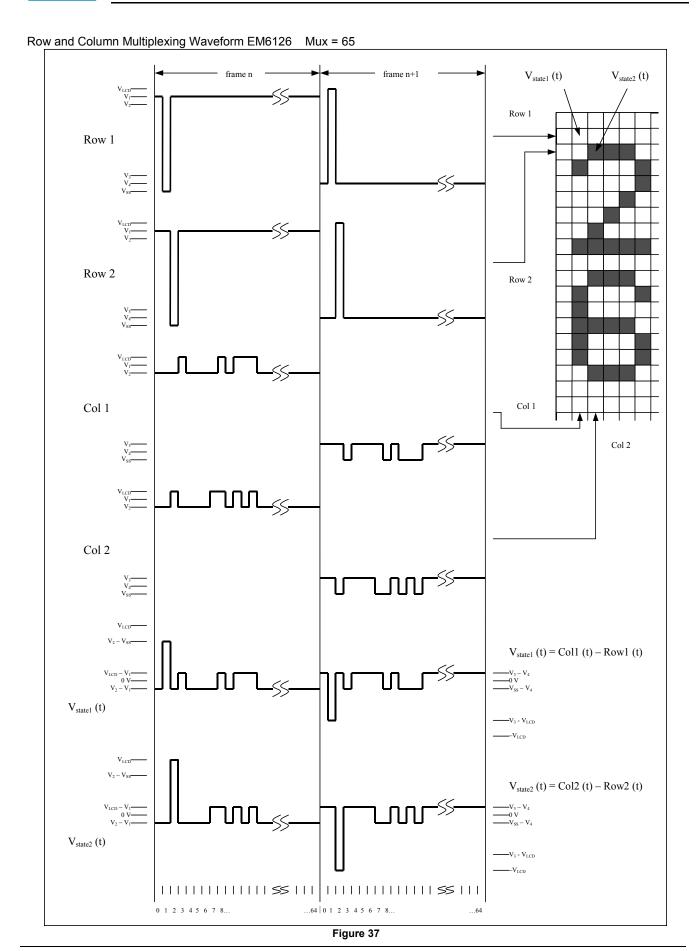

#### 8.11 LCD driver waveforms

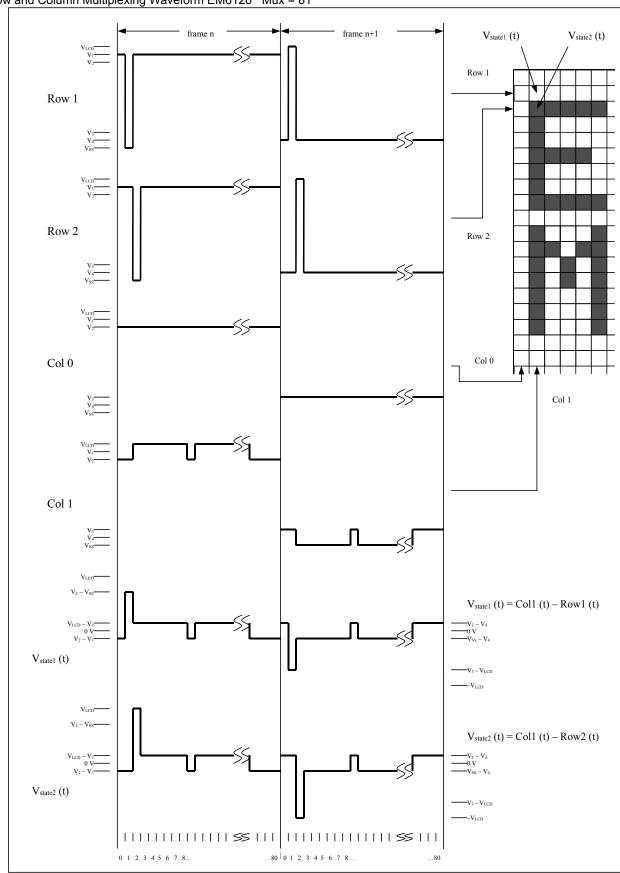

Row and Column Multiplexing Waveform EM6126 Mux = 81

Figure 36

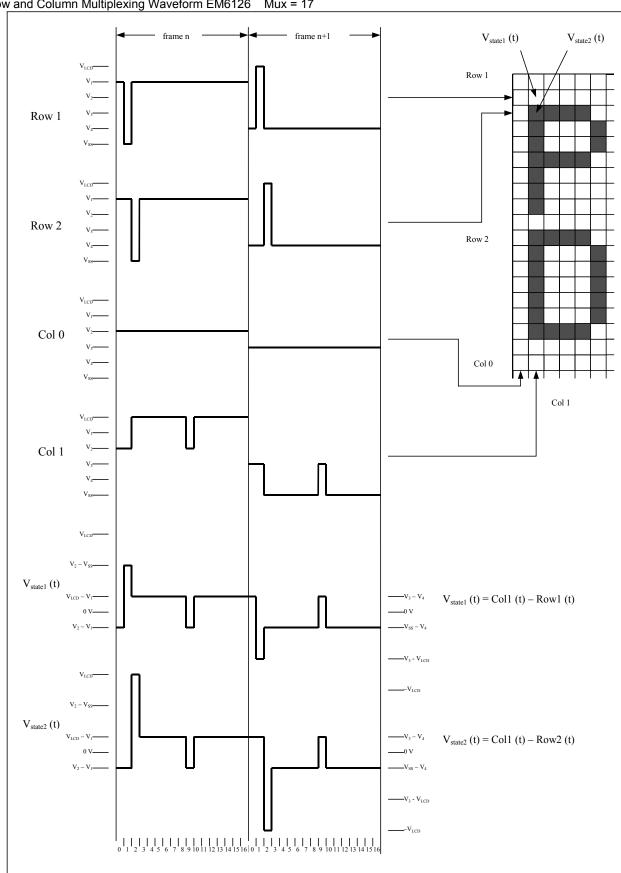

## 8.11.1 Partial Display

Row and Column Multiplexing Waveform EM6126 Mux = 17

Figure 38

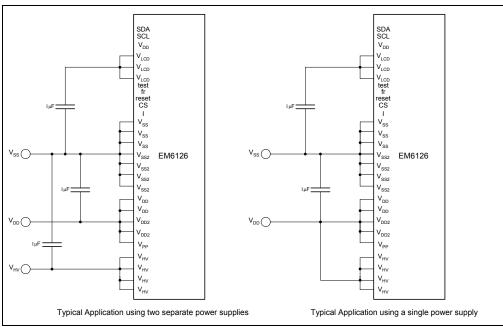

## 9 Typical Application

#### 9.1 Power supply connection

Figure 39: Power Supply connection

#### 9.2 Connection and communication with the display

This example gives typical programming steps for EM6126 with  $I^2C$  interface, for serial interface, start and stop conditions should be replaced by CS at 0L and CS at 1L. LCD display is connected as described on Figure 40:

Figure 40: Connection between EM6126 and LCD for the application example

| Step | DB7 | DB6 | DB5 | DB4     | DB3    | DB2 | DB1 | DB0 | Comment                                                                                                                                                                   | Display   |

|------|-----|-----|-----|---------|--------|-----|-----|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| 1    |     |     |     | Pow     | er on  |     |     | •   |                                                                                                                                                                           | Undefined |

| 2    |     |     |     | Re      | set    |     |     |     | A reset cycle must always follow the power on                                                                                                                             | Blank     |

| 3    |     |     | 120 | C start | condit | ion |     |     |                                                                                                                                                                           | Blank     |

| 4    | х   | Х   | х   | Х       | Х      | Х   | х   | 0   | EM6126 slave address + write mode                                                                                                                                         | Blank     |

| 5    | 1   | 0   | 0   | 0       | 0      | 0   | 0   | 0   | Control byte for initialization 0                                                                                                                                         | Blank     |

| 6    | 1   | 0   | 1   | 0       | 0      | 0   | 0   | 0   | Data byte = initialization 0  Multiplex Rate = 81  Vlcd Temperature Coefficient = -0.39 x Vlcd (mV/°C)  No row or column mirroring  No blank, Checker or Video functions. | Blank     |

| 7    | 1   | 0   | 0   | 0       | 0      | 0   | 1   | 1   | Control byte for initialization 3                                                                                                                                         | Blank     |

| 8    | 1   | 0   | 0   | 0       | 1      | 1   | 1   | 0   | Data byte = initialization 3  Programmed Vlcd_level = 10001110b (8Eh=142) Vlcd = 3.02 + 142*0.0352 = 8.02V                                                                | Blank     |

| 9    | 1   | 0   | 0   | 0       | 0      | 1   | 0   | 0   | Control byte for initialization 4                                                                                                                                         | Blank     |