## **DESCRIPTION**

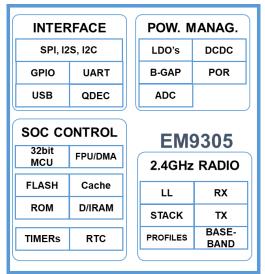

The EM9305 is a tiny, ultra-low power and high-performance  $Bluetooth^{\otimes}$  LE chip.

Its highly flexible architecture allows it to act as a companion IC to any ASIC or MCU-based product, or as a complete System-on-Chip (SoC). Its flexibility also allows it to be used with other protocols. Custom applications can be executed on an efficient 32-bit ARC processor from a 512kB flash using a cache and DMA to optimize power. DSP and floating-point units can be exploited to implement advanced audio and tracking algorithms. Low-power serial interfaces (SPI, I2C, I2S, and UART) can be used to talk with external sensors, memory, display, or touch drivers. In addition, EM9305 can directly be connected to a USB port of a PC.

Included in the software is a fully featured Bluetooth® LE link layer, Host Controller Interface (HCI), stack, profiles and services, and firmware over-the-air (FOTA) updating capability. All Bluetooth® Core 5.4 features are available on the EM9305, including LE 2M and LE Coded communication, Direction Finding for localization applications. Isochronous channels are also available for LE Audio applications.

The EM9305 includes a sophisticated on-chip power management system supporting 1.5V or 3V batteries, and it can be directly powered from an attached 5V USB port. An inductor-less mode for 1.5V batteries can help further reduce the BOM. All 64kB of RAM memory can be kept in retention during sleep, or in 4kB increments to optimize leakage. A stable, low-power sleep oscillator (RC or crystal based) minimizes power consumption while in a connected state or RTC operation. Current consumption is minimized for all modes of application utilizing an efficient scheduler and memory manager.

The EM9305 features a state-of-the-art 2.4GHz transceiver: a low-power receiver with excellent sensitivity/selectivity, and a programmable transmitter up to +10dBm for optimized output power and current consumption.

The PCB footprint and cost is minimized with a very low external component count and several package options. The circuit is offered in a WLCSP23 wafer level chip-scale package, a plastic QFN-28 package, and bare die/wafer form. The device and reference design are available over the industrial temperature range.

# BLUETOOTH® LE SOC AND COMPANION CHIP WITH FLASH

# **KEY FEATURES**

- I Energy efficient, industry standard, ARC EM7D, 32-bit MCU with DMA and Cache for minimum power consumption

- · DSP and FPU for signal processing

- · 64kB ROM

- 512kB flash memory for multi-protocol and applications

- · 64kB data/instruction RAM, all retainable starting from 4kB

- · 48MHz MCU and memory-read speed

- USB (only on QFN/die), UART, I2C, I2S/TDM and SPI interfaces

- · ADC and on-chip temperature indicator

- · 12 GPIO on QFN, 10 GPIO on WLCSP

- I Qualified against Bluetooth® Core 5.4

- · LE 2M and LE Coded support

- Direction Finding support

- · Isochronous channels for LE Audio applications

- · SPI and UART HCI Transport Layers

- Up to 4 simultaneous connections

## I Security Features

- · True Random Number Generator

- · AES-128 Hardware Encryption/Decryption Engine

- Key Generation (ECC-P256)

- Secure Key Containers

- · Secure Firmware Over-the-Air Updating (FOTA)

- · Secure lifecycle management

# I Sophisticated Power Management System

- · Digital step up/down DCDC operation supporting 1.1-3.6V

- · Inductor-less voltage multiplier mode for minimal BOM

- · Direct power from 5V USB port (only on QFN/die)

- Low frequency RC or 32kHz crystal oscillator time base

#### I Low Current Consumption at 3V

- 3.1mA typical receiver current

- · 3.4mA typical transmitter current at 0dBm

- · 390nA Bluetooth® LE sleep mode with XTAL (4 kB RAM retention)

- · 200nA in deep sleep mode (no RAM retention)

- · 7.5nA in disable mode

#### I High Performance RF

- -94/-97/-103dBm RX sensitivity for 2Mbps/1Mbps/125kbps modes and 37-byte payload

- -33dBm to +10dBm transmitter output power range

## I Low Component Count and Cost:

- · Single ended antenna pin with matching network

- · Minimal DC component network

- · 48MHz XTAL, and optional 32kHz XTAL

- · QFN-28 (4x4mm), WLCSP23 (1.8x1.8mm), bare-die/wafer

- I Operating temperature: -40°C to +85°C

# **APPLICATIONS**

Bluetooth® LE applications such as:

- **I** Beacons

- I Positionina

- I Logistic tracking

- I Wearables and Sports Equipment

- I Healthcare Monitoring

- I Remote Sensing

- I Motion and Tracking Devices

- I Home Automation

- I Light Control Applications

- I Smart cities

- I Wireless Mice and Keyboards

- I Alarms and Security System

- **I** Toys

Enabled by the mobile phone as access point to the Internet

#### **CUSTOMER SUPPORT**

- I Hardware and PCB design

- I Firmware development, software development kits

- I FCC/CE certification support

- I Forum for hardware and software support

## TYPICAL APPLICATION DIAGRAMS

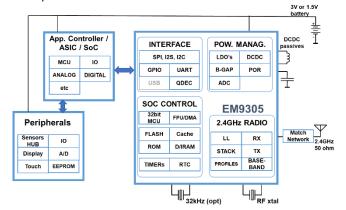

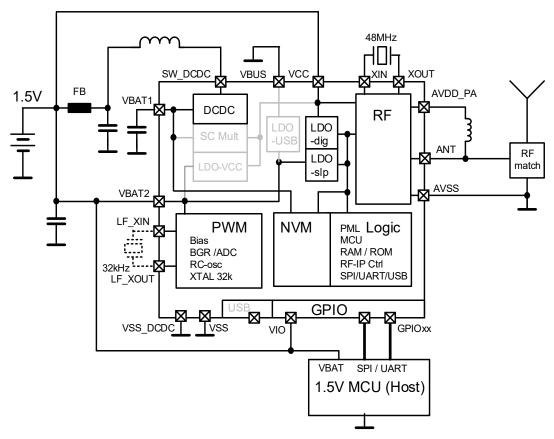

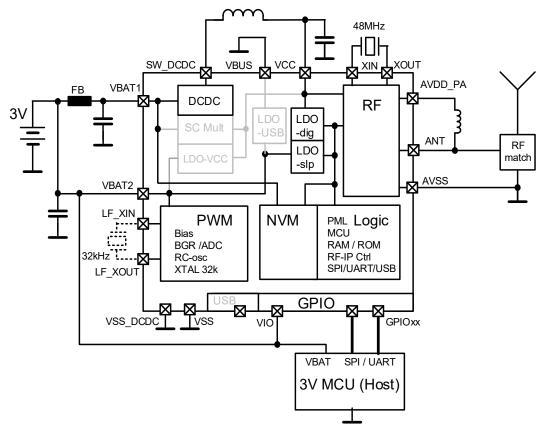

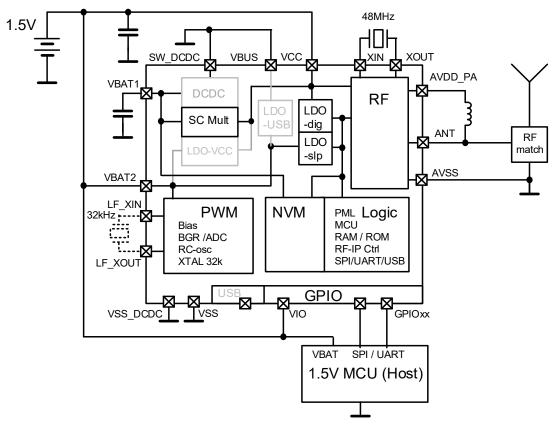

The EM9305 is the ideal Bluetooth® LE companion for any MCU or ASIC application, as illustrated in Figure 0-1. It may be easily connected with:

- I standard 3V MCU's within the very rich catalog of any microprocessor vendor.

- I standard 1.5V MCU's such as ultra-low-power watch microprocessors from EM Microelectronic,

- I any custom sensor processing ASIC for customers requiring a simple add-on function.

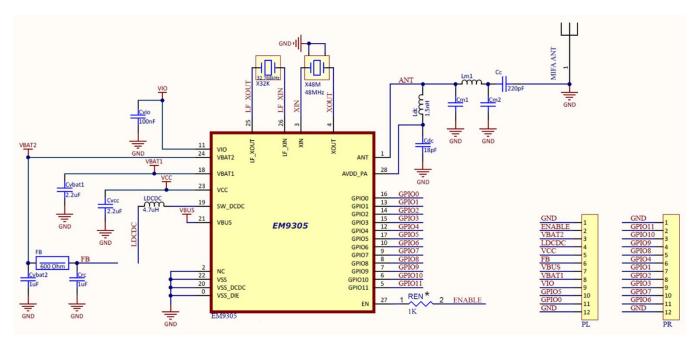

Figure 0-1: Typical application schematic – Bluetooth® LE Companion IC to any MCU or ASIC

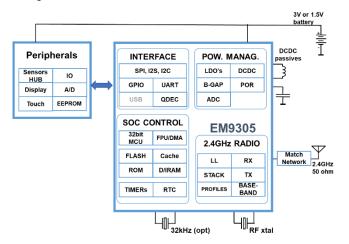

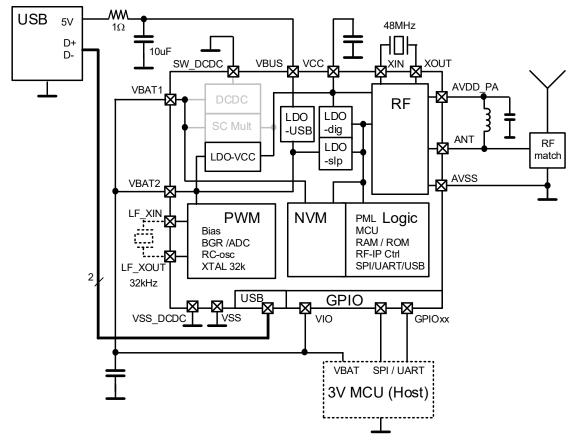

The EM9305 is a flexible solution, which may also be used without an external MCU for simple applications such as beacons. As illustrated in Figure 0-2, it may be directly connected to external digital sensors, which may exploit the EM9305's internal 32-bit processing capability, or with sensor hubs such as from EM's SENtral platform.

Other applications using A/D converters, display and/or touch interfaces can also be implemented.

The EM9305 can be supplied from a 3V battery (e.g. Lithium coin-cell). In such case, the DCDC converter is put into step-down configuration. The EM9305 can also be supplied from a 1.5V battery (e.g. Alkaline, Silver-Oxide, or Zinc-Air single cells). In such case, the DCDC converter is put into step-up configuration.

Figure 0-2: Typical application schematic – EM9305 in SOC mode connected with peripherals

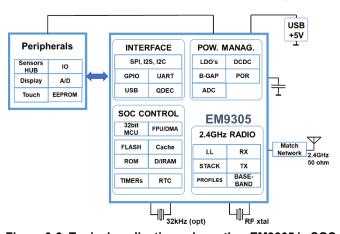

Finally, configurations are also possible without the DCDC converter (no inductor required), for systems already with power management, or for systems that require the lowest bill of materials. An example of a configuration not requiring the inductor is the USB powered application shown in Figure 0-3.

Figure 0-3: Typical application schematic – EM9305 in SOC mode powered from USB

# **TABLE OF CONTENTS**

| DESCRI     | PTION                                     | 1  |

|------------|-------------------------------------------|----|

| KEY FEA    | ATURES                                    | 1  |

| APPLICA    | ATIONS                                    | 2  |

| CUSTOR     | MER SUPPORT                               |    |

|            | L APPLICATION DIAGRAMS                    |    |

|            |                                           |    |

|            | OF CONTENTS                               |    |

| LIST OF    | FIGURES                                   | 7  |

| LIST OF    | *TABLES                                   | S  |

| 1. P       | PRODUCT OVERVIEW                          | 11 |

| 1.1.       | Introduction                              | 11 |

| 1.2.       |                                           |    |

| 1.2        |                                           |    |

| 1.2        | 2.2. Software Architecture                | 13 |

| 1.2        | 2.3. RF Transceiver Overview              | 13 |

| 1.2        | P.4. Power Management Overview            | 14 |

| 1.2        | , 3                                       |    |

| 1.3.       |                                           |    |

| 1.4.       | RELATED DOCUMENTS                         | 18 |

| 2. F       | HANDLING PROCEDURES                       | 19 |

| 3. P       | PIN DESCRIPTION                           | 20 |

| 4. E       | ELECTRICAL SPECIFICATIONS                 | 23 |

| 4.1.       | ABSOLUTE MAXIMUM RATINGS                  | 23 |

| 4.2.       | GENERAL OPERATING CONDITIONS              | 23 |

| 4.3.       | ELECTRICAL CHARACTERISTICS                | 23 |

| 4.3        |                                           |    |

| 4.3        |                                           |    |

| 4.3        | 5 · · · J· · · · · · · · · · · · · · · ·  |    |

|            | TIMING CHARACTERISTICS                    |    |

| 4.4<br>4.5 | 1.1. Digital Interfaces Timing Parameters |    |

|            | DIGITAL PROCESSING (DPR)                  |    |

|            | ·                                         |    |

|            | CPU                                       |    |

| 5.1        |                                           |    |

| 5.1        | 5 ' '                                     |    |

| 5.1<br>5.1 |                                           |    |

| 5.2.       | MEMORY                                    |    |

| 5.3.       | NVM Controller                            |    |

| 5.4.       | CLOCK CONTROLLER                          |    |

| 5.5.       | APPLICATIONS                              |    |

| 5.5        |                                           |    |

| 5.5        |                                           |    |

| 5.5        | 5.3. Software Installation                | 37 |

| 6. P       | POWER MANAGEMENT AND CLOCK STRUCTURE      | 38 |

| 6.1.       | SUPPLY DOMAINS                            | 38 |

| 6.2.       | LOGIC POWER DOMAINS                       |    |

|            |                                           |    |

| 6.3. | SUPPLY   | Y MONITORING                                                             |     |

|------|----------|--------------------------------------------------------------------------|-----|

|      | .3.1.    | Supply Voltage Level Detector (SVLD)                                     | 39  |

|      | .3.2.    | Digital Current Meter                                                    |     |

| 6.4. |          | ITING MODES                                                              |     |

| 6.5. |          | Structure                                                                |     |

| 6.6. |          | STRUCTURE                                                                |     |

|      | .6.1.    | LF XTAL Modes                                                            |     |

|      | .6.2.    | LF RC Clock Calibration                                                  |     |

| 6.   | .6.3.    | LF XTAL Clock Calibration                                                | 43  |

| 7.   | RADIO.   |                                                                          | 44  |

| 7.1. | 2 4GE    | łz Front-End                                                             | ΔΔ  |

| 7.1. |          | NTROLLER                                                                 |     |

| 7.3. |          | T PROCESSOR                                                              |     |

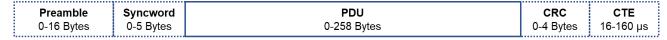

|      | .3.1.    | Bluetooth <sup>®</sup> LE and Bluetooth <sup>®</sup> LE 2M Packet format |     |

|      | .3.2.    | Bluetooth® LE Coded Packet format                                        |     |

| 7.4. | DIRECT   | FION FINDING                                                             |     |

|      |          |                                                                          |     |

| 8.   |          | ERALS                                                                    |     |

| 8.1. | ADC.     |                                                                          | 50  |

| 8.2. |          |                                                                          |     |

| 8.3. |          | ASTER                                                                    |     |

| 8.4. | •        | DM                                                                       |     |

| 8.5. |          |                                                                          |     |

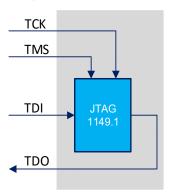

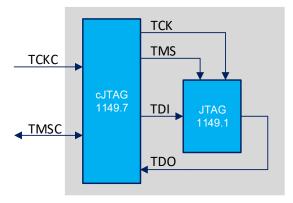

|      | .5.1.    | JTAG (IEEE 1149.1)                                                       |     |

|      | .5.2.    | cJTAG (IEEE 1149.7)                                                      |     |

| 8.6. | -        |                                                                          |     |

| 8.7. |          | ASTER                                                                    |     |

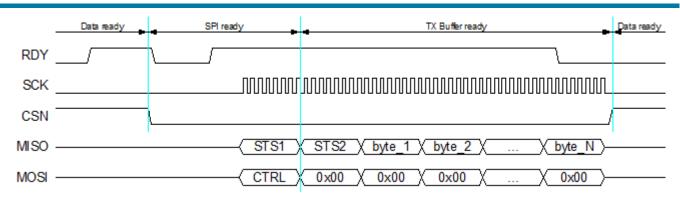

|      | .7.1.    | SPI Modified Protocol                                                    |     |

| 8.8. |          | AVE                                                                      |     |

| _    | .8.1.    | SPI Half-Duplex OperationSPI Full-Duplex Operation                       |     |

| _    | .8.2.    | SPI Flow Control                                                         |     |

| 8.9. | .8.3.    | RATURE INDICATOR                                                         |     |

|      |          | S                                                                        |     |

|      | .10.1.   | Universal Timer                                                          |     |

|      |          | Sleep Timer                                                              |     |

|      | .10.3.   | Protocol Timer                                                           |     |

| _    |          |                                                                          |     |

|      | .11.1.   | UART 1-wire                                                              |     |

|      |          |                                                                          |     |

| 9.   |          | ΓΥ                                                                       |     |

| 9.   | SECURI   | I Y                                                                      | ,/3 |

| 9.1. | CRYPT    | OGRAPHIC SERVICES                                                        | 73  |

| 9.   | .1.1.    | AES                                                                      |     |

| 9.   | .1.2.    | RNG                                                                      |     |

| 9.   | .1.3.    | Software Libraries                                                       |     |

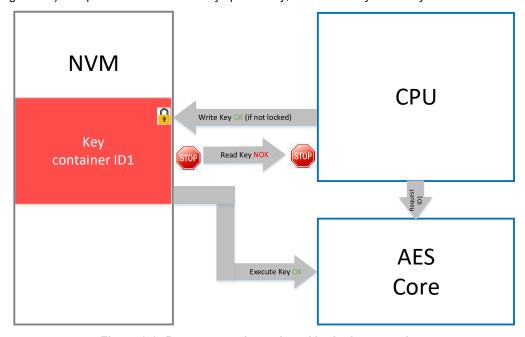

| 9.2. | SECUR    | E KEY CONTAINERS                                                         |     |

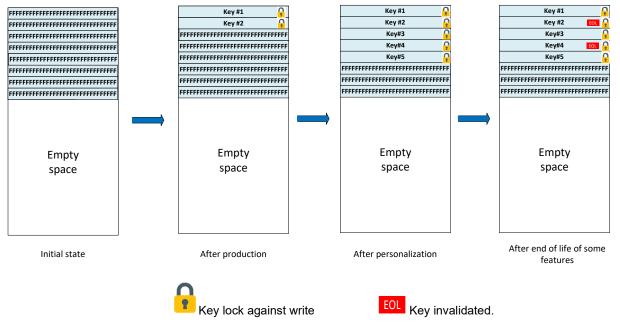

| _    | .2.1.    | Eight First Key Containers                                               |     |

|      | .2.2.    | Other Key Containers                                                     |     |

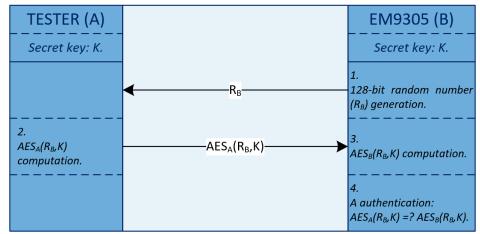

| 9.3. | AUTHE    | NTICATION SCHEME                                                         | 75  |

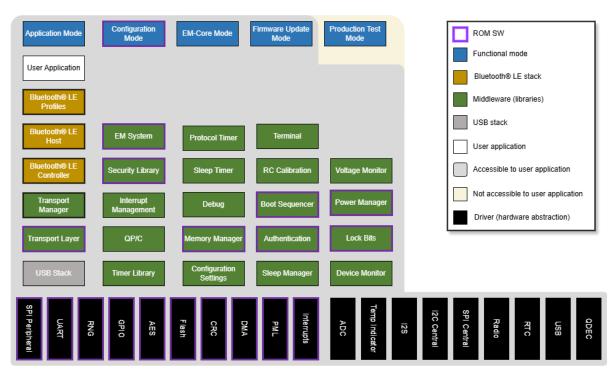

| 10.  | SOFTWA   | ARE ARCHITECTURE                                                         | 76  |

| 10.1 | 1. HARDV | NARE PLATFORM                                                            | 77  |

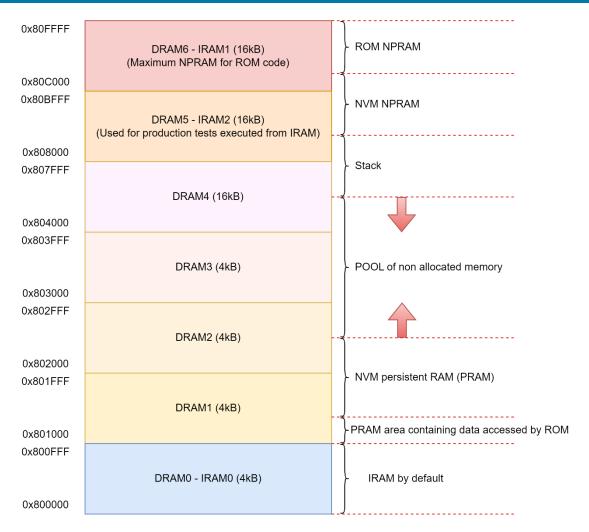

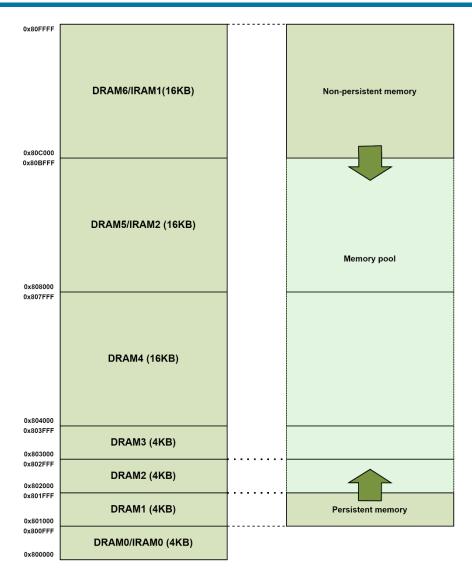

| 10   | 0.1.1.   | Memory Organization                                                      | 77  |

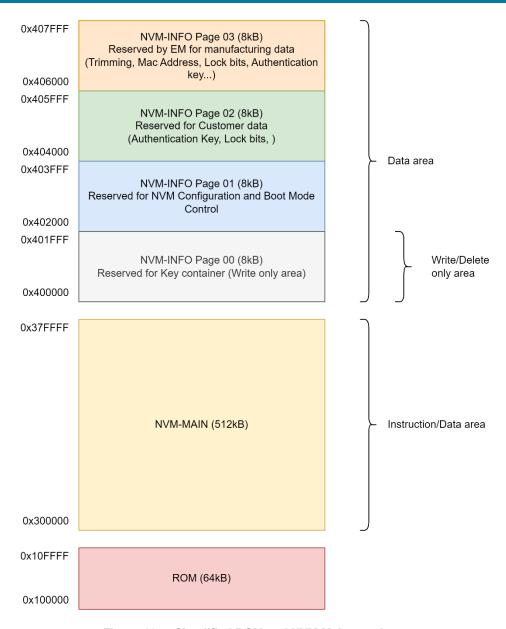

|      | 0.1.2.   | NVM Memory                                                               |     |

| 10.2 | 2. Mode  | S OF OPERATION                                                           | 80  |

| 10.2.1.    | Configuration Mode                       | 80  |

|------------|------------------------------------------|-----|

| 10.2.2.    | Application Mode                         | 80  |

| 10.3. MEN  | MORY USAGE BY FIRMWARE                   | 81  |

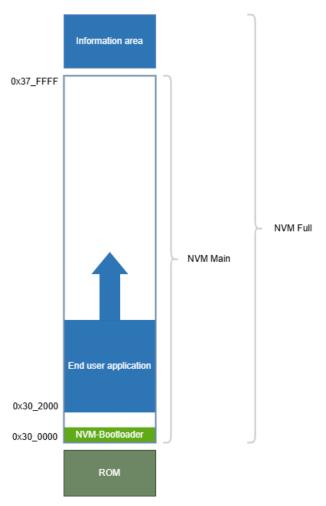

| 10.3.1.    | IROM                                     |     |

| 10.3.2.    | NVM Info Area                            |     |

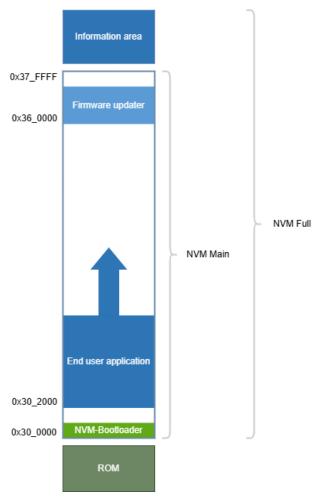

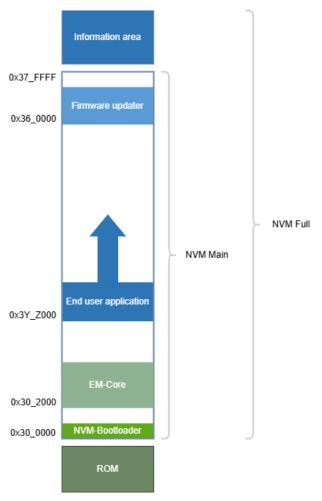

| 10.3.3.    | NVM Main Area                            | 83  |

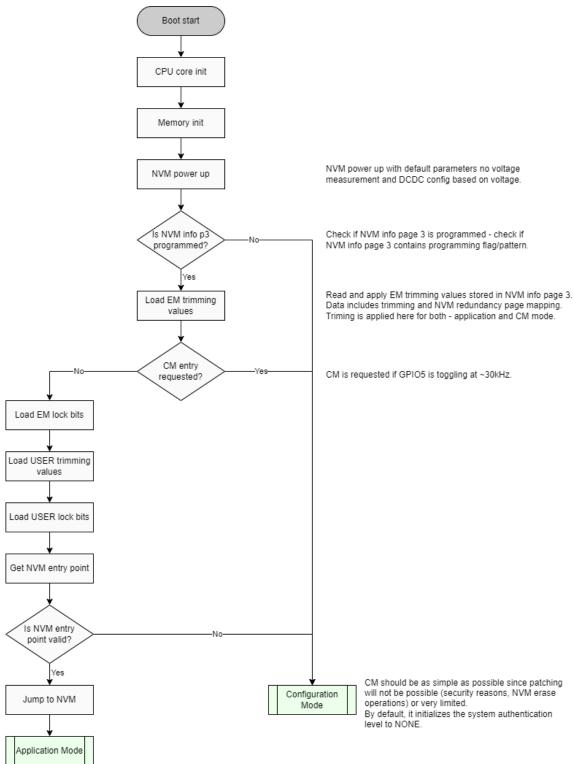

| 10.4. Boo  | T SEQUENCE                               | 84  |

| 10.4.1.    | ROM Boot Sequence                        |     |

| 10.4.2.    | NVM Boot Sequence                        |     |

| 10.5. CONF | FIGURATION MODE (ROM SW)                 |     |

| 10.5.1.    | CM Entering                              |     |

| 10.5.2.    | CM Operation                             |     |

| 10.5.3.    | CM Security                              | 87  |

|            | ICATION FRAMEWORK LAYER                  |     |

| 10.6.1.    | Real-Time Embedded Framework             |     |

| 10.6.2.    | Interrupt Handler                        |     |

| 10.6.3.    | Memory Manager                           |     |

| 10.6.4.    | NVM Memory Driver and Management         |     |

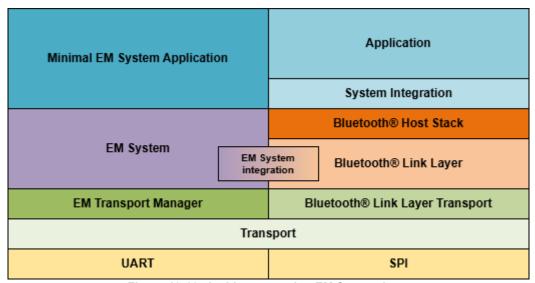

| 10.6.5.    | EM System                                | 92  |

| 10.6.6.    | EM Transport Manager                     | 94  |

| 10.7. HARD | DWARE ABSTRACTION LAYER                  |     |

| 10.7.1.    | Boot Sequencer                           |     |

| 10.7.2.    | Sleep Manager                            |     |

| 10.7.3.    | Voltage Monitor                          |     |

| 10.7.4.    | Device Drivers                           | 95  |

| 11. EM SY  | STEM COMMANDS AND EVENTS                 | QG  |

|            |                                          |     |

| 11.1. PACK | ET DESCRIPTION                           |     |

| 11.1.1.    | Packet Indicators                        |     |

| 11.1.2.    | Packet Formats                           |     |

| 11.1.3.    | Opcodes Format                           |     |

|            | System Commands                          |     |

| 11.2.1.    | Protected EM System (EMS) Commands       |     |

| 11.2.2.    | Backward compatibilty                    |     |

| 11.2.3.    | EMS General (EMSG) Commands              |     |

| 11.2.4.    | EMS Security (EMSS) Commands             | 102 |

| 11.2.5.    | EMS Radio Control (EMSRC) Commands       |     |

| 11.2.6.    | EMS Memory Management (EMSMM) Commands   |     |

| 11.2.7.    | EMS Register Management (EMSRM) Commands | 112 |

| 11.3. EM 9 | System Events                            |     |

| 11.3.1.    | EMS Active State Entered                 |     |

| 11.3.2.    | EMS Configuration Mode Entered           | 113 |

| 11.3.3.    | EMS HAL Notification                     |     |

| 11.4. HAR  | DWARE ERROR EVENT CODES                  | 113 |

| 12. TYPICA | AL APPLICATION                           | 114 |

|            |                                          |     |

|            | RENCE DESIGNS                            |     |

| 12.2. DEVE | ELOPMENT KIT                             | 116 |

| 13. ORDEF  | RING INFORMATION                         |     |

|            | AGING INFORMATION                        |     |

| 14. PACKA  | INFORMATION                              | 118 |

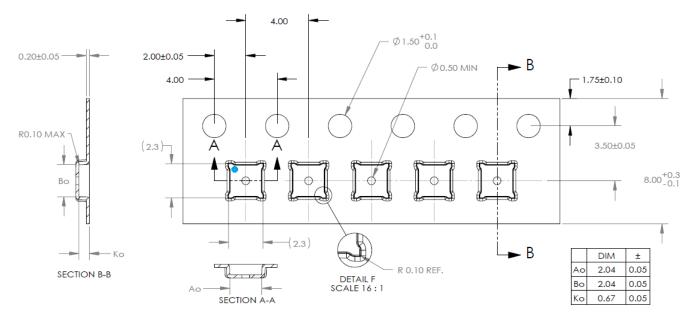

| 14.1. QFN  | PACKAGE INFORMATION                      | 118 |

| 14.1.1.    | QFN Package Marking                      | 119 |

| 14.2. WLC  | SP Package Information                   | 120 |

| 14.2.1.    | WLCSP Package Marking                    | 121 |

| 14.2.2.    | WLCSP Package Reflow                     | 121 |

| 14.3. DIE INFORMATION                                   | 122 |

|---------------------------------------------------------|-----|

| 15. DATASHEET VERSION HISTORY                           | 124 |

| 15.1. VERSION 4.5.3 (AUGUST 20 <sup>TH</sup> , 2025)    | 124 |

| 15.2. Version 4.5.2 (October 29 <sup>th</sup> , 2024)   |     |

| 15.3. Version 4.5.1 (December 18 <sup>TH</sup> , 2023)  |     |

| 15.4. VERSION 4.5.0 (SEPTEMBER 28 <sup>TH</sup> , 2023) | 125 |

| 15.5. VERSION 4.4.3 (SEPTEMBER 28 <sup>TH</sup> , 2023) | 125 |

| 15.6. VERSION 4.4.2 (SEPTEMBER 6 <sup>TH</sup> , 2023)  | 125 |

| 15.7. VERSION 4.4.1 (JUNE 30 <sup>TH</sup> , 2023)      |     |

| 15.8. VERSION 4.4.0 (FEBRUARY 23 <sup>RD</sup> , 2023)  | 126 |

| 15.9. VERSION 4.3.0 (NOVEMBER 4 <sup>TH</sup> , 2022)   | 126 |

| 15.10. VERSION 4.2.0 (AUGUST 31 <sup>ST</sup> , 2022)   | 126 |

| 15.11. VERSION 4.1.0 (APRIL 20 <sup>TH</sup> , 2022)    | 127 |

| 15.12. VERSION 3.2.0 (OCTOBER 27 <sup>TH</sup> , 2021)  |     |

| 15.13. VERSION 3.1.3 (JUNE 25 <sup>TH</sup> , 2021)     |     |

| 15.14. VERSION 3.0.2 (AUGUST 18 <sup>TH</sup> , 2020)   |     |

|                                                         |     |

# **LIST OF FIGURES**

| FIGURE 0-1: TYPICAL APPLICATION SCHEMATIC — BLUETOOTH® LE COMPANION IC TO ANY MCU OR ASIC               | 2  |

|---------------------------------------------------------------------------------------------------------|----|

| FIGURE 0-2: TYPICAL APPLICATION SCHEMATIC — EM9305 IN SOC MODE CONNECTED WITH PERIPHERALS               | 2  |

| FIGURE 0-3: TYPICAL APPLICATION SCHEMATIC — EM9305 IN SOC MODE POWERED FROM USB                         | 2  |

| FIGURE 1-1: BLOCK DIAGRAM CONFIGURED IN STEP-DOWN                                                       | 12 |

| FIGURE 1-2: HARDWARE ARCHITECTURE                                                                       | 13 |

| FIGURE 1-3: RF TRANSCEIVER ARCHITECTURE (SIMPLIFIED VIEW)                                               | 14 |

| FIGURE 1-4: DCDC STEP-UP CONFIGURATION                                                                  | 15 |

| FIGURE 1-5: DCDC STEP-DOWN CONFIGURATION                                                                | 15 |

| FIGURE 1-6: VOLTAGE MULTIPLIER CONFIGURATION                                                            | 17 |

| FIGURE 1-7: USB CONFIGURATION                                                                           | 17 |

| FIGURE 3-1: PIN LOCATION ON QFN PACKAGE (TOP/PCB VIEW)                                                  | 21 |

| FIGURE 3-2: BALL LOCATION ON WLCSP PACKAGE (TOP/PCB VIEW). BALL E1 IS REFERENCED AS (0, 0) IN TABLE 3-2 | 22 |

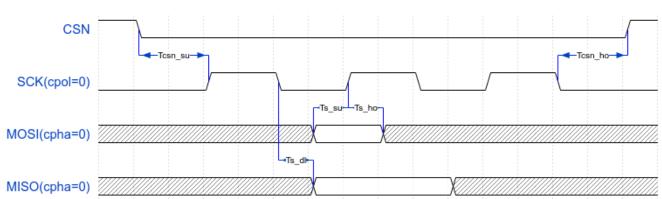

| FIGURE 4-1: SPI SLAVE TIMING DEFINITION                                                                 | 29 |

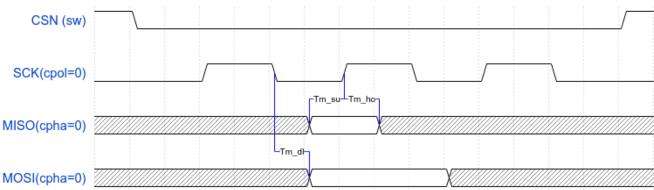

| FIGURE 4-2: SPI MASTER TIMING DEFINITION                                                                | 29 |

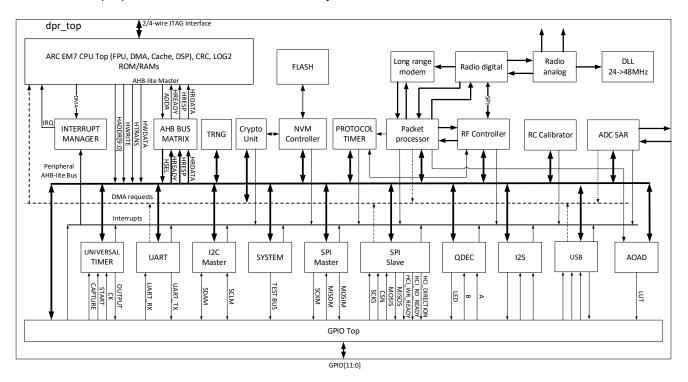

| FIGURE 5-1: BLOCK DIAGRAM OF THE DIGITAL PROCESSING.                                                    | 32 |

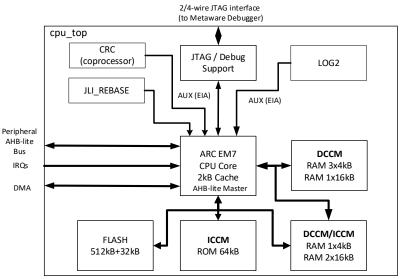

| FIGURE 5-2: TOP-LEVEL CPU BLOCK DIAGRAM                                                                 | 33 |

| FIGURE 5-3: MEMORY ARCHITECTURE AND INTERCONNECTION                                                     | 34 |

| FIGURE 5-4: AHB-FLASH INTERFACE                                                                         | 36 |

| FIGURE 6-1: LOGIC POWER DOMAINS                                                                         | 39 |

| FIGURE 6-2: POWER MODES TRANSITION DIAGRAM                                                              | 41 |

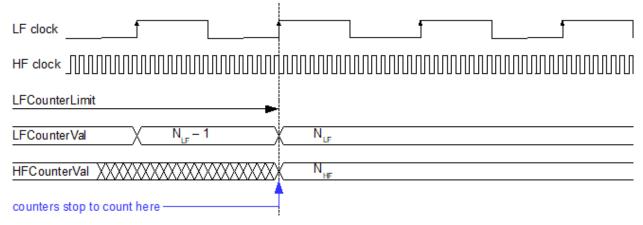

| FIGURE 6-3: LF CLOCK CALIBRATION                                                                        | 43 |

| FIGURE 7-1: BLOCK DIAGRAM OF THE TRANSCEIVER, INCLUDING THE FRONT-END AND THE MODEM                     | 44 |

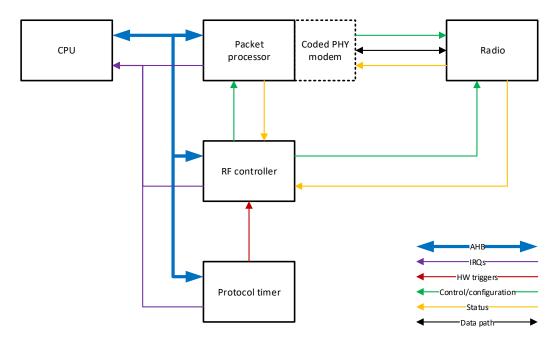

| FIGURE 7-2: PRINCIPAL CONNECTION BETWEEN THE RF CONTROLLER AND SURROUNDING BLOCKS                       | 45 |

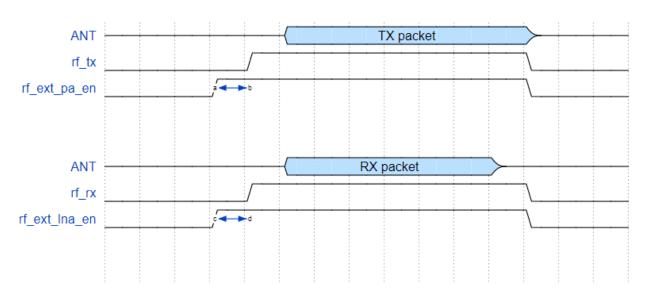

| FIGURE 7-3: EXTERNAL RF CONTROL TIMING                                                                  | 46 |

| FIGURE 7-4: GENERIC PACKET FORMAT                                                                       | 46 |

| FIGURE 7-5: PACKET FORMAT FOR BLUETOOTH® LE AND BLUETOOTH® LE 2M                                        | 47 |

| FIGURE 7-6: PACKET FORMAT FOR BLUETOOTH® LE CODED                                                       | 47 |

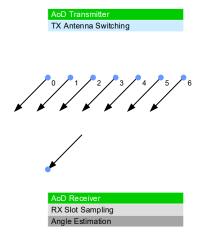

| FIGURE 7-7: ANGLE-OF-DEPARTURE (AOD) SYSTEM REPRESENTATION                                              | 47 |

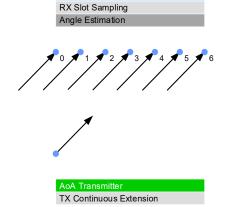

| FIGURE 7-8: ANGLE-OF-ARRIVAL (AOA) SYSTEM REPRESENTATION                                                |    |

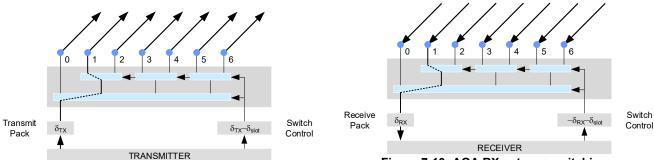

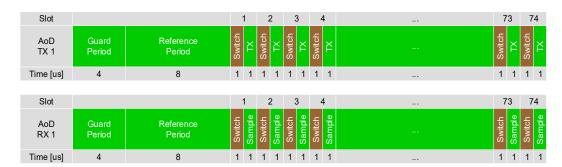

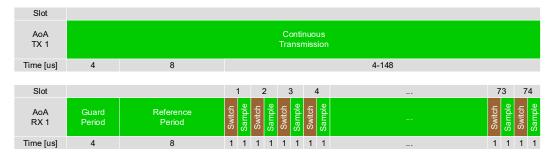

| FIGURE 7-9: AOD TX ANTENNA SWITCHING                                                                    | 48 |

| FIGURE 7-10: AOA RX ANTENNA SWITCHING                                                                   | 48 |

| FIGURE 7-11: TX CTE ANTENNA SWITCHING PACKET FORMAT FOR AOD WITH 1μS PERIOD                             | 48 |

| FIGURE 7-12: RX CTE ANTENNA SWITCHING PACKET FORMAT FOR AOA WITH 1μS PERIOD                             | 48 |

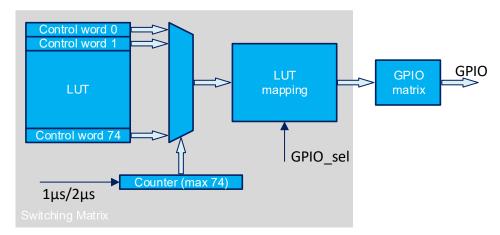

| FIGURE 7-13: SWITCHING MATRIX BLOCK DIAGRAM                                                             | 49 |

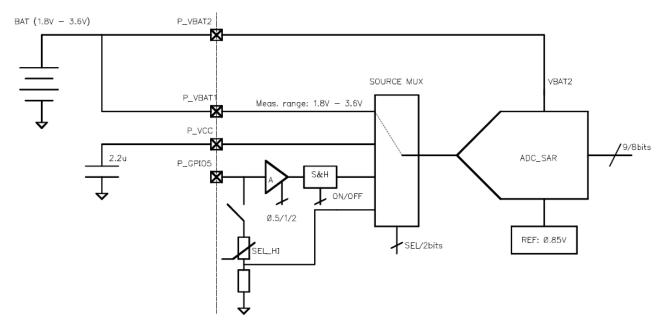

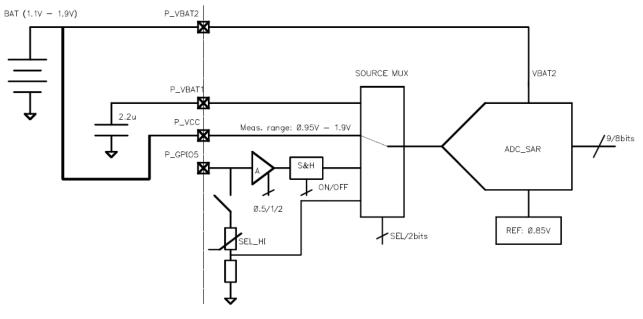

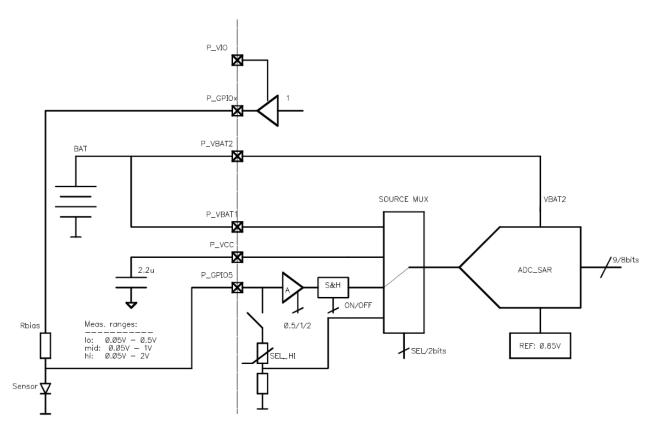

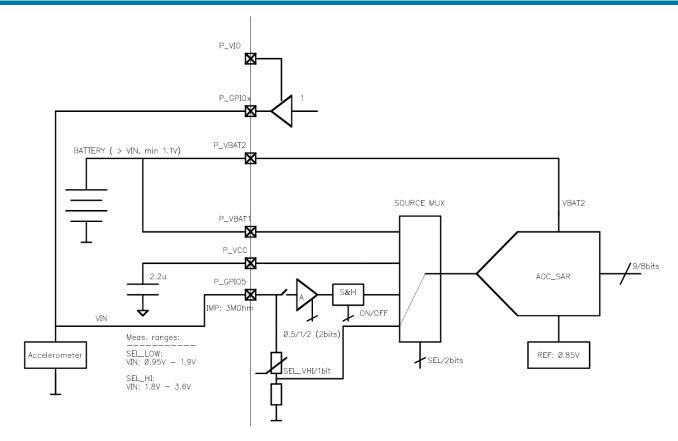

| FIGURE 8-1: ADC APPLICATION EXAMPLE: VBAT1 MEASUREMENT                                                  | 51 |

| FIGURE 8-2: ADC APPLICATION EXAMPLE: VCC MEASUREMENT                                                    | 52 |

| FIGURE 8-3: ADC APPLICATION EXAMPLE: GPIO5 MEASUREMENT WITH SAMPLE AND HOLD                             | 52 |

| FIGURE 8-4: ADC APPLICATION EXAMPLE: GPIO5 MEASUREMENT WITHOUT SAMPLE AND HOLD                          | 53 |

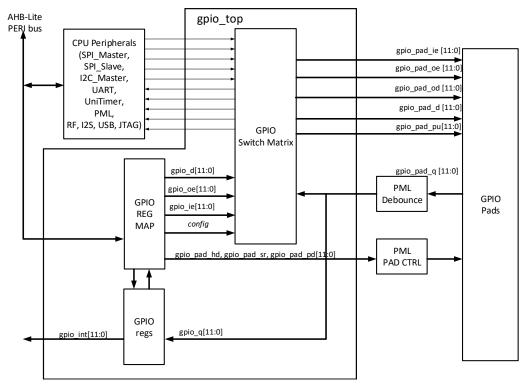

| FIGURE 8-5: GPIO BLOCK DIAGRAM                                                                          | 54 |

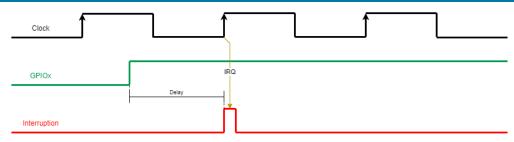

| FIGURE 8-6: GPIO INTERRUPTS SYNCHRONIZATION                                                             | 55 |

| FIGURE 8-7: GPIO WAKE-UP                                                                                | 55 |

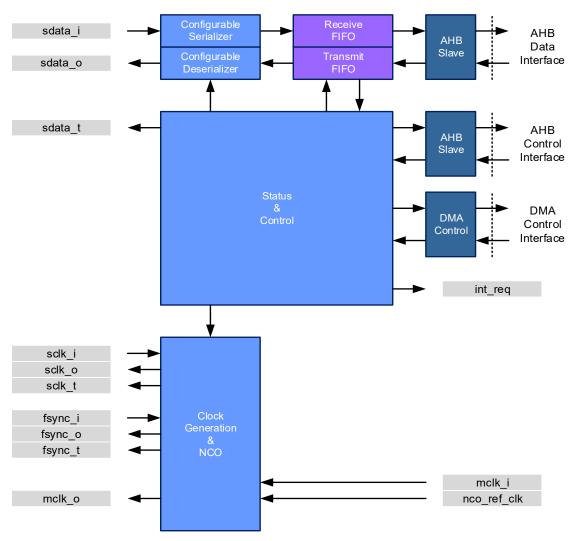

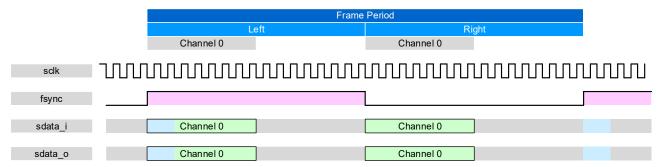

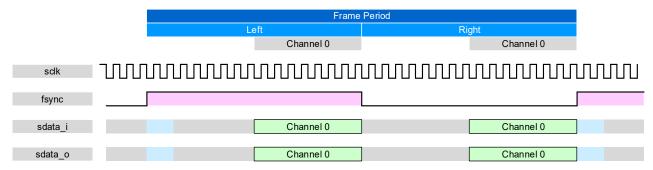

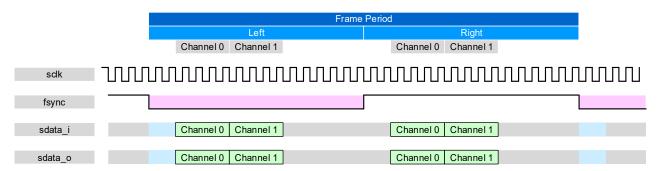

| FIGURE 8-8: ARCHITECTURE OF THE SERIAL AUDIO INTERFACE I2S/TDM                                          | 60 |

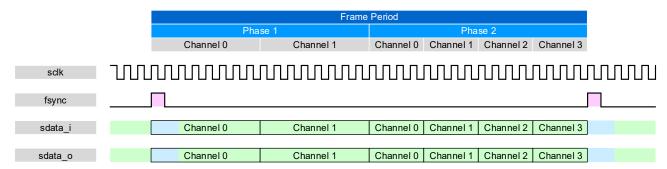

| FIGURE 8-9: TDM FRAME FORMAT                                                                            | 61 |

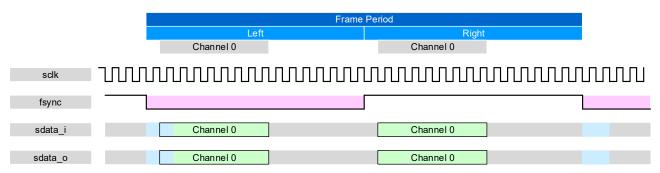

| FIGURE 8-10: I2S FRAME FORMAT                                                                           | 61 |

| FIGURE 8-11: LEFT-JUSTIFIED FRAME FORMAT                                                                | 61 |

| FIGURE 8-12: RIGHT-JUSTIFIED FRAME FORMAT                                                               | 61 |

| FIGURE 8-13: TDM IN I2S FRAME FORMAT                                                                    | 62 |

| FIGURE 8-14: JTAG (IEEE 1149.1) INTERFACE                                                               | 62 |

| FIGURE 8-15: CJTAG (IEEE 1149.7) INTERFACE                                                              | 62 |

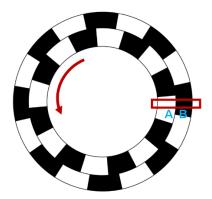

| FIGURE 8-16: ROTARY DECODER WITH CORRESPONDING LOGIC STATES FOR A AND B SIGNALS                         |    |

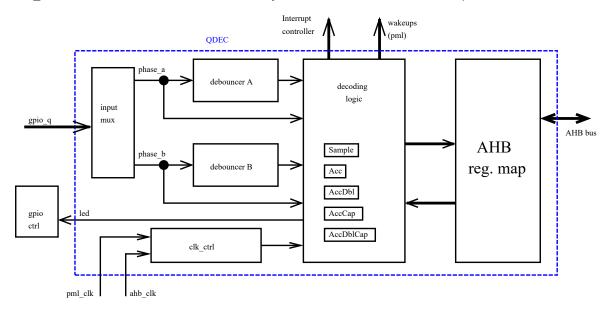

| FIGURE 8-17: QDEC BLOCK DIAGRAM                                                                         | 63 |

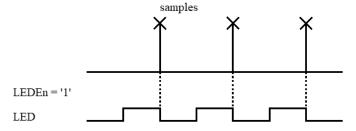

| FIGURE 8-18: QDEC LED ENABLE BEFORE SAMPLE                                                              |    |

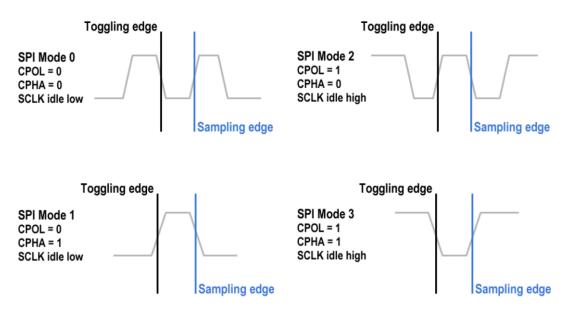

| FIGURE 8-19: SPI MODES                                                                                  |    |

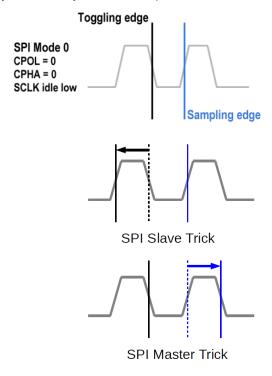

| FIGURE 8-20: SPI TRICK TO INCREASE MAXIMUM SPEED                                                        | 66 |

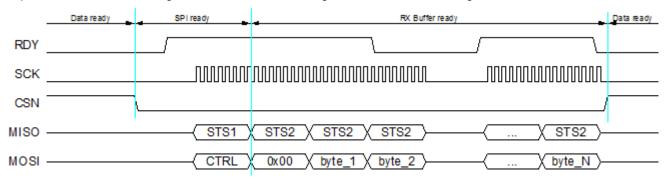

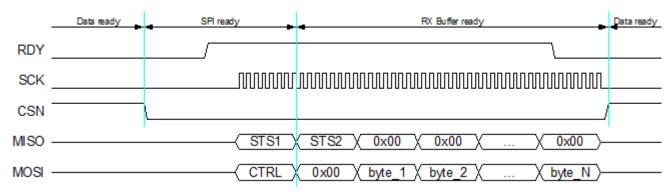

| FIGURE 8-21: SPI SLAVE WRITE TRANSACTION WITH ACTIVE FLOW CONTROL USING RDY                             | 68 |

| FIGURE 8-22: SPI CONTROL, SLAVE READY FOR TRANSACTIONS                                                               | 68  |

|----------------------------------------------------------------------------------------------------------------------|-----|

| FIGURE 8-23: SPI CONTROL, DATA READY IN RX BUFFER                                                                    | 69  |

| FIGURE 8-24: PROTOCOL TIMER AND SLEEP TIMER COOPERATION                                                              | 70  |

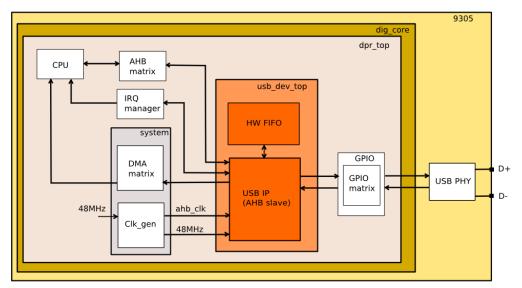

| Figure 8-25: USB system level integration                                                                            | 72  |

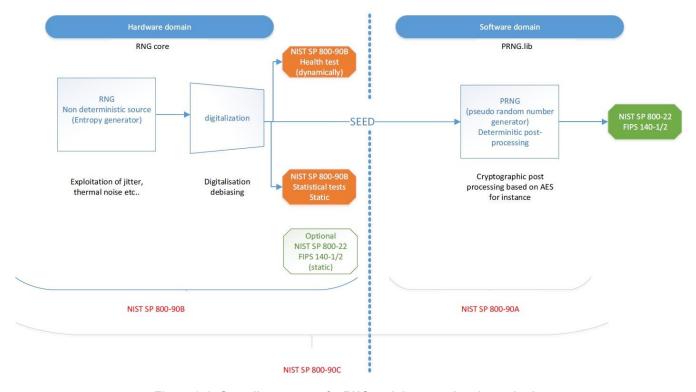

| FIGURE 9-1: OVERALL STRUCTURE OF A RNG AND THE ASSOCIATED STANDARDS                                                  | 73  |

| Figure 9-2: Process to write and read in the key container                                                           | 74  |

| Figure 9-3: 8 first keys life cycle                                                                                  | 75  |

| Figure 9-4: AES-based two-pass authentication                                                                        | 75  |

| Figure 10-1: Software architecture                                                                                   | 76  |

| Figure 10-2: RAM address space                                                                                       | 78  |

| Figure 10-3: Data address space and persistence strategy                                                             | 79  |

| FIGURE 10-4: SIMPLIFIED ROM AND NVM MAIN AREA LAYOUT                                                                 | 84  |

| FIGURE 10-5: READ AUX REGISTER COMMAND REJECTED FOR DEVICES WITH AUTHENTICATION IS ACTIVE                            | 85  |

| Figure 10-6: ROM boot sequence                                                                                       | 86  |

| Figure 10-7: Minimalistic NVM layout content                                                                         | 89  |

| FIGURE 10-8: NVM LAYOUT FOR FIRMWARE UPDATE OVER THE AIR                                                             | 90  |

| FIGURE 10-9: NVM LAYOUT CONTENT WITH EM-CORE                                                                         | 91  |

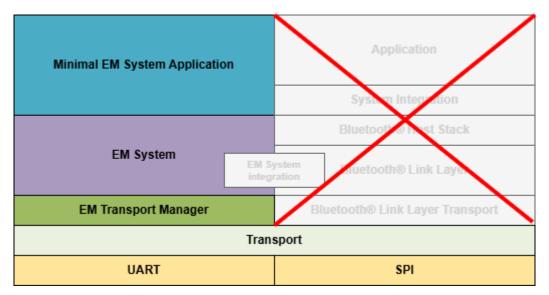

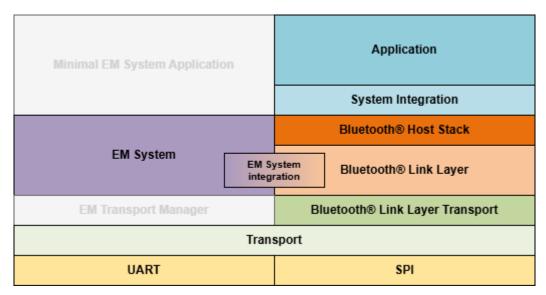

| FIGURE 10-10: ARCHITECTURE USING EM SYSTEM LAYER                                                                     | 92  |

| FIGURE 10-11: ARCHITECTURE USING EM SYSTEM LAYER IN CONFIGURATION MODE                                               | 93  |

| FIGURE 10-12: ARCHITECTURE USING EM SYSTEM LAYER IN APPLICATION MODE (WITH BLUETOOTH® LINK LAYER SW)                 | 93  |

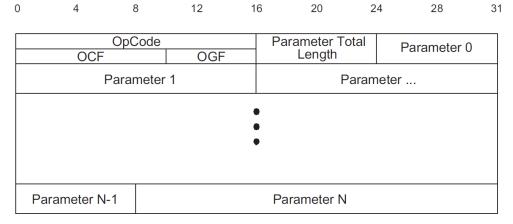

| FIGURE 11-1: HCI COMMAND PACKET FORMAT                                                                               |     |

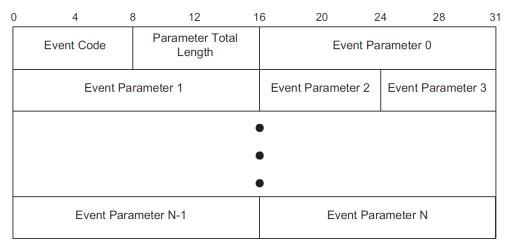

| FIGURE 11-2: HCI EVENT PACKET FORMAT                                                                                 | 96  |

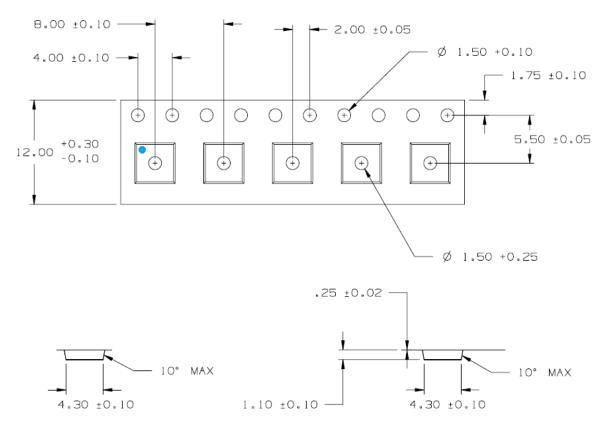

| Figure 12-1: General Reference Design Schematic                                                                      | 115 |

| FIGURE 12-2: EM9305 DEVELOPMENT KIT                                                                                  | 116 |

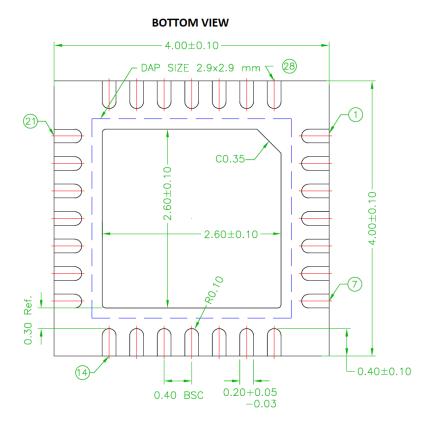

| FIGURE 14-1: QFN-28 MECHANICAL DRAWING (ALL DIMENSIONS ARE IN MILLIMETERS)                                           | 118 |

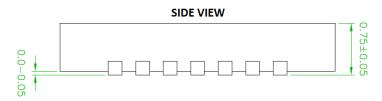

| FIGURE 14-2 TAPE & REEL DIAGRAM. BLUE DOT SHOWS PIN 1 ORIENTATION ON QFN TAPE (ALL DIMENSIONS ARE IN MILLIMETERS)    | 119 |

| FIGURE 14-3: WLCSP23 MECHANICAL DRAWING (ALL DIMENSIONS ARE IN MILLIMETERS)                                          | 120 |

| FIGURE 14-4 TAPE & REEL DIAGRAM. BLUE DOT SHOWS PIN A1 ORIENTATION ON WLCSP TAPE (ALL DIMENSIONS ARE IN MILLIMETERS) |     |

| FIGURE 14-5: WLCSP TEMPERATURE VS TIME REFLOW PROFILE                                                                |     |

| Figure 14-6: Pad location diagram                                                                                    | 122 |

# **LIST OF TABLES**

| Table 1-1: Power Management Configuration Options                                                                     | 16 |

|-----------------------------------------------------------------------------------------------------------------------|----|

| Table 1-2: Typical Battery Types                                                                                      | 16 |

| Table 1-3: Digital Interfaces                                                                                         | 18 |

| Table 3-1: Pin-out Description                                                                                        |    |

| Table 3-2: Ball position (top/PCB view) with reference to Figure 3-2                                                  | 22 |

| Table 4-1: Absolute Maximum Ratings                                                                                   |    |

| Table 4-2: General Operating Conditions                                                                               |    |

| TABLE 4-3: TYPICAL DC CURRENT, DCDC STEP-DOWN AND VOLTAGE MULTIPLIER CONFIGURATIONS AT 48MHz CPU SPEED                |    |

| Table 4-4: Supported data rates                                                                                       |    |

| Table 4-5: High Frequency Crystal Oscillator Specifications                                                           |    |

| Table 4-6: General transmitter characteristics                                                                        | 26 |

| Table 4-7: General receiver characteristics                                                                           | 26 |

| Table 4-8: GPIO pin characteristics                                                                                   |    |

| Table 4-9: Output parameters for I2C mode                                                                             | 27 |

| Table 4-10: Low Frequency Crystal Oscillator Specifications                                                           |    |

| Table 4-11: Start-up characteristics                                                                                  |    |

| Table 4-12: Timing Characteristics when changing mode                                                                 | 28 |

| Table 4-13: Timing Management of the RF controller                                                                    |    |

| Table 4-14: I2C timing parameters                                                                                     | 29 |

| Table 4-15: SPI timing specifications (load conditions: 15pf)                                                         | 30 |

| Table 4-16: NVM characteristics                                                                                       | 31 |

| Table 5-1: Memory map                                                                                                 | 35 |

| Table 6-1: Main supply domains                                                                                        | 38 |

| Table 6-2: Logic power domains                                                                                        | 39 |

| Table 6-3: SVLD supply domains                                                                                        | 39 |

| Table 6-4: Power modes                                                                                                | 40 |

| Table 6-5: Reset sources                                                                                              | 42 |

| Table 6-6: Main system clock sources                                                                                  | 42 |

| Table 6-7: LF XTAL modes                                                                                              | 42 |

| Table 6-8: Counters used for RC calibration                                                                           | 43 |

| Table 7-1: RF controller interfaces                                                                                   | 45 |

| Table 8-1: Peripherals Functions                                                                                      |    |

| Table 8-2: ADC specifications                                                                                         | 50 |

| Table 8-3: ADC sources and measurement ranges                                                                         |    |

| Table 8-4: GPIO Status after SW boot in Configuration Mode: SPI Slave (green cells) – GPIO (purple cells)             | 55 |

| Table 8-5: GPIO configuration                                                                                         |    |

| Table 8-6: SPI Slave with high drive capability (green cells) – SPI Master (purple cells) combination on WLCSP device |    |

| Table 8-7: SPI Master with high drive capability (green cells) – SPI Slave (purple cells) combination on WLCSP device |    |

| Table 8-8: SPI Master with high drive capability (green cells) – UART (purple cells) combination on WLCSP device      | 58 |

| Table 8-9: SPI Slave with high drive capability (green cells) — UART (purple cells) combination on WLCSP device       |    |

| Table 8-10: I2S/TDM (GREEN CELLS) – I2C MASTER (PURPLE CELLS) COMBINATION ON WLCSP DEVICE                             |    |

| Table 8-11: SPI Master with high drive capability (green cells) – I2S/TDM (purple cells) combination on WLCSP device  | 58 |

| Table 8-12: SPI Slave with high drive capability (green cells) – I2S/TDM (purple cells) combination on WLCSP device   |    |

| Table 8-13: Movement detection depending on A, B signals                                                              | 64 |

| Table 8-14: QDEC sampling periods                                                                                     |    |

| Table 8-15: QDEC report period values                                                                                 |    |

| Table 10-1: NVM memory main characteristics                                                                           |    |

| Table 10-2: NVM Info area organization                                                                                |    |

| Table 10-3: NVM info area page 3 - EM configuration data                                                              | 82 |

| Table 10-4: NVM info area page 2 - User configuration data                                                            | 83 |

| Table 10-5: Device drivers list                                                                                       |    |

| Table 11-1: HCI Packet Indicators                                                                                     |    |

| Table 11-2: Opcode format                                                                                             |    |

| Table 11-3: EM System Commands Backward Compatible                                                                    |    |

| Table 11-4: EM System General (EMSG) commands overview                                                                | 98 |

| TABLE 11-5: EM SYSTEM SECURITY (EMSS) COMMANDS OVERVIEW                             | 102 |

|-------------------------------------------------------------------------------------|-----|

| TABLE 11-6: EM SYSTEM RADIO CONTROL (EMSRC) COMMANDS OVERVIEW                       | 104 |

| Table 11-7: EM System Memory Management (EMSMM) commands overview                   | 109 |

| TABLE 11-8: EM SYSTEM REGISTER MANAGEMENT (EMSRM) COMMANDS OVERVIEW                 | 112 |

| Table 11-9: EM System Events overview                                               | 112 |

| TABLE 12-1: RECOMMENDED COMPONENTS LIST AND THEIR SIZE                              | 114 |

| TABLE 12-2: COMPONENTS SELECTION FOR THE MATCHING NETWORK ON QFN REFERENCE DESIGN   | 114 |

| TABLE 12-3: COMPONENTS SELECTION FOR THE MATCHING NETWORK ON WLCSP REFERENCE DESIGN | 114 |

| Table 12-4: Power management components for the different configurations            | 115 |

| Table 13-1: EM9305 versions and ordering information                                | 117 |

| Table 14-1: Package marking information for QFN device                              | 119 |

| TABLE 14-2: PACKAGE MARKING INFORMATION FOR WLCSP DEVICE                            |     |

| Table 14-3: WLCSP Reflow Specifications                                             |     |

| Table 14-4: Pad position (top view)                                                 | 123 |

# 1. PRODUCT OVERVIEW

#### 1.1. INTRODUCTION

The EM9305 is a universal 2.4 GHz RF system on chip with the following target applications:

- Bluetooth® LE Controller Mode

- o Host connect to controller via Host Controller Interface (HCI)

- o HCI implemented via SPI or UART transport layer

- Link laver implemented in flash

- Up to 4 simultaneous connections supported (Contact EM Microelectronic for specific request)

- Long packet lengths (payload up to 255 bytes) supported

## Bluetooth® LE Application Mode

- Application hosting

- Low energy applications such as proximity or sensor beacons using Bluetooth® LE are easily implemented

- Connections to digital peripherals through SPI, I2C, I2S/TDM, UART, and GPIOs allow for data collection, storage, or display for example.

- Software development platform

- Application Program Interface (API) available for all levels of firmware

- Full featured development tools (Metaware/MetawareLite)

- Development and debugging using JTAG or cJTAG interface

- Programs can be developed in flash

- Programs stored in flash will execute from RAM or flash (through a cache system)

- All Controller Mode and Companion Mode features supported

- USB transport Mode

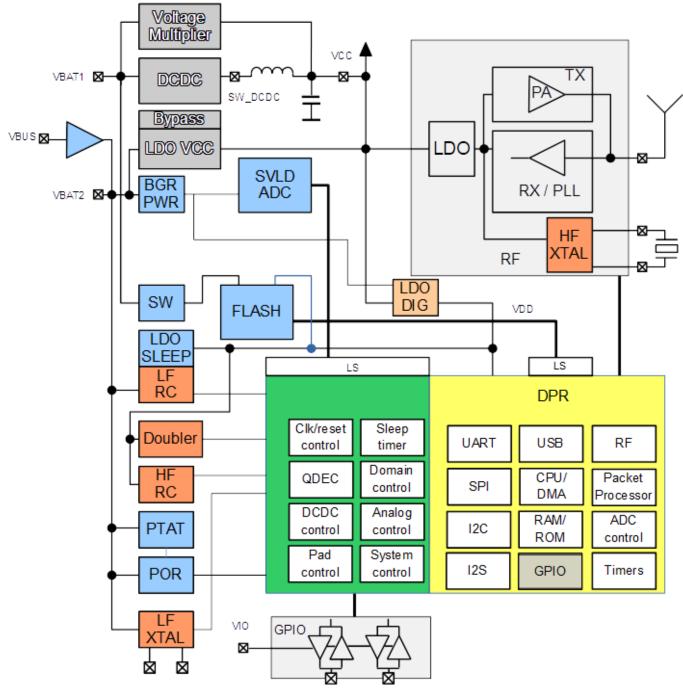

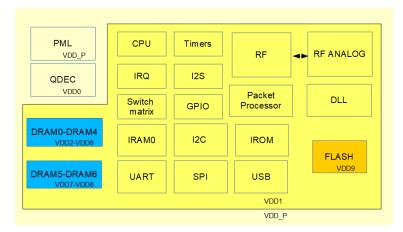

A block diagram of the EM9305 is shown in Figure 1-1 with the power management configured in DCDC Step-Down Configuration. The main blocks are the Digital Processing Block (DPR), the RF block, the Power Management Logic (PML), the Power Management Blocks, and the General Purpose Input Output blocks (GPIO).

The chip architecture is briefly described in Section 1.2. The GPIO configuration is described in Section 1.3.

The package pins are described in Section 3.

A more detailed description of the digital processing block can be found in Section 5. A 32-bit CPU efficiently controls the movement of data between the RF modem, memory, and the digital interfaces. Digital interfaces include UART, SPI, I2C and I2S, which are mapped to GPIO as required by the application. Other peripherals include an interrupt manager, timers, and encryption engines.

An advanced power management system is described in Section 6. Power consumption and battery life are optimized in all conditions. Most common 1.5V and 3.0V primary battery cell technologies are directly supported including Lithium, Alkaline, Zinc-Air and Silver Oxide. For 1.5V batteries, the on-chip DCDC converter steps up the voltage to the required internal levels. An inductor-less voltage multiplier also allows for lower BOM. For 3.0V batteries, the on-chip DCDC converter steps the voltage down internally for efficient power consumption. Very few external components are necessary for the DCDC converter operation; however, it is also possible to operate with an internal LDO to minimize component count even further.

The RF modem is described in Section 7. A very sensitive RF front-end achieves a -97dBm typical sensitivity for 1Mbps operation with 37-byte payloads, while dissipating very low current. The efficient transmitter has programmable RF power levels from -57dBm up to +10dBm are possible. A connection to a 50-ohm antenna needs to be done with an appropriate matching circuit. Fast mode transition times and extremely low sleep current (225nA) enable very low energy application implementations.

Section 8 is describing all the peripherals and interfaces of the EM9305.

The security features, the security concept and the product life cycle are described in Section 9.

The embedded firmware is described in Section 10 and Section 11. The firmware is partitioned between flash and ROM to optimize for future proofing. A scheduler is used to manage priorities, and memory manager is used to optimize power consumption. The state can be retained in retention memory selectable from a minimum of 4kB to optimize features versus memory leakage. The flash memory is used to store trimming, unique identification numbers, protocol, stack, profiles, patches, and applications. The firmware can be updated or "patched" through SPI, UART, or over-the-air (FOTA). Patches can be loaded into and executed from flash. A jump-table system allows for managing updates.

The reference schematics are described in Section 12 with required and optional external components.

Ordering information and packaging options are described in Sections 13 and 14. Several types are offered for various application constraints. A wafer chip-scale package (WLCSP23) is offered for a minimum PCB footprint 1.8mm x 1.8mm; a QFN-28 package compatible with standard PCB technology is offered with additional GPIOs; and bare die in wafer format is offered for i.e. chip-on-board (COB) applications. Other packages are available upon request.

Figure 1-1: Block Diagram configured in Step-Down

# 1.2. CHIP ARCHITECTURE

## 1.2.1. MCU AND DIGITAL ARCHITECTURE

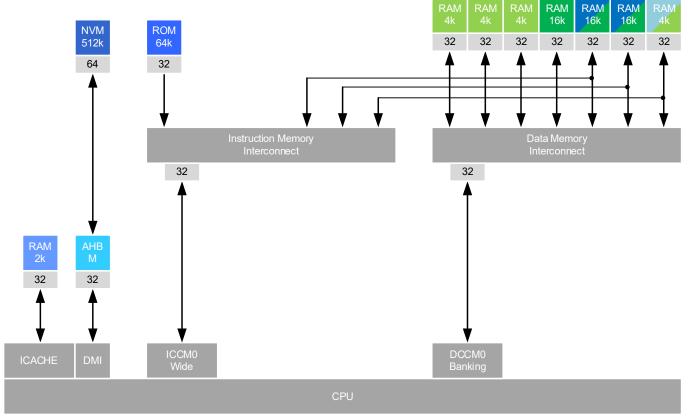

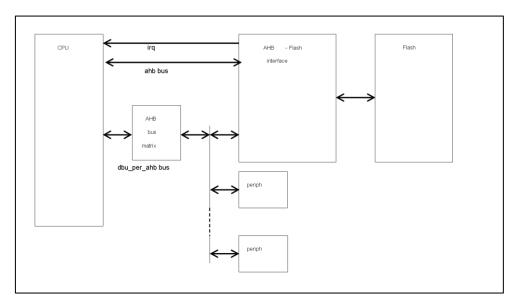

In Figure 1-2, the hardware architecture is shown. A 32-bit MCU efficiently controls the movement of data between the RF modem, memory, and the digital interfaces. The 32-bit MCU includes a digital signal-processing unit (DSP) and a floating-point unit (FPU) for efficient implementation of signal processing algorithms. A CRC coprocessor is also included for efficient verification of program memory. Memories are included for the following functions:

- ROM (64kB) used mainly for the boot

- RAM (64kB) used for application development and for data

- o All 64kB are retainable starting from a minimum of 4kB

- All 64kB can be used for data (DRAM)

- o Up to 36kB can be used for instructions (IRAM) if not used for data

- Flash (512kB) used for data, protocol, stack, profiles, and applications

- The architecture includes also an additional 32kB as information area. This area is used for trimming as well.

• Cache (2kB) – used to optimize code access in flash

Figure 1-2: Hardware Architecture

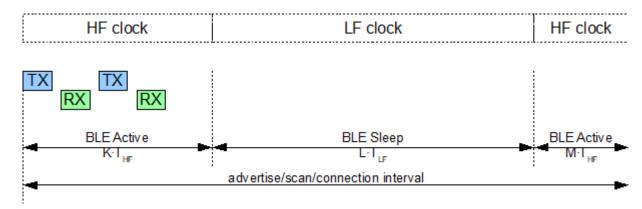

The memory architecture is divided into several different power domains for power consumption optimizations. When a memory is not being used, it can be switched off to reduce current consumption. During Bluetooth® connected sleep mode the entire MCU subsystem can be shut off and only the power management system and required state retention memories (if any) need to be powered. The power management system will properly wake up the MCU subsystem when it is needed. The RF modem is turned on and off as needed in order to minimize energy consumption.

Digital interfaces including UART, SPI master/slave, I2S master/slave and I2C master are mapped to GPIO as required by the application. When the chip is used as a peripheral to a host application, then the SPI slave and UART can be used for communication. The standard Host-Controller Interface (HCI) is implemented for communicating with the link layer. When the chip is used as an application host, then the SPI master or I2C master can be used to talk with most standard digital peripherals. Other peripherals include an interrupt manager and two timers for low power implementations, and an AES-128 encryption engine for security implementation. A NIST compliant true random number generator is also included for key generation.

#### 1.2.2. SOFTWARE ARCHITECTURE

The software architecture is described in detail in Section 10 and Section 11. The firmware is implemented in a power efficient manner using a basic scheduler and memory manager. The EM9305 implements a Bluetooth® Core 5.4 compliant link layer at the bottom of the stack and accessed through the standard HCI interface. Peripherals are accessed through hardware drivers. Bluetooth® HCI commands are implemented and additionally some vendor specific commands are implemented. The link layer is designed to optimize power consumption in each role. The CPU is normally halted and is only activated when a task needs to be accomplished. When sleeping, states and connection information are properly stored in the retention memory and all other memories and peripherals are turned off. A low power timer is used to properly wake up the system. The EM9305 is certified by the Bluetooth® SIG as Bluetooth® Core 5.4 Controller Subsystem.

The Bluetooth® LE stack is accessed through an Application Programming Interface (API) in application mode. The stack includes the L2CAP, Security Manager, ATT, GAP, and GATT. Standard Bluetooth® profiles such as Proximity and Find-Me are also included, as well as proprietary data-exchange and Firmware-Over-the-Air updating procedures to help manage data and program transfer.

The EM9305 can be customized using the on-chip flash memory. Specific Bluetooth® profiles can be loaded depending on the application. Simple applications can be implemented including sensor interfaces. Package configuration, production trim parameters and unique identification numbers can also be stored here.

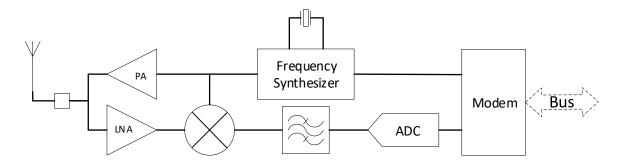

# 1.2.3. RF TRANSCEIVER OVERVIEW

The RF transceiver exceeds the specifications and requirements of the Bluetooth® Core 5.4 specification.

The main features of the RF transceiver are the following:

• Ultra-low power: The peak current in receive mode is 3.1mA and in transmit mode is 3.4mA at 0dBm and 3.0V in DCDC Step-Down Configuration at room temperature.

- Excellent RF performance: including -97dBm sensitivity for 1Mbps operation with 37-byte payload and a programmable output power range from -33dBm to +10dBm

- Low voltage: Operation from 3.6V down to 1.1V

- Very high degree of integration: small footprint with few external components

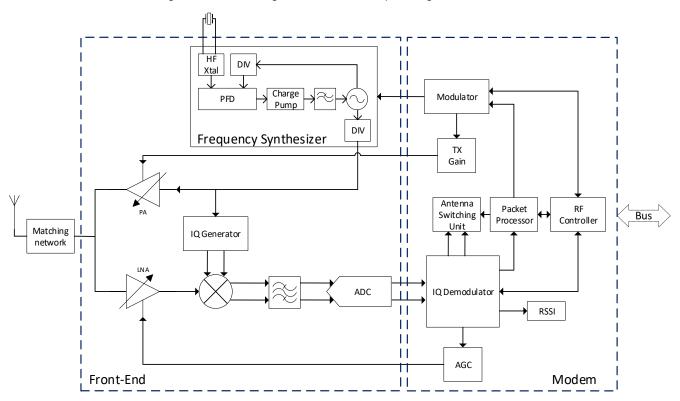

The RF transceiver block diagram is shown in Figure 1-3.

Figure 1-3: RF Transceiver Architecture (Simplified View)

The RF transceiver is divided into an analog/RF part and a digital part. The analog/RF part consists of the RX chain from LNA to ADC, the TX chain from DAC to the PA and the synthesizer subsystem that generates the LO frequency. The digital block consists of the modulator, demodulator, all calibration engines for radio optimization, timing sequencer for TX and RX and the register interface.

The Receiver chain has a low-IF architecture. The Transmitter has a dual point modulation architecture. The Synthesizer is a Frac-N PLL to generate the required LO frequency. All the blocks are optimized for lower current consumption. The RX and TX chains have multiple pre-burst calibrations that help achieve superior performance. The timing sequencer controls all pre-burst calibrations.

The RF transceiver is detailed in Section 7.

#### 1.2.4. POWER MANAGEMENT OVERVIEW

An advanced power management system is implemented on the EM9305. Key low-power circuits include a configurable and highly efficient DCDC converter, low noise bandgap references, low dropout regulators (LDOs), a high frequency RC oscillator for efficient MCU operation, and a high accuracy, low frequency, RC oscillator for sleep mode control. A sophisticated digital control system optimizes power consumption and battery life in all conditions. Several power management configurations are possible. Four of those are described here: DCDC Step-Up, DCDC Step-Down, Voltage multiplier and USB. The configuration is automatically detected by EM9305 from the PCB.

The most common application configurations are DCDC Step-Up and DCDC Step-Down. Depending on the battery voltage, these configurations allow for higher efficiency. Note that in the WLCSP package, VBAT2 and VIO are internally shorted together.

In Figure 1-4, DCDC Step-Up Configuration, a typical arrangement is shown for connecting a <u>1.5V battery</u> (1 Alkaline, Zinc Air or Silver Oxide cell, for example) to the EM9305 and an external 1.5V MCU.

The battery is applied to VCC, which is the main supply for the IC including the RF portion, and VBAT2, which powers key analog circuits in the power management. Using the SW pin, a coil and capacitor, the DCDC converter steps up the battery voltage to generate 1.7V on the VBAT1 pin to supply the flash. During sleep mode, the DCDC operation is off.

In Figure 1-5, DCDC Step-Down Configuration, a typical arrangement is shown for connecting a <u>3V battery</u> (1 Lithium or 2 Alkaline cells, for example) to the EM9305 and an external 3V MCU.

The battery is applied to VBAT1, which powers the DCDC converter, and VBAT2, which powers key analog circuits in the power management. Using the SW pin, a coil and capacitor, the DCDC converter efficiently steps down the battery voltage to generate 1.15V on the VCC pin. This is the main supply voltage for the rest of the IC during normal operation. During sleep mode, the DCDC operation is off and an optional charging circuit is used to maintain VCC.

Figure 1-4: DCDC Step-Up Configuration

Figure 1-5: DCDC Step-Down Configuration

Other configurations are possible in order to minimize the number of external components.

For example, the Figure 1-6, Voltage Multiplier Configuration, shows a typical arrangement for connecting a <u>1.5V battery</u>. VBAT1 voltage is generated by the capacitor multiplier from VBAT2. The first capacitor is internal. The multiplier is enabled/disabled by SW according to NVM usage. This configuration is slightly less efficient than the step-up configuration.

A similar configuration for higher battery voltage is possible (Direct Power configuration). Please contact EM Microelectronic for more information.

An additional configuration is shown in Figure 1-7, where the chip can directly be powered by a USB port applied on VBUS. An internal LDO is then used to generate 1.15V on the VCC pin. The DCDC converter is not used in this arrangement and is turned off. The external  $1\Omega$  resistor forms a supply voltage filter together with the capacitor. This will limit the supply slew-rate. Without it and with a fast-rising USB supply, transient overvoltage can occur inside the EM9305. In case the USB supply slew-rate is proven to be lower than  $50V/\mu$ s, then the resistor can be dropped.

Other configurations could be possible, but please review with EM Microelectronic before proceeding.

A summary of some configuration options and voltage ranges are shown in Table 1-1 (including USB described below). The external supply is coming from the VBAT2 or VBUS in the case of USB mode.

**Table 1-1: Power Management Configuration Options**

| CONFIGURATION           | VBUS         | VBAT1                         | VBAT2           | VCC                        |

|-------------------------|--------------|-------------------------------|-----------------|----------------------------|

| DCDC Step-up            | GND          | 1.9V from internal DCDC       | 1.1V - 1.9V     | VBAT2                      |

| Voltage multiplier GND  |              | 1.9V from voltage multiplier  | 1.1V - 1.9V     | VBAT2                      |

|                         |              | >1.9V from voltage multiplier | 1.9V - 2.5V     |                            |

| DCDC Step-down          | GND          | VBAT2                         | 1.9V - 3.6V     | Internal voltage from DCDC |

| Direct Power (DCDC off) | GND          | VBAT2                         | 1.9V - 3.6V     | Internal voltage from LDO  |

| USB <sup>1</sup>        | 4.4V – 5.25V | VBAT2                         | Internal buffer | Internal voltage from LDO  |

If VIO is not directly connected to VBAT1/VBAT2, the condition VIO≥VBAT2 must be fulfilled.

See section 4.2 for the minimal battery supply voltage for RF operations.

The EM9305 can directly be used with the battery types listed in Table 1-2, for example. Most common 1.5V and 3.0V primary battery cell technologies are directly supported including Lithium, Alkaline, Zinc-Air and Silver Oxide. Other battery types are also supported, for example carbon-printed batteries, but additional decoupling capacitors may be necessary to supply the peak current without the battery level decreasing below the minimum voltage.

The USB supply range shall be maintained between the values indicated in Table 1-1.

**Table 1-2: Typical Battery Types**

| TYPE                                        | NOMINAL<br>VOLTAGE (V) | MINIMUM<br>VOLTAGE (V) | CAPACITY (mAh) |

|---------------------------------------------|------------------------|------------------------|----------------|

| CR1225/CR2032<br>Li/MnO <sub>2</sub>        | 3.0                    | 2.0                    | 48/225         |

| LR44/AAA<br>Alkaline (Zn/MnO <sub>2</sub> ) | 1.5                    | 0.9                    | 200/1100       |

| Zinc Air<br>ZA675                           | 1.4                    | 1.1                    | 650            |

| Silver Oxide (Zn/Ag <sub>2</sub> O)<br>357  | 1.55                   | 1.2                    | 190            |

<sup>&</sup>lt;sup>1</sup> Only on QFN/die.

Figure 1-6: Voltage Multiplier Configuration

Figure 1-7: USB configuration

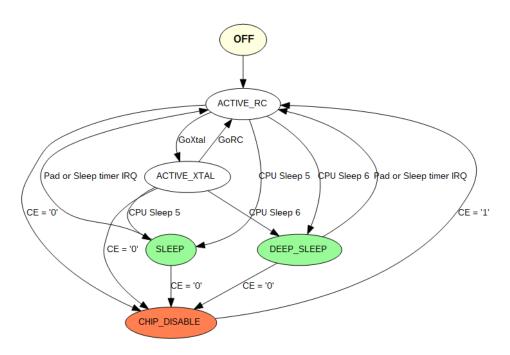

#### 1.2.5. OPERATING MODES

The chip has several modes of operation including several active, standby and sleep modes. These modes are described in detail in Section 6.4. Power consumption is optimized in each of these modes. The lowest power mode while maintaining an active connection dissipates 320nA with 4kB RAM in retention state if a 32kHz crystal is used, or 585nA if the internal sleep RC oscillator is used. Additionally, a deep sleep mode is provided with typical current consumption of 200nA, and a chip disable mode is provided with typical current consumption below 10nA.

Note that special circuitry is added to keep peak currents to the battery typically less than 12.5mA when transmit power is set to 0dBm or lower.

## 1.3. GPIO CONFIGURATION

The EM9305 has the digital serial interfaces listed in Table 1-3, and a complete function list shown in Table 8-1. These interfaces are available through General Purpose I/O pins (GPIO). These include SPI slave and a UART for an HCI application interface, test interface and for debug. An SPI master and I2C master are provided for interfacing to external memory or digital sensors for beacon type applications, for example. A JTAG interface is provided for debug. An I2S interface is also provided for audio streaming applications.

Table 1-3: Digital Interfaces

| Table 1-3. Digital interfaces                                                                        |                              |                                                           |  |  |

|------------------------------------------------------------------------------------------------------|------------------------------|-----------------------------------------------------------|--|--|

| INTERFACE                                                                                            | PADS                         | COMMENT                                                   |  |  |

| HCI/ SPI Slave 24 MHz @ VBAT>=1.9V 16 MHz @ VBAT < 1.9V 5 wires, 8-bit Flow control on dedicated pad | Programmable                 | HCI application default interface                         |  |  |

| UART, max 1.84Mbps                                                                                   | Programmable                 | HCl test interface, debug interface                       |  |  |

| SPI Master<br>24 MHz @ VBAT>=1.9V<br>16 MHz @ VBAT < 1.9V<br>3 or 4 wires, 8-bit                     | Programmable                 |                                                           |  |  |

| I2C Master<br>Standard (up to 100kbps)<br>Fast (up to 400kbps)                                       | Programmable                 | Filters and delay lines out of pads                       |  |  |

| I2S/TDM                                                                                              | Programmable                 |                                                           |  |  |

| JTAG, cJTAG                                                                                          | GPIO8, GPIO9, GPIO10, GPIO11 | Conventional 4-pin and compact 2-pin interfaces supported |  |  |

| USB 2.0, 12Mbps (Full Speed)                                                                         | GPIO6, GPIO7                 | Only on QFN package or die                                |  |  |

# 1.4. RELATED DOCUMENTS

The EM9305 was designed to comply with the following Bluetooth® specifications published by the *Bluetooth® Special Interest Group (SIG)* on http://www.bluetooth.org:

- Bluetooth® Core Specification, Version 5.4, Bluetooth® SIG, 31.01.2023

- Bluetooth® RF PHY Test Specification, p19, Bluetooth® SIG, 07.02.2023

- Bluetooth® Link Layer Test Specification, p21, Bluetooth® SIG, 07.02.2023

- Bluetooth® Host Controller Interface (HCI), p32, Bluetooth® SIG, 07.02.2023

Customers are, however, required to test the compliance of their final systems incorporating or embedding the EM9305 with these or other standards as they may apply and to obtain all necessary licenses and authorizations.

Other standards have also been taken into account in order to have a more generic multi-protocol support. Contact EM Microelectronic for more information.

# 2. HANDLING PROCEDURES

This device has built-in protection against high static voltages or electric fields; however, anti-static precautions must be taken as for any other CMOS component.

Unless otherwise specified, proper operation can only occur when all terminal voltages are kept within the voltage range. Unused inputs must always be tied to a defined logic voltage level unless otherwise specified.

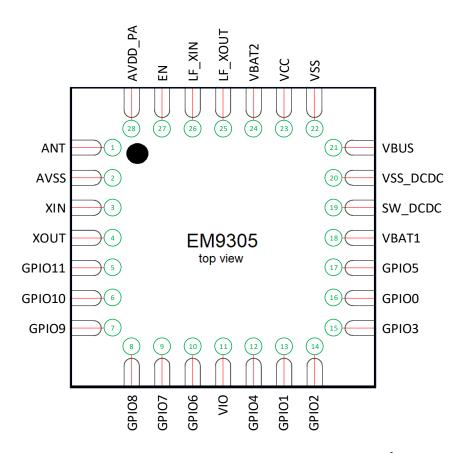

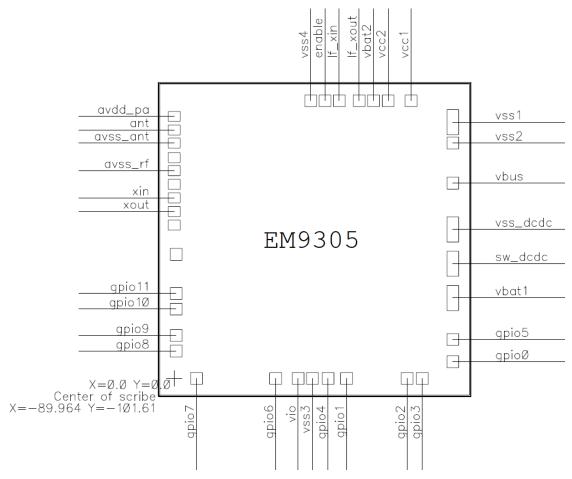

# 3. PIN DESCRIPTION

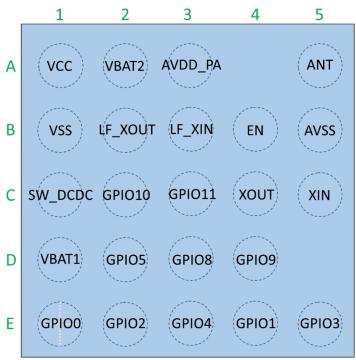

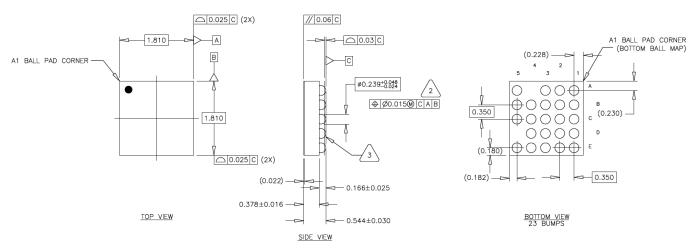

The pins of the EM9305 are described in Table 3-1. For the QFN-28 package, the 28 pins are also shown in Figure 3-1. For the WLCSP-23, 23 pins of the 5x5 array are used, as shown in Figure 3-2. The die information can be found in Section 14.3.

Analog pins include voltage supply pins, pins for crystal oscillators, and an antenna pin for the RF. Power is supplied through VBAT1, VBAT2, VIO, and VCC depending on the power management configuration described in Section 1.2.4. The ground is connected to the various ground pins. Impedance of these connections should be minimized for low noise performance. Ideally, they should be connected directly to a ground plane on the PCB using multiple vias where possible. Two pins are provided for the 48MHz crystal (XIN, XOUT) and two are provided for the optional 32kHz crystal (LF\_XIN, LF\_XOUT). If there is already a 32kHz crystal in the system, the LF\_XIN pin can be used to receive a reference signal. The RF antenna is connected to the ANT pin.

Digital pins include general-purpose I/O pins (GPIO) and a dedicated input pin for chip enable. There are 12 GPIO pins available on the QFN-28 package and in die form. There are 10 GPIO available on the WLCSP-23. Configuration of the GPIO is described in Section 8.2. The chip enable pin (EN) is provided to achieve the lowest possible power consumption (less than 10nA) of the device. The chip is not operational when this pin is low, and then it is initialized when this pin is raised high. VIO supplies the GPIO pins. VBUS is used only for the USB supply mode.

Table 3-1: Pin-out Description

| Table 3-1. Pill-out Description |          |          |         |                                                   |  |

|---------------------------------|----------|----------|---------|---------------------------------------------------|--|

| QFN-28                          | WLCSP-23 | Name     | Type    | Description                                       |  |

| Pin#                            | Pin #    |          |         |                                                   |  |

| 0                               |          | VSS_DIE  |         | Die attach pad, connect to VSS on PCB             |  |

| 1                               | A5       | ANT      | RF      | RF single ended antenna                           |  |

| <b>2</b> <sup>2</sup>           | B5       | AVSS     | Supply  | Analog ground                                     |  |

| 3                               | C5       | XIN      | XTAL    | 48MHz Xtal                                        |  |

| 4                               | C4       | XOUT     | XTAL    | 48MHz Xtal                                        |  |

| 5                               | C3       | GPIO11   | Digital | Logic input/output                                |  |

| 6                               | C2       | GPIO10   | Digital | Logic input/output                                |  |

| 7                               | D4       | GPIO9    | Digital | Logic input/output                                |  |

| 8                               | D3       | GPIO8    | Digital | Logic input/output                                |  |

| 9                               |          | GPIO7    | Digital | Logic input/output – USB D+                       |  |

| 10                              |          | GPIO6    | Digital | Logic input/output – USB D-                       |  |

| 11                              |          | VIO      | Supply  | GPIO voltage level                                |  |

| 12                              | E3       | GPIO4    | Digital | Logic input/output                                |  |

| 13                              | E4       | GPIO1    | Digital | Logic input/output                                |  |

| 14                              | E2       | GPIO2    | Digital | Logic input/output                                |  |

| 15                              | E5       | GPIO3    | Digital | Logic input/output                                |  |

| 16                              | E1       | GPIO0    | Digital | Logic input/output                                |  |

| 17                              | D2       | GPIO5    | Digital | Logic input/output – ADC – PTM                    |  |

| 18                              | D1       | VBAT1    | Supply  | Battery voltage for DCDC, configuration detection |  |

| 19                              | C1       | SW DCDC  | DCDC    | Coil; configuration detection                     |  |

| 20                              |          | VSS_DCDC | DCDC    | Ground of DCDC switches                           |  |

| 21                              |          | VBUS     | Supply  | USB supply                                        |  |

| 22                              | B1       | VSS      | Supply  | Logic ground                                      |  |

| 23                              | A1       | VCC      | Supply  | Analog supply                                     |  |

| 24                              | A2       | VBAT2    | Supply  | External battery voltage                          |  |

| 25                              | B2       | LF_XOUT  | XTAL    | 32kHz Xtal                                        |  |

| 26                              | B3       | LF_XIN   | XTAL    | 32kHz Xtal                                        |  |

| 27                              | B4       | ĒN       | Digital | Chip enable                                       |  |

| 28                              | A3       | AVDD_PA  | Supply  | RF Supply                                         |  |

<sup>&</sup>lt;sup>2</sup> The pin 2 is physically not connected inside the QFN package, but it shall be connected to the ground of the die attach pad on the PCB.

Figure 3-1: Pin location on QFN package (top/PCB view)<sup>3</sup>

Mechanical drawings of the QFN package are reported in Section 14.1.

<sup>&</sup>lt;sup>3</sup> The pin 2 "AVSS" is physically not connected inside the package, but it shall be connected to the ground of the die attach pad on the PCB.

Figure 3-2: Ball location on WLCSP package (top/PCB view). Ball E1 is referenced as (0, 0) in Table 3-2

Table 3-2: Ball position (top/PCB view) with reference to Figure 3-2

| Pin        | Dia none | Ball lo | cation |

|------------|----------|---------|--------|

| number     | Pin name | Χ (μm)  | Υ (μm) |

| A1         | VCC      | 0       | 1400   |

| A2         | VBAT2    | 350     | 1400   |

| <b>A</b> 3 | AVDD_PA  | 700     | 1400   |

| A4         |          |         |        |

| A5         | ANT      | 1400    | 1400   |

| B1         | VSS      | 0       | 1050   |

| B2         | LF_XOUT  | 350     | 1050   |

| B3         | LF_XIN   | 700     | 1050   |

| B4         | EN       | 1050    | 1050   |

| B5         | AVSS     | 1400    | 1050   |

| C1         | SW_DCDC  | 0       | 700    |

| C2         | GPIO10   | 350     | 700    |

| C3         | GPIO11   | 700     | 700    |

| C4         | XOUT     | 1050    | 700    |

| C5         | XIN      | 1400    | 700    |

| D1         | VBAT1    | 0       | 350    |

| D2         | GPIO5    | 350     | 350    |

| D3         | GPIO8    | 700     | 350    |

| D4         | GPIO9    | 1050    | 350    |

| D5         |          |         |        |

| E1         | GPIO0    | 0       | 0      |

| E2         | GPIO2    | 350     | 0      |

| E3         | GPIO4    | 700     | 0      |

| E4         | GPIO1    | 1050    | 0      |

| E5         | GPIO3    | 1400    | 0      |

Mechanical drawings of the WLCSP package are reported in Section 14.2.

# 4. ELECTRICAL SPECIFICATIONS

### 4.1. ABSOLUTE MAXIMUM RATINGS

Table 4-1 summarizes the absolute maximum ratings for the EM9305.

**Table 4-1: Absolute Maximum Ratings**

| Tubio 4 11 Abboliato ilianiliani                                           | Ţ.               | VAL        | _UE         |      |

|----------------------------------------------------------------------------|------------------|------------|-------------|------|

| PARAMETER                                                                  | SYMBOL           | MIN        | MAX         | UNIT |

| Voltage at any ground pin                                                  | $V_{GND}$        | -0.2       | 0.2         | V    |

| Battery voltage 1                                                          | $V_{BAT1}$       | -0.2       | 3.9         | V    |

| Battery voltage 2 (external supply)                                        | $V_{BAT2}$       | -0.2       | 3.9         | V    |

| Analog supply voltage                                                      | V <sub>CC</sub>  | -0.2       | 2.7         | V    |

| USB V <sub>BUS</sub> pin voltage                                           | $V_{BUS}$        | -0.2       | 5.7         | V    |

| Voltage on USB DP/DM pin (GPIO6-7) only when in USB mode                   | $V_{DP}/V_{DM}$  | -1.0       | 4.6         | V    |

| Voltage at any remaining pin                                               | $V_{PIN}$        | -0.2       | 3.9         | V    |

| RF input power (at the antenna with +6dBm matching network)                | P <sub>IN</sub>  | _          | 17          | dBm  |

| Storage temperature                                                        | T <sub>ST</sub>  | -50        | 150         | °C   |

| HBM electrostatic discharge referred to ground – according to JEDEC JS-001 | V <sub>HBM</sub> | -2000      | 2000        | V    |

| CDM electrostatic discharge – according to JEDEC JS-002                    | $V_{CDMQFN}$     | -750       | 750         | V    |

| Maximum soldering conditions                                               | As per JEI       | DEC J-STD- | 020 standar | d    |

Stresses above these listed maximum ratings may cause permanent damage to the device. Exposure beyond specified operating conditions may affect device reliability or cause malfunction.

# 4.2. GENERAL OPERATING CONDITIONS

Table 4-2 shows the general operating conditions for the EM9305. While the chip is operational down to 1.1V, the output power levels are only guaranteed at the supply voltages specified in the table.

**Table 4-2: General Operating Conditions**

|                                                  | 0) (1 1 7 0 1        | VAL  | LINUT |      |

|--------------------------------------------------|----------------------|------|-------|------|

| PARAMETER                                        | SYMBOL               | MIN  | MAX   | UNIT |

| Operating temperature range                      | T <sub>OP</sub>      | -40  | 85    | °C   |

| Battery voltage 1 (for DCDC)                     | V <sub>BAT1</sub>    | 1.7  | 3.6   | V    |

| Battery voltage 2 (external supply) for 0dBm TX  | V <sub>BAT2_0</sub>  | 1.1  | 3.6   | V    |

| Battery voltage 2 (external supply) for 3dBm TX  | V <sub>BAT2_3</sub>  | 1.25 | 3.6   | V    |

| Battery voltage 2 (external supply) for 6dBm TX  | $V_{BAT2\_6}$        | 1.73 | 3.6   | V    |

| Battery voltage 2 (external supply) for 8dBm TX  | V <sub>BAT2_8</sub>  | 2.55 | 3.6   | V    |

| Battery voltage 2 (external supply) for 10dBm TX | V <sub>BAT2_10</sub> | 2.55 | 3.6   | V    |

| Analog supply voltage                            | V <sub>CC</sub>      | 1.1  | 1.9   | V    |

| USB supply voltage                               | $V_{BUS}$            | 4.4  | 5.25  | V    |

All DC voltages are referred to the absolute voltage at the pin VSS.

The output power will decrease automatically if supply voltage drops below the minimum value.

The battery voltage is always connected to VBAT2, and alternatively to VBAT1 and VCC; see Figure 1-4 to Figure 1-7.

#### 4.3. ELECTRICAL CHARACTERISTICS

Unless otherwise specified:

- All DC voltages are referred to the absolute voltage at the pin VSS.

- Typical values are measured at 25°C; minimal and maximal values are measured from -40°C to +85°C.

## 4.3.1. DC CHARACTERISTICS

Table 4-3 shows the DC characteristics in DCDC Step-Down Configuration with 3.0V applied to VBAT2, no flash usage, and GPIO not toggling. The values are compared with the DC characteristics in Voltage Multiplier Configuration with VBAT2 = 1.5V.

Table 4-3: Typical DC current, DCDC Step-Down and Voltage Multiplier Configurations at 48MHz CPU speed

|                     | PARAMETER                              | STEP DOWN $V_{BAT2} = 3.0V$ | V MULT<br>V <sub>BAT2</sub> = 1.5V | UNIT |

|---------------------|----------------------------------------|-----------------------------|------------------------------------|------|

|                     | RX 1Mbps mode                          | 3.1                         | 6.7                                | mA   |

|                     | RX 2Mbps mode                          | 3.3                         | 7.2                                | mA   |

|                     | TX mode, -33 dBm                       | 1.6                         | 3.4                                | mA   |

|                     | TX mode, -24 dBm                       | 1.7                         | 3.6                                | mA   |

|                     | TX mode, -15 dBm                       | 1.9                         | 4.0                                | mA   |

|                     | TX mode, -12 dBm                       | 2.0                         | 4.3                                | mA   |

|                     | TX mode, -9 dBm                        | 2.2                         | 4.7                                | mA   |

| Halt                | TX mode, -6 dBm                        | 2.5                         | 5.4                                | mA   |

| CPU in Halt         | TX mode, -3 dBm                        | 2.9                         | 6.3                                | mA   |

| ٦                   | TX mode, 0 dBm                         | 3.4                         | 7.4                                | mA   |

| Ö                   | TX mode, 3 dBm                         | 4.4                         | 9.1                                | mA   |

|                     | TX mode, 4 dBm                         | 5.3                         | 10.0                               | mA   |

|                     | TX mode, 5 dBm                         | 6.4                         | 10.8                               | mA   |

|                     | TX mode, 6 dBm                         | 7.8                         | N.A.                               | mA   |

|                     | TX mode, 8 dBm                         | 14.5                        | N.A.                               | mA   |

|                     | TX mode, 10 dBm                        | 17.6                        | N.A.                               | mA   |

|                     | Active RC                              | 250                         | 510                                | μA   |

|                     | Active XTAL                            | 420                         | 890                                | μA   |

|                     | Coremark test running in NVM           | 1.08                        | 2.33                               | mA   |

|                     | Sleep mode, LF RC, no retention        | 53                          |                                    | nA   |

|                     | Sleep mode, LF XTAL, no retention      |                             | 10                                 | nA   |

| Sleep mode currents | Deep Sleep mode, LF RC, no retention   | 20                          |                                    | nA   |

| ırre                | Deep Sleep mode, LF XTAL, no retention |                             | 10                                 | nA   |