# RAINFC TRANSPONDER IC FOR SECURE APPLICATIONS

### **DESCRIPTION**

em|echo-lock corresponds to the latest generation of EM Microelectronic RAINFC devices, bringing innovative features to the HF, NFC, and RAIN RFID<sup>TM</sup> worlds. The chip combines all functionalities on a single die, with NFC for proximity range, HF for vicinity range, and RAIN technology used for long range application purposes. All protocols make use of a shared memory and a common IC serial number.

em|echo-lock incorporates the Cryptographic Suite (CS) defined by ISO/IEC 29167-10 (AES-128) and it is available to all protocols. The AES-128 CS provides security services for tag authentication, interrogator authentication, and data exchange during authentication including key update.

em|echo-lock includes the new and improved GS1  $EPC^{TM}$  Gen2v3 air interface protocol which provides better management of tag populations and more reliable communications.

## **APPLICATIONS**

- I Industrial, automotive, rail, and aerospace logistics

- Automated vehicle ID for tolling, parking, and registration

- Event ticketing and crowd management

- I Product authentication with tamper evidence detection

## **FEATURES**

- Advanced RAIN RFID technology

- AES-128 crypto for tag and interrogator authentication

- I Tamper detection

- I Shared memory

- I Minimum 100k write cycles endurance

- I Minimum 10 years data retention @ 70°C, minimum 30 years data retention @ 55°C

- Dual Frequency 1-step inlay manufacturing

- On-chip resonant capacitor: 50pF

- Extended temperature range: -40°C to +85°C

- Sawn wafers, 6-mil thickness, gold bumps

### RAIN RFID is a trademark of the RAIN Alliance

It is recommended to follow the RAIN Alliance best encoding practices for UHF EPC/UII memory (see https://rainrfid.org/cin)

EPC is a trademark of EPCglobal Inc.

N-Mark is a trademark of the NFC Forum

## HF INTERFACE

- I ISO/IEC 15693 and 18000-3 compliant

- Supports ISO/IEC 29167-10 (AES-128 crypto)

- NIST SP 800-22 compliant

- Optional AES tag authentication and interrogator authentication, supported with up to 2 crypto keys

- Optional random ID and secure customer privacy

- Protected memory using password or crypto

- I Tamper Alarm is readable

### **NFC INTERFACE**

- NFC Forum Type 5 Tag compliant

- All HF interface features are available via NFC

## **UHF INTERFACE**

- I ISO/IEC 18000-63 compliant

- I EPC<sup>™</sup> Generation-2 Version 3 (Gen2v3) compliant:

- Alteration EAS compliant

- Tag Alteration (Authenticate) compliant

- Tag Alteration (Challenge) compliant

- Supports ISO/IEC 29167-10 (AES-128 crypto)

- NIST SP 800-22 compliant

- Optional AES tag authentication, interrogator authentication, supported with up to 2 crypto keys

- Read sensitivity up to -21dBm with a dipole antenna

- Write sensitivity up to -16dBm with a dipole antenna

- I Tamper status is readable

### **MEMORY**

1

- Shared unique IC serial number included in:

- 64-bit UID (HF)

- 96-bit TID (UHF)

- Memory partitions for Dual Frequency devices:

- 1920-bit (240 bytes) HF USER memory

- Up to 480-bit EPC/UII encodings

- 2048-bit UHF USER memory

- 1 1-step tag encoding possible from either HF or UHF interface.

# **Product short data sheet**

# **TABLE OF CONTENTS**

| 1. Typical Operating Configurations             | 3 |

|-------------------------------------------------|---|

| 2. Block Diagram                                | 3 |

| 3. Electrical specifications                    | 3 |

| 3.1. Absolute Maximum Ratings                   | 3 |

| 3.2. Handling Procedures                        |   |

| 3.3. Operating Conditions                       |   |

| 3.4. Electrical Characteristics – HF Interface  |   |

| 3.5. Electrical Characteristics – UHF Interface | 4 |

| 3.6. Tamper Loop Electrical Characteristics     |   |

| 3.7. NVM Electrical Characteristics             | 5 |

| 3.8. Timing                                     |   |

| 4. Product overview                             |   |

| 4.1. Overview (HF)                              | 6 |

| 4.2. Overview (NFC)                             |   |

| 4.3. Overview (UHF)                             |   |

| 4.4. Functional Description                     |   |

| 5. Pad location diagram                         |   |

| 6. Ordering Information                         |   |

| 6.1. Version                                    |   |

| 6.2. Standard Version and Samples               |   |

| 7 Product Support                               | C |

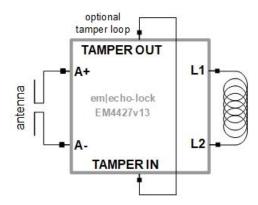

## 1. TYPICAL OPERATING CONFIGURATIONS

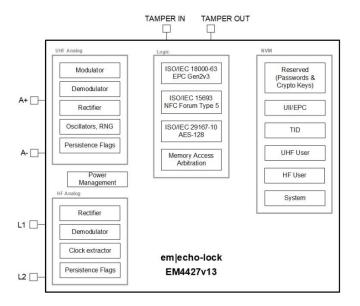

## 2. BLOCK DIAGRAM

## 3. ELECTRICAL SPECIFICATIONS

# 3.1. ABSOLUTE MAXIMUM RATINGS

| Parameters                                             | Symbol               | Min.  | Max. | Unit |

|--------------------------------------------------------|----------------------|-------|------|------|

| Storage temperature                                    | TSTORAGE             | -50   | 125  | °C   |

| RF power at antenna attached to A+, A- 1)              | P <sub>MAX-ABS</sub> |       | 25   | dBm  |

| AC current induced on L1, L2                           | I <sub>MAX-ABS</sub> |       | 50   | mA   |

| Electrostatic discharge on all pads/pins <sup>2)</sup> | V <sub>ESD</sub>     | -2000 | 2000 | V    |

Note 1: Antenna matched to IC impedance at read sensitivity ( $P_{\text{READ}}$ )

Note 2: Human Body Model (HBM; 100pF; 1.5kOhm) for all combinations between pads/pins. ESD measurements are made with die mounted into CDIP packages

Stresses above these listed maximum ratings may cause permanent damages to the device. Exposure beyond specified operating conditions may affect device reliability or cause malfunction.

# 3.2. HANDLING PROCEDURES

This device has built-in protection against high static voltages or electric fields; however, anti-static precautions must be taken as for any other CMOS component. Unless otherwise specified, proper operation can only occur when all terminal voltages are kept within the voltage range. Unused inputs must always be tied to a defined logic voltage level.

### 3.3. OPERATING CONDITIONS

| Parameters                                | Symbol              | Min. | Max. | Unit |

|-------------------------------------------|---------------------|------|------|------|

| Operating temperature                     | $T_OP$              | -40  | +85  | °C   |

| RF power at antenna attached to A+, A- 1) | P <sub>MAX-OP</sub> |      | 20   | dBm  |

| RF carrier frequency                      | f <sub>A</sub>      | 860  | 960  | MHz  |

| AC peak current induced on L1, L2         | I <sub>MAX-OP</sub> |      | 30   | mA   |

### 3.4. ELECTRICAL CHARACTERISTICS - HF INTERFACE

Operating conditions (unless otherwise specified): Vcoil = 4V (peak to peak), Vss = 0V, fc = 13.56MHz sine wave, Top = 25°C.

| Parameters          | Symbol           | Conditions                  | Min. | Тур.  | Max. | Unit |

|---------------------|------------------|-----------------------------|------|-------|------|------|

| Operating frequency | fc               |                             | -    | 13.56 | -    | MHz  |

| Resonance Capacitor | C <sub>r50</sub> | fc = 13.56MHz;<br>U = 2Vrms | 47.5 | 50    | 52.5 | pF   |

### 3.5. ELECTRICAL CHARACTERISTICS – UHF INTERFACE

Operating conditions (unless otherwise specified): T<sub>OP</sub> = 25°C.

| Parameters                                                                                          | Symbol              | Conditions                                                                                                                                                                                                                    | Min. | Тур.                                  | Max. | Unit                     |

|-----------------------------------------------------------------------------------------------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------------------------------------|------|--------------------------|

| IC input capacitance                                                                                | Ср                  | Parallel                                                                                                                                                                                                                      | -    | 0.66                                  | -    | pF                       |

| IC impedance <sup>3)</sup>                                                                          | Z <sub>AB</sub>     | f <sub>A</sub> =866MHz<br>f <sub>A</sub> =915MHz                                                                                                                                                                              | -    | 18.1-j279<br>17.2-j263                |      | Ω                        |

| Typical assembly capacitance 4)                                                                     | CASSY               |                                                                                                                                                                                                                               | -    | 0.2                                   | -    | pF                       |

| IC read (inventory) sensitivity <sup>5)6)7)8)</sup>                                                 | Pread               | Power Check Enables Inventory disabled; Query command; fA=866MHz fA=915MHz  Power Check Enables Inventory disabled; QueryX command; fA=866MHz fA=915MHz  Power Check Enables Inventory enabled; fA=866MHz fA=866MHz fA=915MHz |      | -19<br>-19<br>-16.3<br>-16.3<br>-15.5 |      | dBm<br>dBm<br>dBm<br>dBm |

| IC write sensitivity <sup>5)6)7)8)</sup> IC tag authentication (TA) sensitivity <sup>5)6)7)8)</sup> | Pwrite              | f <sub>A</sub> =866MHz<br>f <sub>A</sub> =915MHz                                                                                                                                                                              | -    | -14<br>-14                            | -    | dBm<br>dBm               |

|                                                                                                     | P <sub>TA</sub>     | Power Check Enables<br>Inventory disabled;<br>AES-128 TAM1                                                                                                                                                                    |      | -18                                   |      | dBm                      |

|                                                                                                     | P <sub>TAfast</sub> | AES-128 TAM1                                                                                                                                                                                                                  |      | -14.5                                 |      | dBm                      |

$\textbf{Note 3} : \text{Measured directly on wafer with a } 100\Omega \text{ differential network analyzer at minimum operating RF power level}$

Note 4: The antenna should be matched assuming 200fF additional input capacitance from assembly

Note 5: IC impedance conjugate matched to antenna at read sensitivity (P<sub>READ</sub>)

Note 6: IC is configured with tamper pads disabled and EPC/UII encoding of 96 bits

Note 7: HF field is not present

Note 8: Sensitivity values are for IC devices in die form and do not include antenna gain

# 3.6. TAMPER LOOP ELECTRICAL CHARACTERISTICS

Operating conditions (unless otherwise specified):  $T_{OP} = 25$ °C.

| Parameters                                               | Symbol              | Conditions                                  | Min. | Тур.      | Max. | Unit |

|----------------------------------------------------------|---------------------|---------------------------------------------|------|-----------|------|------|

| Tamper loop maximum capacitance                          | C <sub>max</sub>    | Measured between tamper pads                |      |           | 47   | pF   |

| Tamper loop maximum inductance                           | L <sub>max</sub>    | Measured between tamper pads                |      |           | 40   | nΗ   |

| Resistance connected between TAMPER_IN and TAMPER_OUT to | R <sub>CLOSED</sub> | Cloadmax between tamper pads/pins = 12.5pF; |      |           | 1    | МΩ   |

| assure a closed (short) loop                             |                     | Tamper loop enabled                         |      |           |      |      |

| Resistance connected between TAMPER_IN and TAMPER_OUT to | ROPEN               | Cloadmax between tamper pads/pins = 12.5pF; | 10   |           |      | ΜΩ   |

| assure an open (broken) loop                             |                     | Tamper loop enabled                         |      |           |      |      |

| Input impedance between<br>TAMPER_IN and TAMPER_OUT      | Z <sub>TAMPER</sub> | RF power = P <sub>READ</sub> ;              |      |           |      |      |

|                                                          |                     | Pads configured for HI-Z;                   |      | 5.2-j106  |      | Ω    |

|                                                          |                     | f <sub>A</sub> = 866MHz                     |      |           |      |      |

|                                                          |                     | RF power = P <sub>READ</sub> ;              |      |           |      |      |

|                                                          |                     | Pads configured for Tamper Loop;            |      | 17.5-j106 |      | Ω    |

|                                                          |                     | f <sub>A</sub> = 866MHz                     |      |           |      |      |

|                                                          |                     | RF power = P <sub>READ</sub> ;              |      |           |      |      |

|                                                          |                     | Pads configured for HI-Z;                   |      | 5.1-j101  |      | Ω    |

|                                                          |                     | f <sub>A</sub> = 915MHz                     |      |           |      |      |

|                                                          |                     | RF power = P <sub>READ</sub> ;              |      |           |      |      |

|                                                          |                     | Pads configured for Tamper Loop;            |      | 16.1-j101 |      | Ω    |

|                                                          |                     | f <sub>A</sub> = 915MHz                     |      |           |      |      |

# 3.7. NVM ELECTRICAL CHARACTERISTICS

| Parameters              | Symbol           | Conditions             | Min.    | Тур. | Max. | Unit   |

|-------------------------|------------------|------------------------|---------|------|------|--------|

| Erase / write endurance | Tcyc             | T <sub>OP</sub> = 25°C | 100,000 |      |      | Cycles |

| Retention               | T <sub>RET</sub> | T = 70°C               | 10      |      |      | Years  |

|                         |                  | T = 55°C               | 30      |      |      |        |

# **3.8. TIMING**

| Parameters                                                                                                                                                                                 | Symbol                | Conditions                                                   | Min. | Тур. | Max. | Unit |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|--------------------------------------------------------------|------|------|------|------|

| Power-up timing to receive first command                                                                                                                                                   | T <sub>PWR_UP</sub>   | Supports both Gen2v2 and Gen2v3 timing requirements          |      |      | 1.5  | ms   |

| HF interface execution time to write a value into NVM  HF Authenticate (TA) AES-128 crypto execution time for TAM1  UHF Authenticate (TA) AES-128 crypto execution time for TAM1 5/90/7/8) | Т                     | All commands except for Write Multiple Blocks                |      |      | 10.9 | ms   |

|                                                                                                                                                                                            | $T_{WRITE}$           | Write Multiple Blocks when writing two physical blocks       |      |      | 15.4 | ms   |

|                                                                                                                                                                                            | T <sub>HF_TAM1</sub>  |                                                              |      |      | 2.7  | ms   |

|                                                                                                                                                                                            | T <sub>UHF TAM1</sub> | Fast crypto speed when more RF power is sensed by the device |      |      | 8.0  | ms   |

| Crypto execution time for TAIMT System                                                                                                                                                     | -                     | Normal crypto speed                                          |      |      | 1.4  | ms   |

### Product short data sheet

### 4. PRODUCT OVERVIEW

em|echo-lock is used in passive transponder applications and provides support for use as either a Dual Frequency product (HF + UHF, NFC + UHF, or HF/NFC + UHF) or a UHF Only product.

Both the HF / NFC and UHF interfaces have access to all of memory although access operations may be protected and require the use of passwords or crypto. No priority is given to either air interface. The memory cannot be accessed in parallel and memory access arbitration is performed on a per command basis as the commands are received over the air interfaces.

The user has the option to select the security features appropriate for their application(s).

The user has the option to enable the tamper detection feature which checks impedance of a continuity loop at power-up between two pads/pins to determine if the loop is intact (closed) or broken (open).

### 4.1. OVERVIEW (HF)

em|echo-lock corresponds to the latest generation of ISO/IEC 15693 and 18000-3 Mode 1 devices offering innovative and enriched features.

The IC supports data rates at 6kbps, 26kbps, and 53kbps.

em|echo-lock offers the maximum of flexibility in terms of security using ISO/IEC 29167-10 (AES-128) security services, or password protection, or none at all.

Each em|echo-lock chip is delivered with a unique 64-bit inalterable UID number programmed at wafer level to ensure full traceability.

em|echo-lock supports the optional Write Multiple Blocks command, enabling rapid tag encoding.

The HF memory is also accessible through the UHF interface as specified later in this document.

The HF specific mechanisms and features do not influence UHF functionality excluding memory sharing and mechanisms which are explicitly described.

### 4.2. OVERVIEW (NFC)

em|echo-lock corresponds to the latest generation of NFC Type 5 devices offering innovative and enriched features.

The IC supports data rates at 26kbps.

The HF / NFC memory contains the NFC Capability Container, the NDEF message, and other proprietary data.

The HF / NFC memory is also accessible through UHF interface as specified later on in this document.

The NFC specific mechanisms and features do not influence UHF functionality excluding memory sharing and mechanisms which are explicitly described.

### 4.3. OVERVIEW (UHF)

em|echo-lock is a RAIN RFID IC compliant with ISO/IEC 18000-63 and GS1 EPC Gen2v3. It supports the Tag Alteration (Challenge), Tag Alteration (Authenticate), and Alteration EAS application requirements to provide data privacy and EAS capability.

em|echo-lock offers the maximum of flexibility in terms of security using ISO/IEC 29167-10 (AES-128) security services, or password protection, or none at all.

Each em|echo-lock chip is delivered with a 96-bit inalterable TID number programmed at wafer level to ensure full traceability.

em|echo-lock supports the optional BlockWrite command, enabling rapid tag encoding.

The UHF memory is also accessible through HF / NFC interface as specified later on in this document.

The UHF specific mechanisms and features do not influence HF / NFC functionality excluding memory sharing and mechanisms which are explicitly described.

### 4.4. FUNCTIONAL DESCRIPTION

As soon as the em|echo-lock enters an RF operating field (HF / NFC or UHF), the energy from the operating field is extracted to provide power for the IC. Both fields can be present simultaneously.

em|echo-lock initialization occurs during power-up (BOOT) and the device reads initial values from NVM to configure the tag for normal operation. The em|echo-lock stays quiet and ignores all incoming communication during BOOT.

If UHF field is present, then UHF mode is available (if not killed) after BOOT and UHF interface is ready to execute commands. If HF field is present, HF / NFC mode is available (if not killed) after BOOT and HF / NFC interface is ready to execute commands.

#### Product short data sheet

If both fields are present, then both HF / NFC mode and UHF mode are available and commands will be executed on a first-in, first-served basis.

This device is in full compliance with the following documents:

#### HF:

- "ISO/IEC 15693-2:2019 Identification cards Contactless integrated circuit cards Vicinity cards Part 2: Air interface and initialization", Publication Date: 2019-04

- "ISO/IEC 15693-3:2019 Identification cards Contactless integrated circuit cards Vicinity cards Part 3: Anticollision and transmission protocol", Publication Date: 2019-04

- "ISO/IEC 18000-3:2010 Information technology Radio frequency identification for item management Part 3: Parameters for air interface communications at 13,56 MHz", Publication Date: 2010-11

#### NFC:

- "NFC Forum Analog, Technical Specification, Version 2.1", Publication Date: 2018-02-19

- "NFC Forum Activity, Technical Specification, Version 2.0", Publication Date: 2017-04-30

- "NFC Forum Digital Protocol, Technical Specification, Version 2.0", Publication Date: 2017-05-09

- "NFC Forum Type 5 Tag Operation, Technical Specification, Version 1.0", Publication Date: 2015-07-07

#### UHF:

- "ISO/IEC 18000-63:2021 Information technology Radio frequency identification for item management Part 63: Parameters for air interface communications at 860 MHz to 960 MHz Type C", Publication Date: 2021-11

- "EPC® Radio-Frequency Identity Generation-2 UHF RFID Standard, Specification for RFID Air Interface Protocol for Communications at 860 MHz – 930 MHz, Release 3.0, Ratified, Jan 2024" from GS1

- "EPC Tag Data Standard TDS, defines the Electronic Product Code™ and specifies the memory content of Gen 2 RFID Tags, Release 2.2, Ratified, Feb 2025" from GS1

- "GS1 Digital Link URI: Compression Standard, An algorithm for compressing and decompressing GS1 Digital Link URIs, Release 1.0, Ratified, July 2025" from GS1

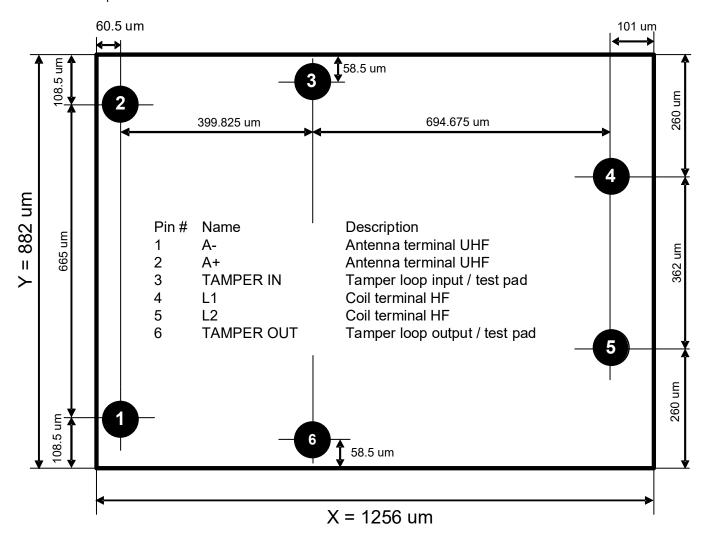

# 5. PAD LOCATION DIAGRAM

All dimensions in µm and do not include the scribe line.

| Pad | Name       | Description                                               |

|-----|------------|-----------------------------------------------------------|

| 1   | A-         | Antenna terminal for UHF                                  |

| 2   | A+         | Antenna terminal for UHF                                  |

| 3   | TAMPER IN  | Tamper loop input                                         |

| 4   | L1 / NC    | Dual Frequency: Coil terminal for HF UHF Only: No connect |

| 5   | L2 / NC    | Dual Frequency: Coil terminal for HF UHF Only: No connect |

| 6   | TAMPER OUT | Tamper loop output                                        |

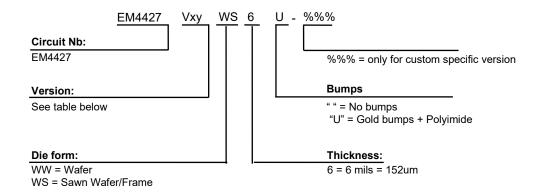

## 6. ORDERING INFORMATION

#### 6.1. VERSION

| ху | Brand Name   | Air Interfaces | Supports Crypto      |

|----|--------------|----------------|----------------------|

| 13 | em echo-lock | Dual Frequency | yes (UHF and HF/NFC) |

### 6.2. STANDARD VERSION AND SAMPLES

The version below is considered standard and should be readily available. For other delivery form, please contact EM Microelectronic-Marin S.A. For samples, please order exclusively from the standard versions.

| Brand Name   | Part Number   | Package / Die Form                                 | Delivery Form  |  |

|--------------|---------------|----------------------------------------------------|----------------|--|

| em echo-lock | EM4427V13WS6U | Sawn wafer / Gold bumped +PI – thickness of 6 mils | Wafer on frame |  |

### 7. PRODUCT SUPPORT

Check our website at  $\underline{\text{www.emmicroelectronic.com}}$  under Products/RF Identification section. Questions can be submitted to  $\underline{\text{rfidsupport@emmicroelectronic.com}}$ .

EM Microelectronic-Marin SA ("EM") makes no warranties for the use of EM products, other than those expressly contained in EM's applicable General Terms of Sale, located at http://www.emmicroelectronic.com. EM assumes no responsibility for any errors which may have crept into this document, reserves the right to change devices or specifications detailed herein at any time without notice, and does not make any commitment to update the information contained herein.

No licenses to patents or other intellectual property rights of EM are granted in connection with the sale of EM products, neither expressly nor implicitly.

In respect of the intended use of EM products by customer, customer is solely responsible for observing existing patents and other intellectual property rights of third parties and for obtaining, as the case may be, the necessary licenses.

Important note: The use of EM products as components in medical devices and/or medical applications, including but not limited to, safety and life supporting systems, where malfunction of such EM products might result in damage to and/or injury or death of persons is expressly prohibited, as EM products are neither destined nor qualified for use as components in such medical devices and/or medical applications. The prohibited use of EM products in such medical devices and/or medical applications is exclusively at the risk of the customer.