# EXTREME LOW POWER RTC WITH I2C,

# 32-bit UNIX time counter, 43 bytes EEPROM, Battery Switchover and Trickle Charger

#### **DESCRIPTION**

The EM3028 engineered using the in-house analog low power (ALP) technology provides unmatched true ultra-low current consumption of typically 40nA while running on a standard 32'768 Hz tuning fork crystal. Thus allowing several hours of backup supply using cost effective MLCC capacitors.

It provides full RTC function with programmable counters, alarm, selectable interrupt and clock output functions and also a 32-bit UNIX Time counter.

The internal EEPROM memory hosts all configuration settings and allows for additional 43 bytes of user memory.

All addresses and data are transferred over an I2C-bus interface for communication with a host controller.

It is available in a TSSOP14 plastic package or as a module combining the 32 kHz Crystal with the RTC IC in an ultrasmall, hermetically sealed C7 SMD package, factory calibrated to an initial accuracy of +/- 1ppm.

#### **FEATURES**

- I Extreme low power consumption: 40 nA @ 3 V.

- I Wide operating voltage range: 1.2 V to 5.5 V.

- I Built-in tuning Fork crystal at 32'768 Hz

- I Time accuracy: possible to calibrate to ±1 ppm @ 25°C

- I Non-volatile configuration settings with user programmable offset value.

- I Configuration stored in EEPROM and mirrored in RAM

- I Backup Switch and Trickle Charger function.

- I Provides year, month, date, weekday, hours, minutes and seconds.

- I Automatic leap year correction; 2000 to 2099

- I 32 bit UNIX time counter.

- I Timer, alarm and external event functions with time stamp

- I Clock output: 32.768 kHz, 8192 Hz, 1024 Hz, 64 Hz, 32Hz,1 Hz.

- I 43 bytes non-volatile user memory, 2 bytes user RAM.

- I I<sup>2</sup>C-bus interface: 400 kHz.

- I Package: TSSOP14, 100% Pb-free, RoHS-compliant

- I Also available in ultra-small SMD C7 package, factory calibrated and including the 32kHz crystal, part number EM3028-C7

### **APPLICATIONS**

- I loT

- I Wearable systems

- I Multi-Solar cell platforms

- I Beacons and wireless sensor networks

- I Industrial and environmental monitoring

- I Battery operated platform

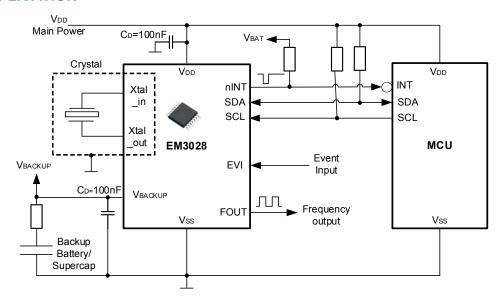

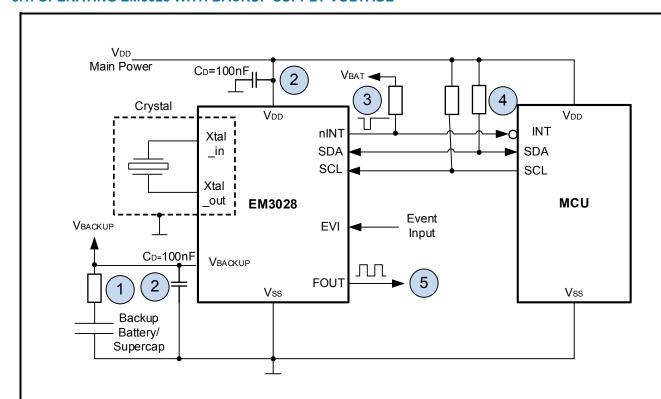

## **TYPICAL APPLICATION**

# **TABLE OF CONTENTS**

| 1. Product description                               | 9  |

|------------------------------------------------------|----|

| 1.1. Block diagram                                   | 9  |

| 1.2. Operating modes                                 | 10 |

| 1.2.1. Device Protection                             | 10 |

| 1.2.2. Register Organization                         | 10 |

| 1.2.3. Register Conventions                          | 11 |

| 1.2.4. Register Overview                             | 11 |

| 2. Handling Procedures                               | 13 |

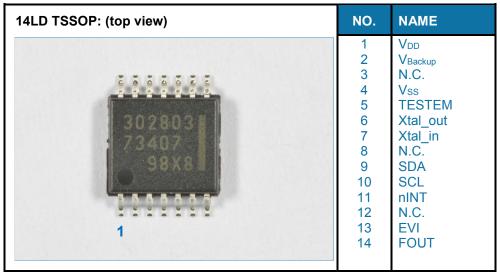

| 3. Pin description                                   | 13 |

| 4. Package / Pin Out / Marking                       | 14 |

| 5. Electrical specifications                         | 15 |

| 5.1. Absolute Maximum Ratings                        | 15 |

| 5.2. Operating Conditions                            | 15 |

| 5.3. Electrical Characteristics                      | 16 |

| 5.4. Oscillator Characteristics                      | 19 |

| 5.5. Timing Characteristics                          | 20 |

| 5.5.1. POWER ON                                      | 20 |

| 5.5.2. I <sup>2</sup> C-BUS Characteristics          | 21 |

| 6. Product configuration                             | 22 |

| 6.1. Clock Registers                                 | 22 |

| 6.2. Calendar Registers                              | 23 |

| 6.3. Alarm Registers                                 | 25 |

| 6.4. Periodic Countdown Timer Control Registers      | 27 |

| 6.5. Configuration Registers                         | 29 |

| 6.6. Event Control Register                          | 33 |

| 6.7. Time Stamp Registers                            | 34 |

| 6.8. UNIX Time Registers                             | 37 |

| 6.9. RAM Registers                                   | 38 |

| 6.10. PASSWORD Registers                             | 39 |

| 6.11. EEPROM Memory Control Registers                | 40 |

| 6.12. ID Register                                    | 41 |

| 6.13. Configuration EEPROM with RAM Mirror Registers | 41 |

| 6.13.1. EEPROM Reserved                              | 41 |

| 6.13.2. EEPROM Password Enable Register              | 41 |

| 6.14. EEPROM Password Registers                      | 42 |

| 6.15. EEPROM FOUT Register                           | 43 |

| 6.16. EEPROM OFFSET Register                         | 44 |

| 6.17. EEPROM BACKUP Register                         | 45 |

| 6.18. USER EEPROM                                    | 46 |

| 6.19. MANUFACTURER EEPROM                            | 46 |

| 6.20. Register Reset Values Summary                  | 47 |

| 7. Detailed Functional Description                   | 50 |

| 7.1. POWER ON RESET (POR)                                      | 50 |

|----------------------------------------------------------------|----|

| 7.2. AUTOMATIC BACKUP Switchover Function                      | 50 |

| 7.2.1. SWITCHOVER Disabled                                     | 51 |

| 7.2.2. Direct Switching Mode (DSM)                             | 51 |

| 7.2.3. STANDBY MODE                                            | 52 |

| 7.2.4. Level Switching Mode (LSM)                              | 52 |

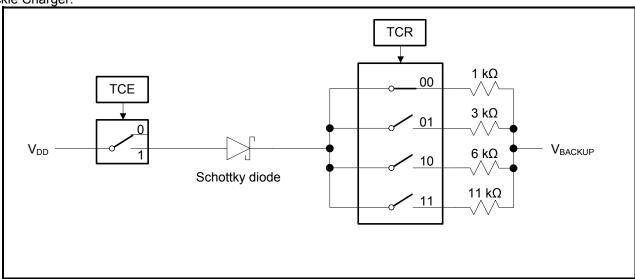

| 7.3. Trickle Charger                                           | 53 |

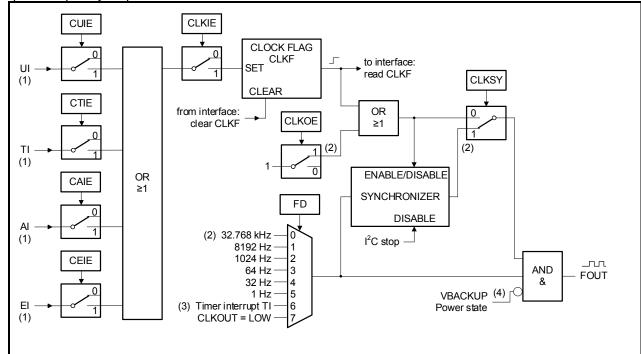

| 7.4. Programmable Clock Output                                 | 53 |

| 7.4.1. FOUT Frequency Selection                                | 54 |

| 7.4.2. Normal Clock Output                                     | 54 |

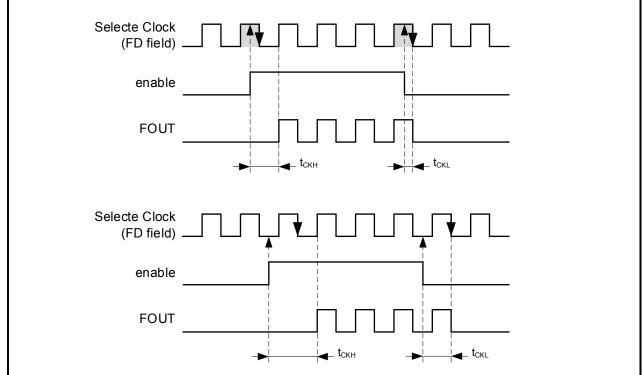

| 7.4.3. Interrupt Controlled Clock Output                       | 54 |

| 7.4.4. Synchronized Enable/Disable                             | 55 |

| 7.4.5. Clock Output Scheme                                     | 56 |

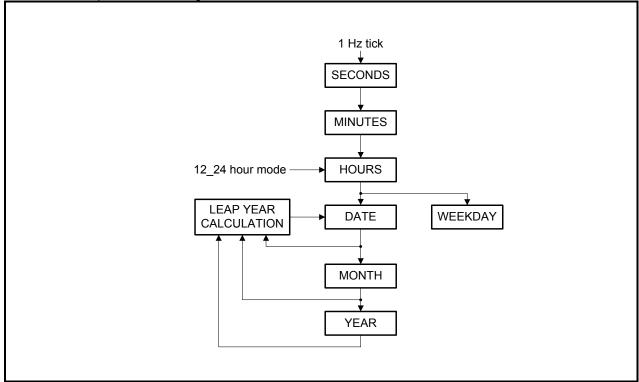

| 7.5. Setting and Reading the Time                              | 57 |

| 7.5.1. Setting the Time                                        | 58 |

| 7.5.2. Reading the Time                                        | 58 |

| 7.6. EEPROM READ/WRITE                                         | 59 |

| 7.6.1. POR Refresh (ALL CONFIGURATION EEPROM → RAM)            | 59 |

| 7.6.2. AUTOMATIC Refreash (ALL CONFIGURATION EEPROM → RAM)     | 59 |

| 7.6.3. Refresh (ALL CONFIGURATION EEPROM → RAM)                | 59 |

| 7.6.4. Update (ALL CONFIGURATION RAM → EEPROM)                 | 59 |

| 7.6.5. READ ONE EEPROM BYTE (EEPROM → RAM-EEdata)              | 59 |

| 7.6.6. Write to ONE EEPROM BYTE (RAM-EEdata → EEPROM)          | 59 |

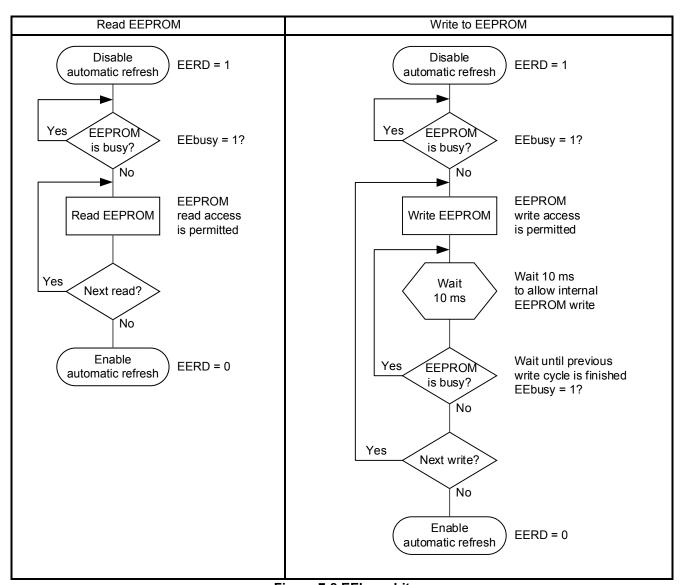

| 7.6.7. EEBUSY Bit                                              | 60 |

| 7.6.8. EEPROM Read/Write Conditions                            | 61 |

| 7.7. Use of the Configuration EEPROM WITH RAM MIRROR Registers | 61 |

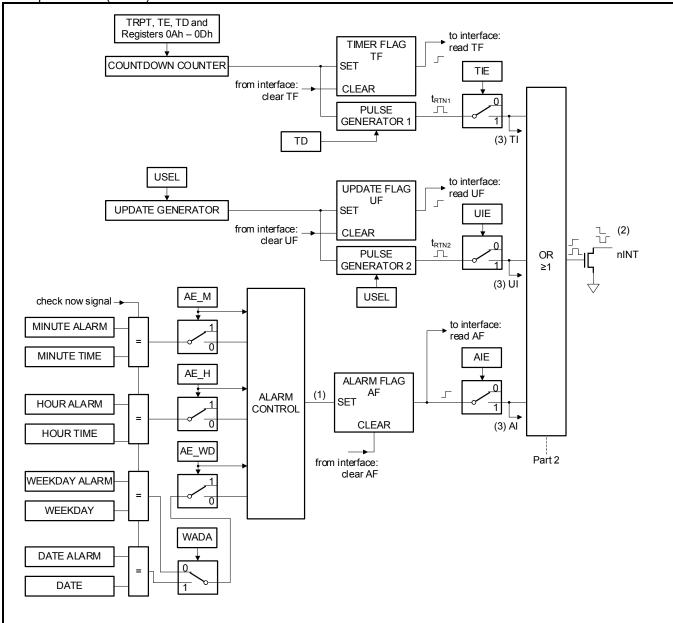

| 7.8. Interrupt Output                                          | 62 |

| 7.8.1. Servicing Interrupts                                    | 62 |

| 7.8.2. Interrupt Scheme                                        | 63 |

| 7.9. Periodic Countdown Timer Interrupt Function               | 65 |

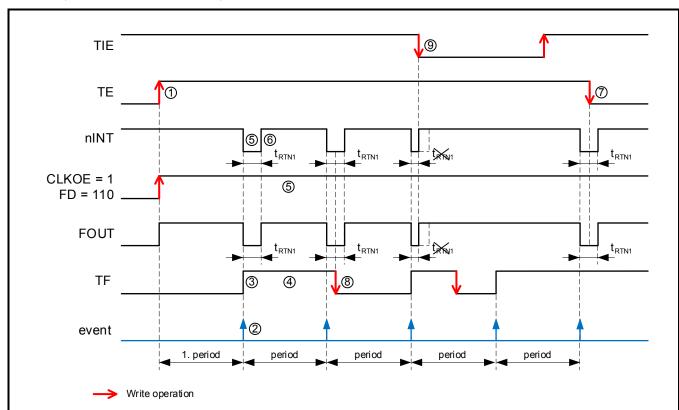

| 7.9.1. Periodic Countdown Timer Diagram                        | 66 |

| 7.9.2. Use of the Periodic Countdown Timer Interrupt           | 67 |

| 7.9.3. First Period Duration                                   | 69 |

| 7.10. Periodic Time Update Interrupt Function                  | 70 |

| 7.10.1. Periodic Time Update Diagram                           | 70 |

| 7.10.2. Use of the Periodic Time Update Interrupt              | 71 |

| 7.11. Alarm Interrupt Function                                 | 72 |

| 7.11.1. Alarm Diagram                                          | 72 |

| 7.11.2. Use of The Alarm Interrupt                             | 73 |

| 7.12. External Event Function                                  | 74 |

| 7.12.1. External Event Diagram                                 | 75 |

| 7.12.2. Use of the External Event Function                     | 76 |

| 7.13. Automatic BACKUP Switchover Interrupt Function           | 78 |

| 7.13.1. Automatic Backup Switchover Diagram              | 79  |

|----------------------------------------------------------|-----|

| 7.13.2. Use of the Automatic BACKUP Switchover Interrupt | 80  |

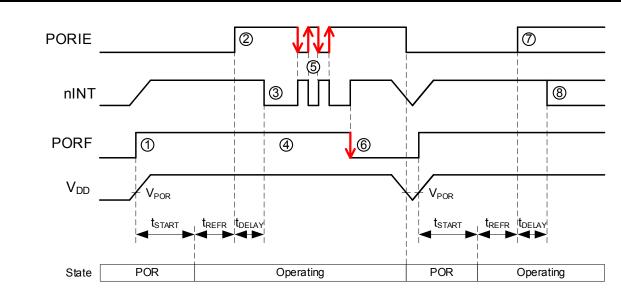

| 7.14. POWER ON RESET Interrupt Function                  | 81  |

| 7.14.1. POWER ON RESET Diagram                           | 81  |

| 7.14.2. Use of the POWER ON RESET Interrupt              | 82  |

| 7.15. TIME STAMP Function                                | 83  |

| 7.16. Frequency OFFSET Correction                        | 85  |

| 7.16.1. EEOFFSET Value Determination                     | 85  |

| 7.16.2. Verification of the Corrected Time Accuracy      | 85  |

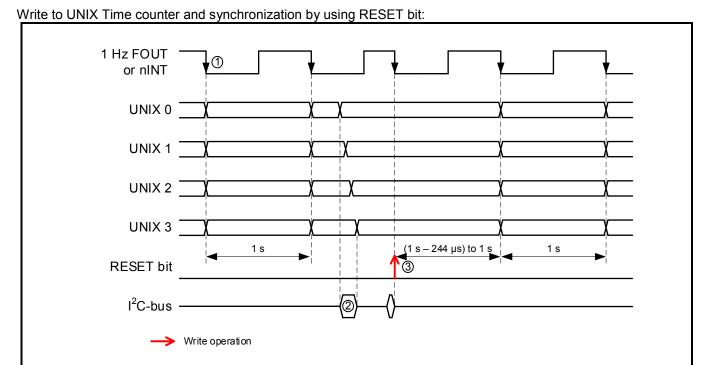

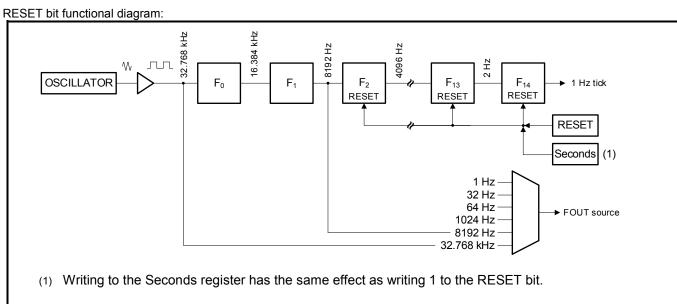

| 7.17. UNIX Time Counter                                  | 86  |

| 7.18. RESET bit Function                                 | 87  |

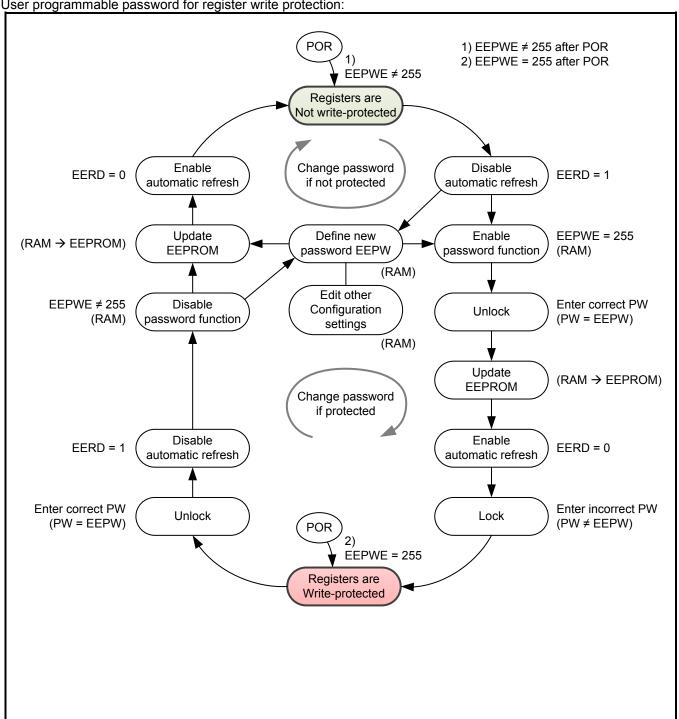

| 7.19. User Programmable Password                         | 88  |

| 7.19.1. Enabling/Disabling Write Protection              | 88  |

| 7.19.2. Changing Password                                | 89  |

| 7.19.3. Flowchart                                        | 90  |

| 7.20. I <sup>2</sup> C Interface                         | 91  |

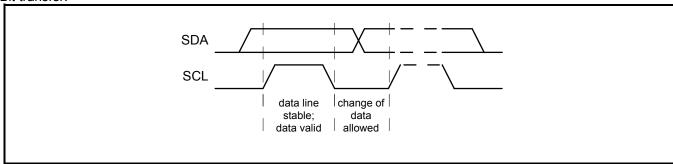

| 7.20.1. Bit Transfer                                     | 91  |

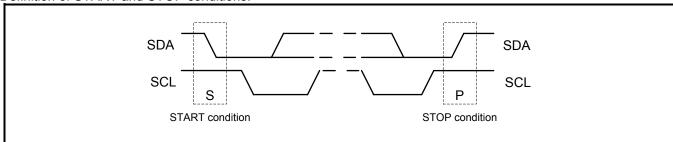

| 7.20.2. START and STOP Conditions                        | 91  |

| 7.20.3. DATA Valid                                       | 92  |

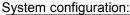

| 7.20.4. System Configuration                             | 92  |

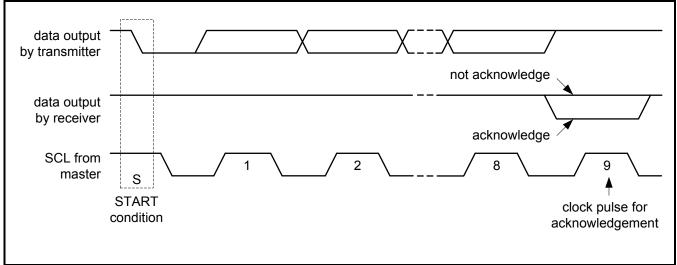

| 7.20.5. Acknowledge                                      | 93  |

| 7.20.6. Slave Address                                    | 94  |

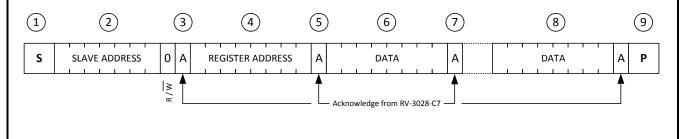

| 7.20.7. WRITE Operation                                  | 94  |

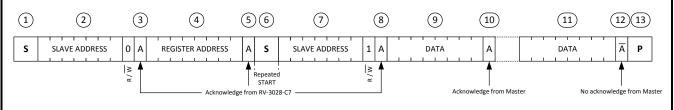

| 7.20.8. READ Operation at Specific Address               | 95  |

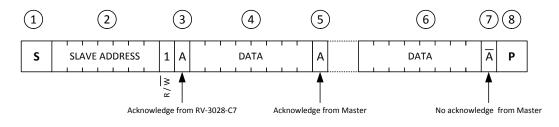

| 7.20.9. READ Operation                                   | 95  |

| 7.20.10. I <sup>2</sup> C-BUS in Switchover Condition    | 96  |

| 8. Typical Application                                   | 97  |

| 8.1. Operating EM3028 with Backup Supply Voltage         | 97  |

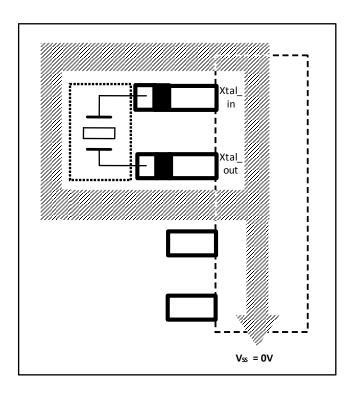

| 8.2. Crystal Layout Guideline                            | 98  |

| 9. Ordering Information                                  | 99  |

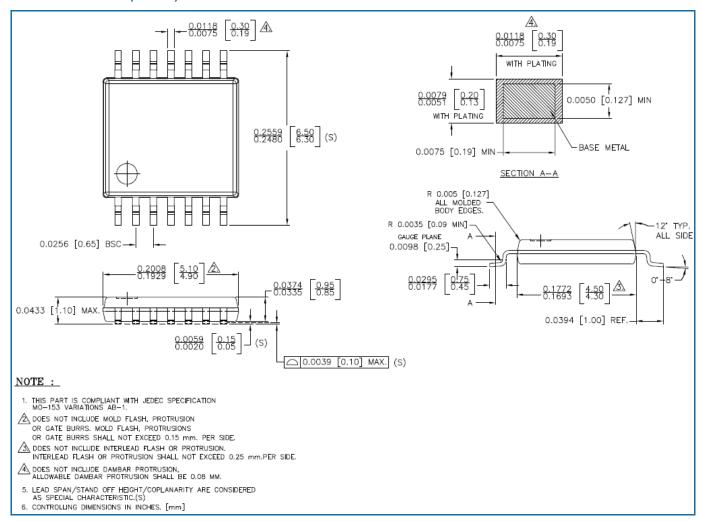

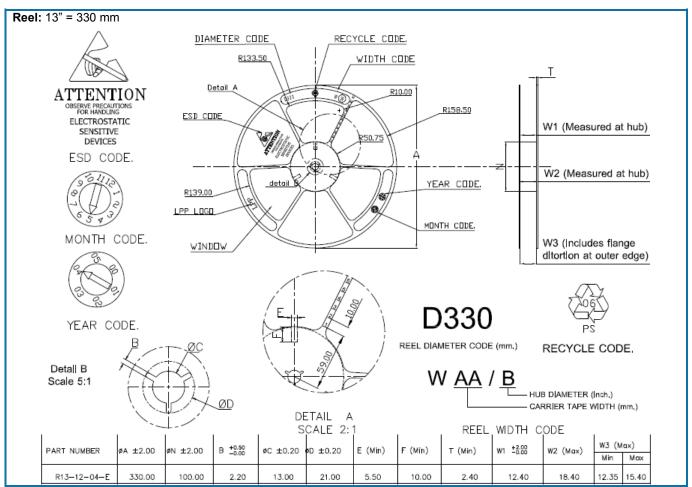

| 10. Packaging Information                                | 100 |

| 10.1. 14LD TSSOP (rev C)                                 | 100 |

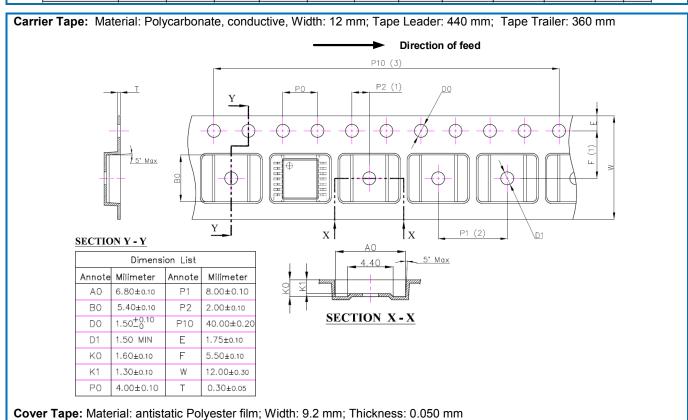

| 10.2. Tape & Reel Information                            | 101 |

| 11 Document Revision History                             | 102 |

# **LIST OF FIGURES**

| Figure 1-1 EM3028 Block Diagram                                                                                                          | g  |

|------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 1-2 Address register auto-increment                                                                                               | 10 |

| Figure 1-3 Device Diode Protection Diagram                                                                                               | 10 |

| Figure 4-1 14LD TSSOP                                                                                                                    | 14 |

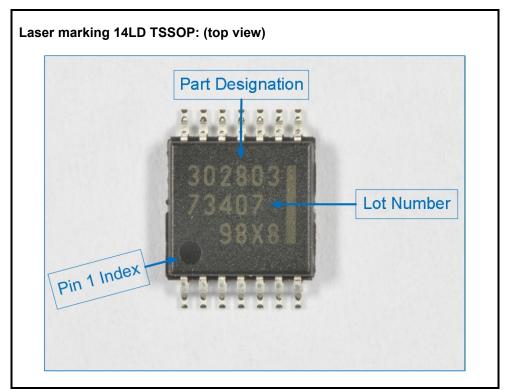

| Figure 4-2 Laser marking 14LD TSSOP                                                                                                      | 14 |

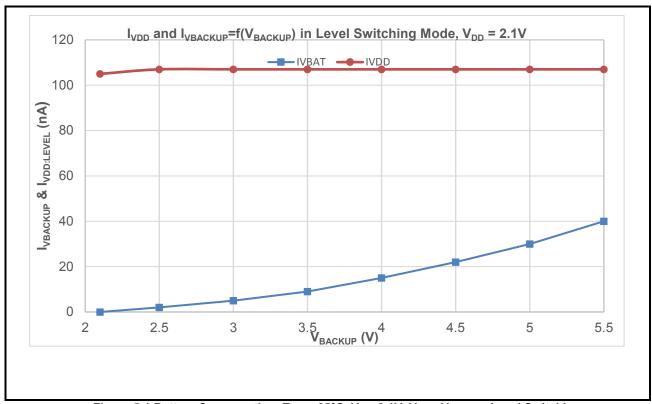

| Figure 5-1 Battery Consumption, T <sub>OPR</sub> =25°C, V <sub>DD</sub> =2.1V, V <sub>DD</sub> > V <sub>th_swbat</sub> , Level Switching | 17 |

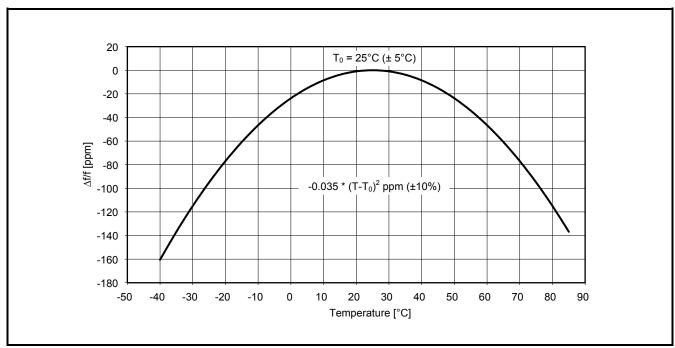

| Figure 5-2 XTAL Frequency vs Temperature Characteristics                                                                                 | 19 |

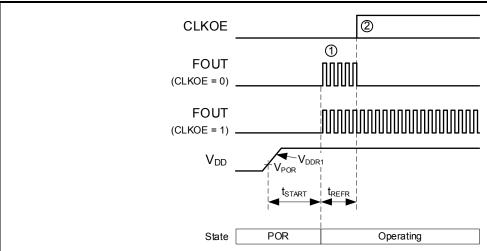

| Figure 5-3 Power On Timing Diagram                                                                                                       | 20 |

| Figure 5-4 I <sup>2</sup> C BUS Timing Diagram                                                                                           | 21 |

| Table 6 5 I <sup>2</sup> C Timing Characteristics                                                                                        | 21 |

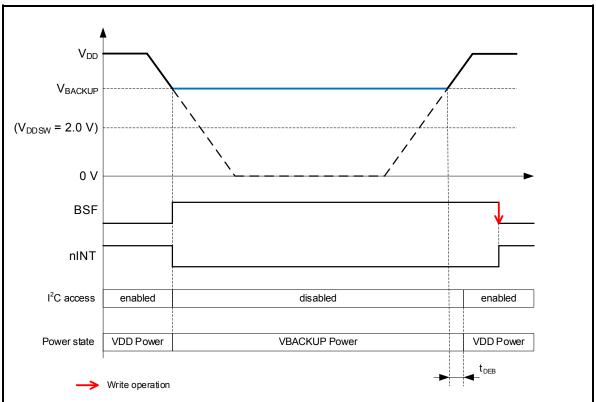

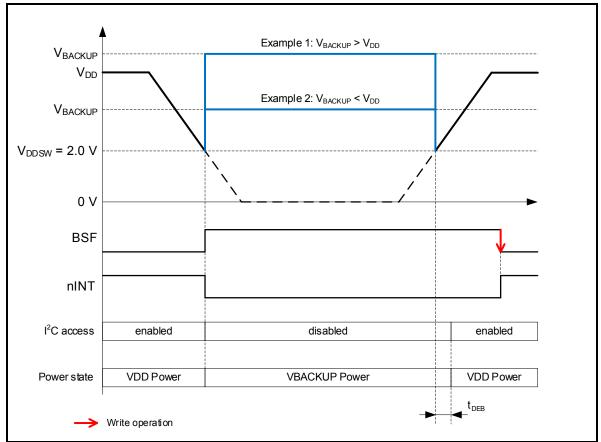

| Figure 7-1 Direct Switching Mode                                                                                                         | 51 |

| Figure 7-2 Level Switching Mode                                                                                                          | 52 |

| Figure 7-3 Trickle Charger configuration                                                                                                 | 53 |

| Figure 7-4 Frequency Output configuration                                                                                                | 55 |

| Figure 7-5 Frequency Output scheme                                                                                                       | 56 |

| Figure 7-6 Setting and Reading the Time                                                                                                  | 57 |

| Figure 7-7 Access time for Read/Write Operations                                                                                         | 57 |

| Figure 7-8 EEbusy bit                                                                                                                    | 60 |

| Figure 7-9 Interrupt Scheme (Part 1)                                                                                                     | 63 |

| Figure 7-10 Interrupt Scheme (Part 2)                                                                                                    | 64 |

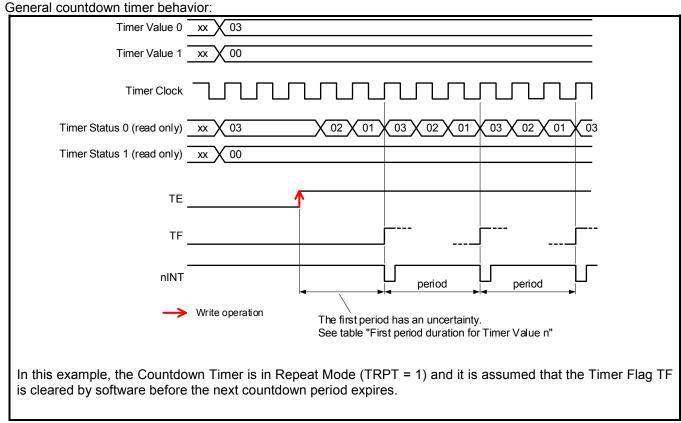

| Figure 7-11 Periodic Countdown Timer Interrupt                                                                                           | 66 |

| Figure 7-12 Periodic Countdown Timer Interrupt                                                                                           | 68 |

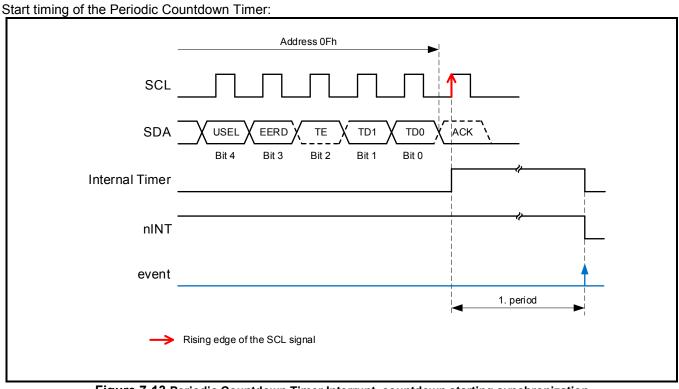

| Figure 7-13 Periodic Countdown Timer Interrupt, countdown starting synchronization                                                       | 68 |

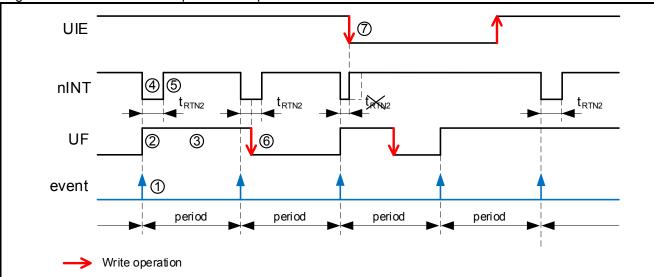

| Figure 7-14 Periodic Time Update Interrupt                                                                                               | 70 |

| Figure 7-15 Alarm Interrupt                                                                                                              | 72 |

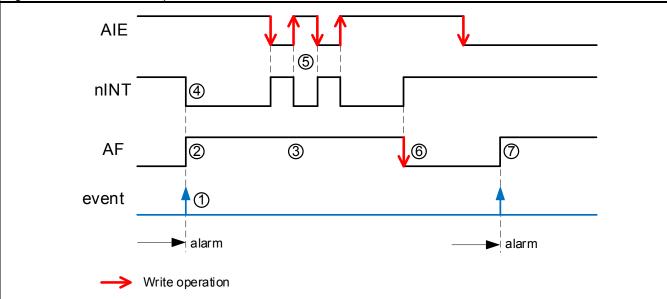

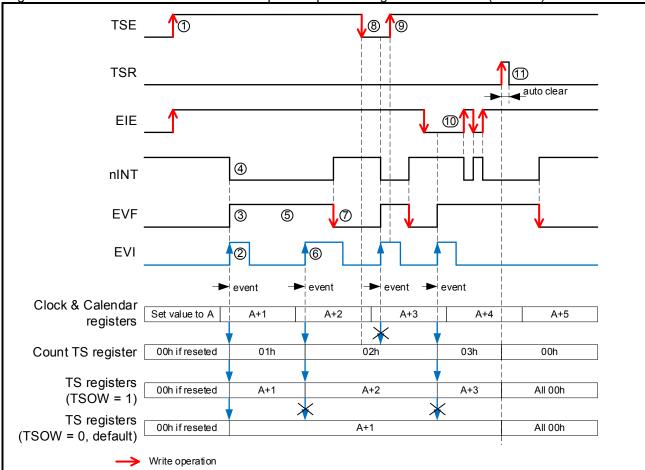

| Figure 7-16 External Event                                                                                                               | 75 |

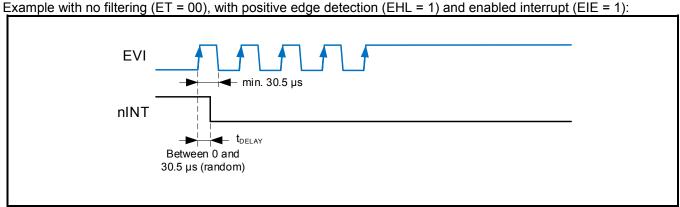

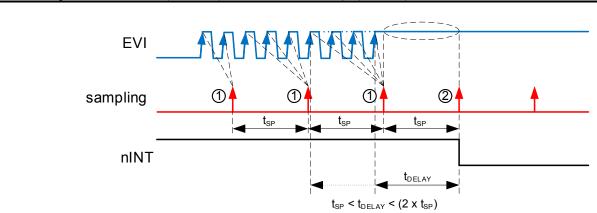

| Figure 7-17 External Event function, No filtering example, EIE = 1                                                                       | 77 |

| Figure 7-18 External Event function, with Filtering example, EIE = 1                                                                     | 77 |

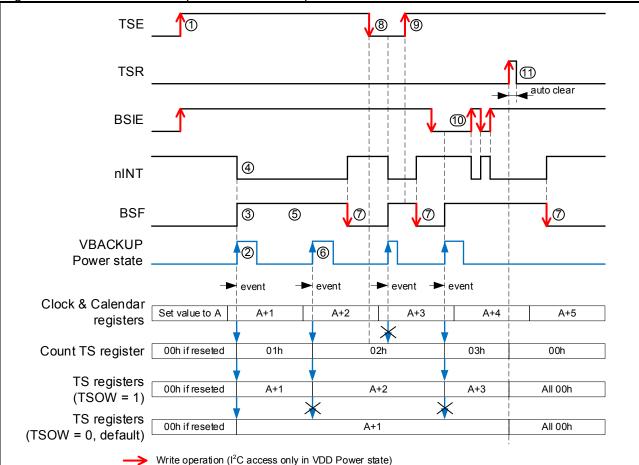

| Figure 7-19 Automatic Backup Switchover                                                                                                  | 79 |

| Figure 7-20 Power On Reset Interrupt                                                                                                     | 81 |

| Figure 7-21 Time Stamp Scheme                                                                                                            | 84 |

| Figure 7-22 Unix Time Counter                                                                                                            | 86 |

| Figure 7-23 Reset bit Function                                                                                                           | 87 |

| Figure 7-24 User Programmable Password Flowchart                                                                                         | 90 |

| Figure 7-25 I <sup>2</sup> C Bit Transfer                                                                                                | 91 |

| Figure 7-26 I <sup>2</sup> C Start and Stop Conditions                                                                                   | 91 |

| Figure 7-27 I <sup>2</sup> C System Configuration                                                                                        | 92 |

| Figure 7-28 I <sup>2</sup> C Acknowledge                                                                                                 | 93 |

| Figure 7-29 I <sup>2</sup> C Write Operation                                                                                             | 94 |

| Figure 7-30 I <sup>2</sup> C Master reads data from slave EM3028 at specific address                                                     | 95 |

| Figure 7-31 I <sup>2</sup> C Master reads data from slave EM3028 immediately after first byte                                            | 95 |

| Figure 8-1 Example of Application                                                                                                        | 97 |

| Figure 10-1 14LD TSSOP Package Outline Drawing        | .100 |

|-------------------------------------------------------|------|

| Figure 10-2 Tape & Reel diagram & orientation on tape | .101 |

# **LIST OF TABLES**

| Table 1 Pin Out description                       | 13 |

|---------------------------------------------------|----|

| Table 2 Absolute maximum ratings                  | 15 |

| Table 3 Operating Conditions                      | 15 |

| Table 4 Electrical Specifications                 | 16 |

| Table 5 Timing Characteristics                    | 20 |

| Table 6 5 I <sup>2</sup> C Timing Characteristics | 21 |

| Table 7 Seconds (0x00h)                           | 22 |

| Table 8 Minutes (0x01h).                          | 22 |

| Table 9 Hours (0x02h).                            | 22 |

| Table 10 Weekday (0x03h)                          | 23 |

| Table 11 Date (0x04h)                             | 23 |

| Table 12 Month (0x05h)                            | 24 |

| Table 13 Year (0x06h)                             | 24 |

| Table 14 Minutes Alarm (0x07h)                    | 25 |

| Table 15 Hours Alarm (0x08h).                     | 25 |

| Table 16 Weekday/Date Alarm (0x09h).              | 26 |

| Table 17 Timer Value 0 (0x0Ah).                   | 27 |

| Table 18 Timer Value 1 (0x0Bh).                   | 27 |

| Table 19 Timer Status 0 (0x0Ch)                   | 28 |

| Table 20 Timer Status 1 shadow (0x0Dh)            | 28 |

| Table 21 Status (0x0Eh).                          | 29 |

| Table 22 Control 1 (0x0Fh)                        | 30 |

| Table 23 Control 2 (0x10h).                       | 31 |

| Table 24 GP bits (0x11h).                         | 32 |

| Table 25 Clock Interrupt Mask (0x12h).            | 32 |

| Table 26 Event Control (0x13h).                   | 33 |

| Table 27 Count TS (0x14h)                         | 34 |

| Table 28 Seconds TS (0x15h).                      | 34 |

| Table 29 Minutes TS (0x16h)                       | 34 |

| Table 30 Hours TS (0x17h)                         | 35 |

| Table 31 Date TS (0x18h)                          | 35 |

| Table 32 Month TS (0x19h).                        | 36 |

| Table 33 Year TS (0x1Ah).                         | 36 |

| Table 34 UNIX Time 0 (0x1Bh)                      | 37 |

| Table 35 UNIX Time 1 (0x1Ch)                      | 37 |

| Table 36 UNIX Time 2 (0x1Dh)                      | 37 |

| Table 37 UNIX Time 3 (0x1Eh)                      | 37 |

| Table 38 User RAM 1 (0x1Fh)                       | 38 |

| Table 39 User RAM 2 (0x20h)                       | 38 |

| Table 40 Password 0 (0x21h)                       | 39 |

| Table 41 Password 1 (0x22h)                       | 39 |

| Table 42 Password 2 (0x23h)                       | 39 |

| Table 43 Password 3 (0x24h)                                                | 39 |

|----------------------------------------------------------------------------|----|

| Table 44 EEPROM Address (0x25h)                                            | 40 |

| Table 45 EEPROM Data (0x26h)                                               | 40 |

| Table 46 EEPROM Commands (0x27h)                                           | 40 |

| Table 47 ID Register (0x28h)                                               | 41 |

| Table 48 EEPROM Reserved (0x2Bh)                                           | 41 |

| Table 49 EEPROM Password Enable (0x30h)                                    | 41 |

| Table 50 EEPROM Password 0 (0x31h)                                         | 42 |

| Table 51 EEPROM Password 1 (0x32h)                                         | 42 |

| Table 52 EEPROM Password 2 (0x33h)                                         | 42 |

| Table 53 EEPROM Password 3 (0x34h)                                         | 42 |

| Table 54 EEPROM FOUT Register (0x35h).                                     | 43 |

| Table 55 EEPROM Offset (0x36h)                                             | 44 |

| Table 56 EEPROM Backup Register (0x37h)                                    | 45 |

| Table 57 EEOffset Value (0x36h. 0x37h)                                     | 46 |

| Table 58 User EEPROM (0x00h to 2Ah).                                       | 46 |

| Table 59 Manufacturer EEPROM (0x2Ch to 2Fh and 38h to 3Fh).                | 46 |

| Table 60 Reset Values; RAM (00h to 3Fh).                                   | 47 |

| Table 61 Configuration EEPROM (0x2Bh and 0x30h to 37h).                    | 48 |

| Table 62 Default values: User EEPROM (0x00h to 2Ah)                        | 48 |

| Table 63 Default values: Manufacturer EEPROM (0x2Ch to 2Fh and 38h to 3Fh) | 48 |

| Table 64 Component list                                                    | 97 |

| Table 65 Ordering Information                                              | 99 |

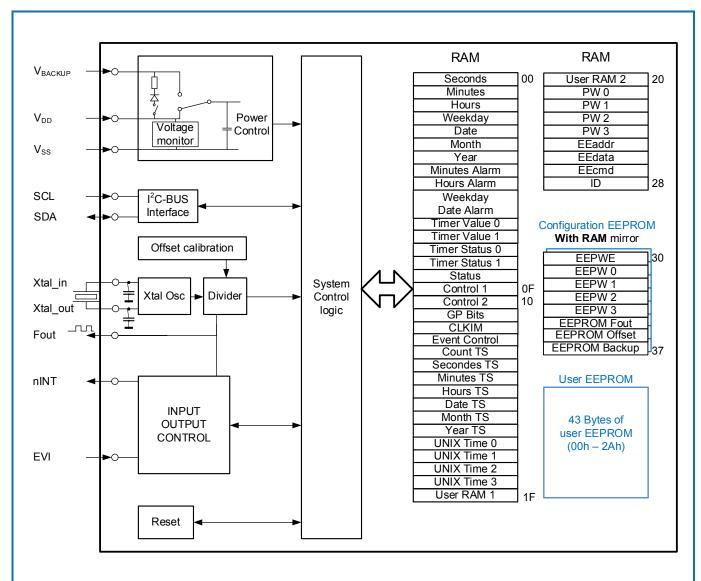

#### 1. PRODUCT DESCRIPTION

The EM3028 is an extreme-low power CMOS based Real-Time with external 32.768 kHz Crystal. It includes an Automatic Backup switchover function with a Trickle charger where the interrupt output on nINT pin is also working in VBACKUP Power state. The clock output on FOUT pin can be enabled normally via command over interface or can be interrupt driven and synchronized clock output enable/disable on FOUT pin can be freely selected. The configuration registers are stored permanently in non-volatile EEPROM and mirrored in RAM in order that the RTC is still configured correctly even after power down. For safety against inadvertent overwriting the time registers and configuration registers can be protected by a User Programmable Password. Additionally, there is an OscOffset value customer use for aging correction.

The EM3028 provides standard Clock & Calendar function including seconds, minutes, hours (12 or 24 h), weekdays, date, months, years (with leap year correction) and interrupt functions for the Periodic Countdown Timer, Periodic Time Update, Alarm, External Event, Automatic Backup Switchover and Power On Reset. All is accessible via I<sup>2</sup>C-bus (2-wire Interface). The interrupt functions and the Time Stamp of the External Event function are also working in VBACKUP Power state. Beside the standard RTC functions a 32-bit UNIX Time counter and 43 Bytes of non-volatile User Memory EEPROM and 2 Bytes of User RAM are provided. A further Byte can be used as User RAM when the Periodic Countdown Timer is not used (Timer Value register 0Ah) and a further Byte when the Alarm function is not used (Alarm register 07h).

#### 1.1. BLOCK DIAGRAM

Figure 1-1 EM3028 Block Diagram

#### 1.2. OPERATING MODES

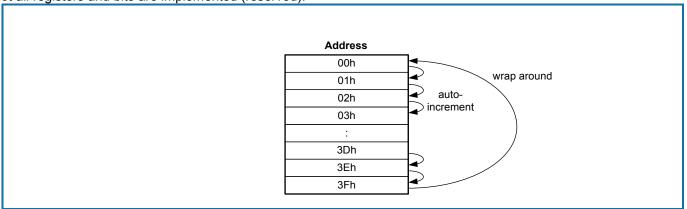

The registers are accessed by selecting a register address and then performing read or write operations. Multiple reads or writes may be executed in a single access, with the address automatically incrementing after each byte. When address is automatically incremented, wrap around occurs from address 3Fh to address 00h (see Figure 1-2 Address register auto-increment). All registers are designed as addressable 8-bit registers despite the fact that not all registers and bits are implemented (reserved).

Figure 1-2 Address register auto-increment

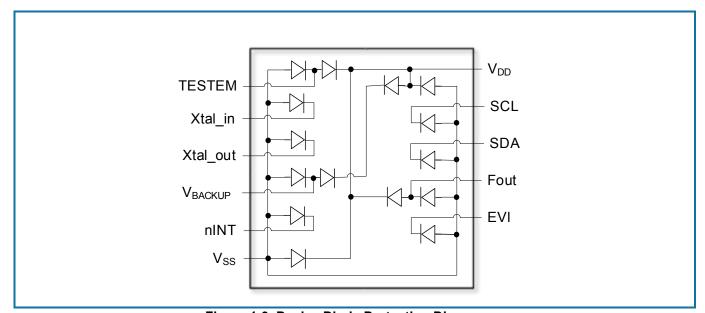

#### 1.2.1. DEVICE PROTECTION

Figure 1-3 Device Diode Protection Diagram

# 1.2.2. REGISTER ORGANIZATION

- RAM Registers at addresses 00h to 28h are accessed by selecting a register address and then performing read or write operations. Multiple reads or writes may be executed in a single access, with the address automatically incrementing after each byte.

- The Configuration Registers at addresses 2Bh and 30h to 37h are memorized in EEPROM and mirrored in RAM.

- There are 43 bytes of non-volatile user memory EEPROM at addresses 00h to 2Ah for general use.

The following tables summarize the function of each register.

# **REGISTER CONVENTIONS**

The conventions in this table serve as a key for the register overview and individual register diagrams:

| Convention (Conv.) | Description                                                       |

|--------------------|-------------------------------------------------------------------|

| R                  | Read only. Writing to this register has no effect.                |

| W                  | Write only. Returns 0 when read.                                  |

| R/WP               | Read: Always readable. Write: Can be write-protected by password. |

| WP                 | Write only. It can be write-protected by password.                |

| Prot.              | Protected. Not readable, but normal address pointer incrementing. |

# 1.2.3. REGISTER OVERVIEW

After reset, all registers are set according to Table in section Register Reset Values Summary.

Register Definitions; RAM, Address 00h to 3Fh:

| Address | Function                     | Conv.  | Bit 7          | Bit 6        | Bit 5 | Bit 4 | Bit 3  | Bit 2 | Bit 1 | Bit 0 |  |

|---------|------------------------------|--------|----------------|--------------|-------|-------|--------|-------|-------|-------|--|

| 00h     | Seconds                      | R/WP   | 0              | 40           | 20    | 10    | 8      | 4     | 2     | 1     |  |

| 01h     | Minutes                      | R/WP   | 0              | 40           | 20    | 10    | 8      | 4     | 2     | 1     |  |

| 02h     | Hours (24 hour)              | R/WP   | 0              | 0            | 20    | 10    | 8      | 4     | 2     | 1     |  |

| 0211    | Hours (12 hour)              | IN/VVF | O              |              | AMPM  | 10    | 8      | 4     | 2     | 1     |  |

| 03h     | Weekday                      | R/WP   | 0              | 0            | 0     | 0     | 0      | 4     | 2     | 1     |  |

| 04h     | Date                         | R/WP   | 0              | 0            | 20    | 10    | 8      | 4     | 2     | 1     |  |

| 05h     | Month                        | R/WP   | 0              | 0            | 0     | 10    | 8      | 4     | 2     | 1     |  |

| 06h     | Year                         | R/WP   | 80             | 40           | 20    | 10    | 8      | 4     | 2     | 1     |  |

| 07h     | Minutes Alarm                | R/WP   | AE_M           | 40           | 20    | 10    | 8      | 4     | 2     | 1     |  |

|         | Hours Alarm                  |        |                |              | 20    | 10    | 8      | 4     | 2     | 1     |  |

| 08h     | (24h)                        | R/WP   | AE_H           | 0            |       | 10    |        |       |       | '     |  |

| 33      | Hours Alarm                  |        | ,              | -            | AMPM  | 10    | 8      | 4     | 2     | 1     |  |

|         | (12h)                        |        |                |              | _     | _     | _      | 4     | 2     | 4     |  |

| 09h     | Weekday Alarm                | R/WP   | AE_WD          | 0            | 0     | 0     | 0      | 4     | 2     | 1     |  |

| 0.4.6   | Date Alarm                   | DAVD   | 400            | 0.4          | 20    | 10    | 8      | 4     | 2     | 1     |  |

| 0Ah     | Timer Value 0                | R/WP   | 128            | 64           | 32    | 16    | 8      | 4     | 2     | 1     |  |

| 0Bh     | Timer Value 1 Timer Status 0 | R/WP   | 0              | 0            | 0     | 0     | 2048   | 1024  | 512   | 256   |  |

| 0Ch     | Timer Status 0               | R      | 128            | 64           | 32    | 16    | 8      | 4     | 2     | 1     |  |

| 0Dh     | shadow                       | R      | 0              | 0            | 0     | 0     | 2048   | 1024  | 512   | 256   |  |

| 0Eh     | Status                       | R/WP   | EEbusy         | CLKF         | BSF   | UF    | TF     | AF    | EVF   | PORF  |  |

| 0Fh     | Control 1                    | R/WP   | TRPT           | -            | WADA  | USEL  | EERD   | TE    | Т     | D     |  |

| 10h     | Control 2                    | R/WP   | TSE            | CLKIE        | UIE   | TIE   | AIE    | EIE   | 12_24 | RESET |  |

| 11h     | GP Bits                      | R/WP   | -              | GP6          | GP5   | GP4   | GP3    | GP2   | GP1   | GP0   |  |

| 12h     | Clock Int. Mask              | R/WP   | -              | -            | -     | -     | CEIE   | CAIE  | CTIE  | CUIE  |  |

| 13h     | Event Control                | R/WP   | 0              | EHL          | Е     | T     | 0      | TSR   | TSOW  | TSS   |  |

| 14h     | Count TS                     | R      | 128            | 64           | 32    | 16    | 8      | 4     | 2     | 1     |  |

| 15h     | Seconds TS                   | R      | 0              | 40           | 20    | 10    | 8      | 4     | 2     | 1     |  |

| 16h     | Minutes TS                   | R      | 0              | 40           | 20    | 10    | 8      | 4     | 2     | 1     |  |

| 475     | Haves TC                     | -      | _              | _            | 20    | 10    | 8      | 4     | 2     | 1     |  |

| 17h     | Hours TS                     | R      | 0              | 0            | AMPM  | 10    | 8      | 4     | 2     | 1     |  |

| 18h     | Date TS                      | R      | 0              | 0            | 20    | 10    | 8      | 4     | 2     | 1     |  |

| 19h     | Month TS                     | R      | 0              | 0            | 0     | 10    | 8      | 4     | 2     | 1     |  |

| 1Ah     | Year TS                      | R      | 80             | 40           | 20    | 10    | 8      | 4     | 2     | 1     |  |

| 1Bh     | UNIX Time 0                  | R/WP   | UNIX 0 [7:0]   |              |       |       |        |       |       |       |  |

| 1Ch     | UNIX Time 1                  | R/WP   | UNIX 1 [15:8]  |              |       |       |        |       |       |       |  |

| 1Dh     | UNIX Time 2                  | R/WP   | UNIX 2 [23:16] |              |       |       |        |       |       |       |  |

| 1Eh     | UNIX Time 3                  | R/WP   | UNIX 3 [31:24] |              |       |       |        |       |       |       |  |

| 1Fh     | User RAM 1                   | R/WP   | RAM 1 data     |              |       |       |        |       |       |       |  |

| 20h     | User RAM 2                   | R/WP   | RAM 2 data     |              |       |       |        |       |       |       |  |

| 21h     | Password 0                   | W      | PW 0 [7:0]     |              |       |       |        |       |       |       |  |

| 22h     | Password 1                   | W      |                |              |       | PW 1  | [15:8] |       |       |       |  |

| 23h     | Password 2                   | W      |                | PW 2 [23:16] |       |       |        |       |       |       |  |

| Address     | Function     | Conv. | Bit 7                                                            | Bit 6        | Bit 5      | Bit 4        | Bit 3      | Bit 2       | Bit 1      | Bit 0 |  |

|-------------|--------------|-------|------------------------------------------------------------------|--------------|------------|--------------|------------|-------------|------------|-------|--|

| 24h         | Password 3   | W     |                                                                  | PW 3 [31:24] |            |              |            |             |            |       |  |

| 25h         | EEPROM Addr. | R/WP  |                                                                  | EEaddr       |            |              |            |             |            |       |  |

| 26h         | EEPROM Data  | R/WP  | EEdata                                                           |              |            |              |            |             |            |       |  |

| 27h         | EEPROM Com.  | WP    | EEcmd                                                            |              |            |              |            |             |            |       |  |

| 28h         | ID           | R     |                                                                  | Н            | D          |              |            | V           | ID         |       |  |

| 29h and 2Ah | Non-existing |       |                                                                  | Non-exis     | ting RAM a | ddress (will | be skipped | d by addres | s pointer) |       |  |

| 2Ch to 2Fh  | RESERVED     | Prot. | RESERVED (not readable, but normal address pointer incrementing) |              |            |              |            |             |            |       |  |

| 38h to 3Fh  | RESERVED     | Prot. | RESERVED (not readable, but normal address pointer incrementing) |              |            |              |            |             |            |       |  |

<sup>-</sup> Bit not implemented. Will return a 0 when read.

Register Definitions; Configuration EEPROM with RAM mirror, Address 2Bh and 30h to 37h:

| Address       | Function                | Conv.    | Bit 7            | Bit 6 | Bit 5 | Bit 4  | Bit 3     | Bit 2 | Bit 1 | Bit 0 |

|---------------|-------------------------|----------|------------------|-------|-------|--------|-----------|-------|-------|-------|

| 2Bh           | EEPROM<br>RESERVED      | R/WP     |                  |       |       |        |           |       |       |       |

| 30h           | EEPROM PW<br>Enable     | R/WP     |                  |       |       |        |           |       |       |       |

| 31h           | EEPROM<br>Password 0    | WP       | EEPW 0 [7:0]     |       |       |        |           |       |       |       |

| 32h           | EEPROM<br>Password 1    | WP       | EEPW 1 [15:8]    |       |       |        |           |       |       |       |

| 33h           | EEPROM<br>Password 2    | WP       | EEPW 2 [23:16]   |       |       |        |           |       |       |       |

| 34h           | EEPROM<br>Password 3    | WP       |                  |       |       | EEPW 3 | 3 [31:24] |       |       |       |

| 35h           | EEPROM<br>FOUT          | R/WP     | CLKOE            | CLKSY | -     |        | PORIE     |       | FD    |       |

| 36h           | EEPROM<br>Offset        | R/WP     | EEOffset [8:1]   |       |       |        |           |       |       |       |

| 37h           | EEPROM<br>Backup        | R/WP     | EEOffs<br>et [0] | BSIE  | TCE   | FEDE   | BS        | SM    | TC    | CR    |

| t not impleme | nted. Will return a 0 w | hen read | l                |       |       |        |           |       |       |       |

# Register Definitions; User EEPROM, Address 00h to 2Ah:

| Address    | Function                  | Conv. | Bit 7 | Bit 6 | Bit 5    | Bit 4      | Bit 3        | Bit 2 | Bit 1 | Bit 0 |

|------------|---------------------------|-------|-------|-------|----------|------------|--------------|-------|-------|-------|

| 00h to 2Ah | User EEPROM<br>(43 Bytes) | R/WP  |       |       | 43 Bytes | of non-vol | atile User E | EPROM |       |       |

# Register Definitions; Manufacturer EEPROM, Address 2Ch to 2Fh and 38h to 3Fh:

| Address    | Function           | Conv. | Bit 7    | Bit 6    | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |  |

|------------|--------------------|-------|----------|----------|-------|-------|-------|-------|-------|-------|--|

| 2Ch to 2Fh | EEPROM<br>RESERVED | Prot. | RESERVED |          |       |       |       |       |       |       |  |

| 38h to 3Fh | EEPROM<br>RESERVED | Prot. |          | RESERVED |       |       |       |       |       |       |  |

# 2. HANDLING PROCEDURES

This device has built-in protection against high static voltages or electric fields; however, anti-static precautions must be taken as for any other CMOS component. Unless otherwise specified, proper operation can only occur when all terminal voltages are kept within the voltage range. Unused inputs must always be tied to a defined logic voltage level.

# 3. PIN DESCRIPTION

|     | PIN             | I/O 7     | ГҮРЕ                                 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                           |

|-----|-----------------|-----------|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NO. | NAME            | DIRECTION | SUPPLY                               |                                                                                                                                                                                                                                                                                                                                                                                                       |

| 1   | $V_{DD}$        |           |                                      | Positive power supply                                                                                                                                                                                                                                                                                                                                                                                 |

| 2   | VBAckup         |           |                                      | Battery Supply Voltage. When the backup switchover function is not needed, $V_{BACKUP}$ must be tied to $V_{SS}$ with a 10 k $\Omega$ resistor.                                                                                                                                                                                                                                                       |

| 3   | V <sub>SS</sub> |           | $V_{SS}$                             | Ground                                                                                                                                                                                                                                                                                                                                                                                                |

| 4   | TESTEM          | 1         | $V_{DD}$                             | Test input for factory test. Connect to Vss                                                                                                                                                                                                                                                                                                                                                           |

| 5   | Xtal_out        | 0         |                                      | Oscillator output Wire length between quartz and package shall be minimized.                                                                                                                                                                                                                                                                                                                          |

| 6   | Xtal_in         | I         |                                      | Oscillator input Wire length between quartz and package shall be minimized.                                                                                                                                                                                                                                                                                                                           |

| 7   | SDA             | I/O       | $V_{DD}$                             | I <sup>2</sup> C Serial Data Input-Output; open-drain; requires pull-up resistor. In VBACKUP Power state, the SDA pin is disabled (high impedance).                                                                                                                                                                                                                                                   |

| 8   | SCL             | I         | $V_{DD}$                             | I <sup>2</sup> C Serial Clock Input; requires pull-up resistor. In VBACKUP Power state, the SCL pin is disabled.                                                                                                                                                                                                                                                                                      |

| 9   | nINT            | 0         | V <sub>DD</sub> or<br>VBACKUP        | Interrupt Output; open-drain; active LOW; requires pull-up resistor; used to output Periodic Countdown Timer, Periodic Time Update, Alarm, External Event, Automatic Backup Switchover and Power On Reset Interrupt signals. Interrupt output also in VBACKUP Power state.                                                                                                                            |

| 10  | EVI             | I         | V <sub>DD</sub> <b>or</b><br>Vbackup | External Event Input; used for interrupt generation, interrupt driven clock output and time stamp function. Remains active also in VBACKUP Power state. This pin should not be left floating.                                                                                                                                                                                                         |

| 11  | FOUT            | 0         | $V_{DD}$                             | Clock Output; push-pull; Normal and Interrupt driven clock output can be activated concurrently.                                                                                                                                                                                                                                                                                                      |

|     |                 |           |                                      | <ol> <li>Normal clock output is controlled by the CLKOE bit. When<br/>CLKOE is set to 1 (default), the FOUT pin drives the square<br/>wave on the FOUT pin. When CLKOE bit is set to 0, the FOUT<br/>pin is LOW.</li> </ol>                                                                                                                                                                           |

|     |                 |           |                                      | <ol> <li>Interrupt driven clock output is controlled by an interrupt event.     When CLKIE is set to 1 the occurrence of the interrupt selected     in the Clock Interrupt Mask Register (12h) allows the square     wave output on the FOUT pin. Writing 0 to CLKIE will disable     new interrupts from driving square wave on FOUT. When CLKF     flag is cleared, the FOUT pin is LOW.</li> </ol> |

|     |                 |           |                                      | Depending of the settings in the XO field, the FOUT pin can drive the square wave of 32.768 kHz (default), 8192 Hz, 1024 Hz, 64 Hz, 32 Hz or 1 Hz, or the predefined periodic countdown timer interrupt. When XO field is 111 the FOUT pin is LOW.                                                                                                                                                    |

|     |                 |           |                                      | When CLKSY bit set to 1, the enabling and disabling of the clock output is synchronized. CLKSY has no effect on the timer interrupt signal.                                                                                                                                                                                                                                                           |

|     |                 |           |                                      | In VBACKUP Power state, the FOUT pin is LOW.                                                                                                                                                                                                                                                                                                                                                          |

**Table 1 Pin Out description**

# 4. PACKAGE / PIN OUT / MARKING

Figure 4-1 14LD TSSOP

Figure 4-2 Laser marking 14LD TSSOP

# 5. ELECTRICAL SPECIFICATIONS

# **5.1. ABSOLUTE MAXIMUM RATINGS**

| PARAMETER                                                                         | VAL   | VALUE |    |  |  |

|-----------------------------------------------------------------------------------|-------|-------|----|--|--|

| PARAMETER                                                                         | MIN   | MAX   |    |  |  |

| Power supply V <sub>DD</sub>                                                      | -0.3  | +6.0  | V  |  |  |

| Storage Temperature Range (T <sub>STG</sub> )                                     | -50   | +150  | °C |  |  |

| Electrostatic discharge to ANSI/ESDA/JEDEC JS-001 for HBM                         | -2000 | +2000 | V  |  |  |

| Latch-up testing, according to JESD78., Class I (room temperature), level A (100) | -100  | +100  | mA |  |  |

**Table 2 Absolute maximum ratings**

Stresses above these listed maximum ratings may cause permanent damages to the device. Exposure beyond specified operating conditions may affect device reliability or cause malfunction.

**Warning**: The device is not functional when exposed to light. When a non-packaged version is used, it is mandatory to protect the device from light.

# **5.2. OPERATING CONDITIONS**

| PARAMETER              | SYMBOL   | MIN | TYP | MAX | UNIT                 |

|------------------------|----------|-----|-----|-----|----------------------|

| Supply voltage         | $V_{DD}$ | 1.1 |     | 5.5 | V                    |

| Battery Supply voltage | VBACKUP  | 1.1 |     | 5.5 | V                    |

| Temperature range      | $T_R$    | -40 |     | +85 | $^{\circ}\mathrm{C}$ |

**Table 3 Operating Conditions**

15

#### **5.3. ELECTRICAL CHARACTERISTICS**

Unless otherwise specified:  $V_{DD}$  = 1.2 to 5.5V,  $T_A$ =-40 to +85°C for min max specifications and  $T_A$ = 25°C,  $V_{DD}$  = 3.0V, Rs=40k $\Omega$  for typical specifications.

| OSCILLATOR PARAMETER                                                                                       | SYMBOL                   | CONDITIONS                                                                    | MIN | TYP  | MAX | UNI<br>T |

|------------------------------------------------------------------------------------------------------------|--------------------------|-------------------------------------------------------------------------------|-----|------|-----|----------|

| SUPPLIES                                                                                                   |                          |                                                                               |     |      |     |          |

|                                                                                                            |                          | Time-keeping mode <sup>(1)</sup>                                              | 1.1 |      | 5.5 |          |

| Power Supply Voltage                                                                                       | $V_{DD}$                 | I <sup>2</sup> C-bus (100 kHz)                                                | 1.2 |      | 5.5 | V        |

|                                                                                                            |                          | I <sup>2</sup> C-bus (400 kHz)                                                | 2.0 |      | 5.5 |          |

| Backup Supply Voltage                                                                                      | $V_{BACKUP}$             |                                                                               | 1.1 |      | 5.5 | V        |

| V <sub>DD</sub> supply current timekeeping                                                                 |                          | $V_{DD} = 1.1 V(2)$                                                           |     | 40   | 300 |          |

| I <sup>2</sup> C-bus inactive, FOUT                                                                        | I <sub>VDD</sub>         | $V_{DD} = 3.0 V(2)$                                                           |     | 40   | 330 | nA       |

| disabled, average current                                                                                  |                          | $V_{DD} = 5.0 V(2)$                                                           |     | 40   | 400 |          |

| V <sub>DD</sub> supply current during                                                                      |                          | $V_{DD} = 1.2 \text{ V, SCL} = 100 \text{ kHz}^{(3)}$                         |     | 2    | 15  |          |

| I <sup>2</sup> C burst read/write, FOUT                                                                    | I <sub>VDD:I2C</sub>     | $V_{DD} = 3.0 \text{ V, SCL} = 400 \text{ kHz}^{(3)}$                         |     | 5    | 40  | μA       |

| disabled                                                                                                   |                          | $V_{DD} = 5.0 \text{ V, SCL} = 400 \text{ kHz}^{(3)}$                         |     | 7    | 60  |          |

| V <sub>DD</sub> supply current in level<br>switching mode<br>I <sup>2</sup> C-bus inactive, FOUT disabled  | IVDD:LEVEL               | V <sub>DD</sub> = 3.0 V, T <sub>A</sub> = 25°C                                |     | 115  | 180 | nA       |

| V <sub>DD</sub> supply current in direct<br>switching mode<br>I <sup>2</sup> C-bus inactive, FOUT disabled | IVDD:DIRECT              | V <sub>DD</sub> = 3.0 V, T <sub>A</sub> = 25°C                                |     | 95   | 150 | nA       |

|                                                                                                            | ΔI <sub>VDD:CK32</sub>   | $V_{DD}$ = 3.0 V, $F_{OUT}$ = 32.768 kHz, $C_L$ = 10 pF                       |     | 1    |     | μA       |

| Additional V <sub>DD</sub> supply current <sup>(4)</sup>                                                   | ΔI <sub>VDD:CK1024</sub> | $V_{DD} = 3.0 \text{ V}, F_{OUT} = 1024 \text{ Hz},$<br>$C_L = 10 \text{ pF}$ |     | 30   |     | nA       |

|                                                                                                            | ΔI <sub>VDD:CK1</sub>    | $V_{DD} = 3.0 \text{ V}, F_{OUT} = 1 \text{ Hz},$<br>$C_L = 10 \text{ pF}$    |     | 0.03 |     | nA       |

<sup>(1)</sup> Clocks operating and RAM registers retained.

$\Delta I_{VDD}$  =  $C_L \times V_{DD} \times f_{OUT}$ , e.g.  $\Delta I_{VDD}$  = 10 pF x 3.0 V x 32'768 Hz = 980 nA ≈ 1  $\mu$ A

Table 4 Electrical Specifications

Typical characteristics in direct switching mode:  $I_{VDD:LEVEL} @ V_{DD} = 2.1 \text{ V}$  and  $I_{VBACKUP}$  vs.  $V_{BACKUP}$ ,  $T_A = 25^{\circ}\text{C}$ ,  $I^2\text{C}$ -bus inactive, FOUT disabled.

<sup>(2)</sup> All inputs and outputs are at 0 V or  $V_{\text{\tiny DD}}.$

<sup>(3) 2.2</sup>k pull-up resistors on SCL/SDA, excluding external peripherals and pull-up resistor current. All other inputs (besides SDA and SCL) are at 0 V or VDD. Test conditions: Continuous burst read/write, 55h data pattern, 25 μs between each data byte, 20 pF load on each bus nin

<sup>&</sup>lt;sup>(4)</sup>When FOUT is enabled the additional  $V_{DD}$  supply current  $\Delta I_{VDD}$  can be calculated as follows:

Figure 5-1 Battery Consumption, Topr =25°C, VDD=2.1V, VDD > Vth\_swbat, Level Switching

Unless otherwise specified:  $V_{DD}$  = 1.2 to 5.5V,  $T_A$ =-40 to +85°C for min max specifications and  $T_A$ = 25°C,  $V_{DD}$  = 3.0V,  $R_S$ =40k $\Omega$  for typical specifications.

| Rs=40kΩ for typical specificatio<br>OSCILLATOR PARAMETER | SYMBOL                      | CONDITIONS                                                     | MIN                 | TYP  | MAX                 | UNIT |

|----------------------------------------------------------|-----------------------------|----------------------------------------------------------------|---------------------|------|---------------------|------|

| INPUTS                                                   |                             |                                                                |                     |      |                     |      |

| LOW level input voltage                                  | V <sub>IL</sub>             | V <sub>DD</sub> = 1.1 V to 5.5 V                               |                     |      | 0.2 V <sub>DD</sub> | V    |

| HIGH level input voltage                                 | V <sub>IH</sub>             | Pins: SCL, SDA, EVI                                            | 0.8 V <sub>DD</sub> |      | 1.2 100             | V    |

| Input leakage current                                    | I <sub>ILEAK</sub>          | $V_{SS} \le V_I \le V_{DD}$                                    | -0.5                |      | 0.5                 | μA   |

| Input capacitance                                        | Cı                          | V <sub>DD</sub> = 3.0 V, T <sub>A</sub> = 25°C<br>f = 1MHz     |                     |      | 7                   | pF   |

| Outputs                                                  |                             |                                                                |                     | •    |                     |      |

|                                                          |                             | $V_{DD} = 1.1 \text{ V}, I_{OL} = -0.1 \text{ mA}$             |                     |      | 0.1                 |      |

| LOW level output voltage                                 | $V_{OL:CLK}$                | $V_{DD} = 3.0 \text{ V}, I_{OL} = -1.0 \text{ mA}$             |                     |      | 0.3                 | V    |

| FOUT                                                     |                             | $V_{DD} = 5.0 \text{ V}, I_{OL} = -1.0 \text{ mA}$             |                     |      | 0.5                 |      |

| IIIOII I a cal a catacata calta a a                      |                             | V <sub>DD</sub> = 1.1 V, I <sub>OH</sub> = 0.1 mA              | 1.0                 |      |                     |      |

| HIGH level output voltage                                | $V_{OH:CLK}$                | V <sub>DD</sub> = 3.0 V, I <sub>OH</sub> = 1.0 mA              | 2.7                 |      |                     | V    |

| FOUT                                                     |                             | V <sub>DD</sub> = 5.0 V, I <sub>OH</sub> = 1.0 mA              | 4.5                 |      |                     |      |

|                                                          |                             | $V_{DD} = 1.2 \text{ V}, I_{OL} = -0.5 \text{ mA}$             |                     |      | 0.4                 |      |

| LOW level output voltage                                 | $V_{OL}$                    | $V_{DD} = 3.0 \text{ V}, I_{OL} = -3.0 \text{ mA}$             |                     |      | 0.4                 | V    |

| Pins: SDA, nINT                                          |                             | $V_{DD} = 5.0 \text{ V}, I_{OL} = -3.0 \text{ mA}$             |                     |      | 0.3                 | 1    |

| Output leakage current                                   | I <sub>OLEAK</sub>          | $V_O = V_{DD}$ or $V_{SS}$                                     | -0.5                |      | 0.5                 | μΑ   |

| Output capacitance                                       | Соит                        | $V_{DD} = 3.0 \text{ V}, T_A = 25^{\circ}\text{C}$<br>f = 1MHz |                     |      | 7                   | pF   |

| Power On Reset                                           |                             |                                                                |                     |      |                     |      |

| POR detection threshold                                  | $V_{POR}$                   |                                                                | 0.75                | 0.8  | 0.85                | V    |

| Trickle charger                                          |                             |                                                                |                     |      |                     |      |

|                                                          | TCR 1 kΩ                    |                                                                | 2                   | 3    | 4                   |      |

| Current limiting resistors                               | TCR 3 kΩ                    | $V_{DD} = 5.0 \text{ V}, V_{BACKUP} = 3.0 \text{ V},$          | 4.5                 | 5.5  | 6.25                | kΩ   |

|                                                          | TCR 6 kΩ<br>TCR 11 kΩ       | including internal schottky diode                              | 7.5<br>12.5         | 9.3  | 11.6<br>17.4        |      |

| Switchover                                               | TCR TT KΩ                   |                                                                | 12.5                | 15.7 | 17.4                |      |

| Switchover hysteresis in direct                          |                             | V <sub>DD</sub> with respect to V <sub>BACKUP</sub> =          |                     |      |                     |      |

| switching mode                                           | V <sub>HYST:DSM</sub>       | 3.0 V, T <sub>OPR</sub> = -40°C to +85°C                       |                     | 60   |                     | mV   |

| Backup switchover threshold voltage                      | $V_{DDSW}$                  | Relative to V <sub>DD</sub>                                    | 1.8                 | 2.0  | 2.2                 | V    |

| Switchover hysteresis in level                           | 1/                          | V <sub>DD</sub> with respect to V <sub>BACKUP</sub> =          |                     | 100  |                     | \ /  |

| switching mode                                           | V <sub>HYST:LSM</sub>       | 3.0 V, T <sub>OPR</sub> = -40°C to +85°C                       |                     | 100  |                     | mV   |

| <b>EEPROM Characteristics</b>                            |                             |                                                                |                     |      |                     |      |

| Read voltage                                             | $V_{READ}$                  |                                                                | 1.1                 |      |                     |      |

| Programming voltage                                      | $V_{PROG}$                  |                                                                | 1.5                 |      |                     | V    |

|                                                          |                             |                                                                |                     |      |                     | ] V  |

| Write voltage,                                           | Vwrite                      |                                                                | $V_{DDSW}$          |      |                     |      |

| Write voltage, only for voltage ≥ V <sub>DDSW</sub>      | Vwrite                      |                                                                | V <sub>DDSW</sub>   |      |                     |      |

| Write voltage,                                           | Vwrite<br>T <sub>PROG</sub> |                                                                | V <sub>DDSW</sub>   |      | 30                  | ms   |

## **5.4. OSCILLATOR CHARACTERISTICS**

Unless otherwise specified:  $V_{DD}$  = 1.2 to 5.5V,  $T_{A}$ =-40 to +85°C for min max specifications and  $T_{A}$ = 25°C,  $V_{DD}$  = 3.0V,  $R_{S}$ =40k $\Omega$  for typical specifications.

| NS-40K12 for typical specifica                                | ations.              |                                                                                     |                       |                                                    |                                    |           |

|---------------------------------------------------------------|----------------------|-------------------------------------------------------------------------------------|-----------------------|----------------------------------------------------|------------------------------------|-----------|

| OSCILLATOR PARAMETER                                          | SYMBOL               | CONDITIONS                                                                          | MIN                   | TYP                                                | MAX                                | UNIT      |

| XTAL GENERAL                                                  |                      |                                                                                     |                       |                                                    |                                    |           |

| Crystal Frequency                                             | F                    |                                                                                     |                       | 32.768                                             |                                    | kHz       |

| Oscillator start-up time at V <sub>DD</sub> = 3.0 V           | tstart               | T <sub>A</sub> = 25°C                                                               |                       | 0.5                                                | 1                                  | s         |

| Oscillator start-up voltage                                   | VSTART               | T <sub>A</sub> = 25°C                                                               |                       |                                                    | 3                                  | S         |

| Frequency vs. voltage Characteristics                         | Δf/V                 | $V_{DD}$ = 1.1 V to 5.5 V<br>$T_A$ = 25°C                                           |                       | 0.5                                                |                                    | ppm/<br>V |

| V <sub>DD</sub> rising slew rate                              | $V_{DDR}$            | V <sub>DD</sub> = 1.1 V to 3.6 V<br>V <sub>DD</sub> = 3.6 V to 5.5 V                |                       |                                                    | 2.5<br>3.8                         | V/ms      |

| V <sub>DD</sub> falling slew rate                             | $V_{DDF}$            | V <sub>DD</sub> = 5.5 V to 1.1 V                                                    |                       |                                                    | 2.2                                | V/ms      |

| FOUT duty cycle                                               | Δ <sub>FOUT</sub>    | $V_{DD} = 1.1 \text{ V to } 5.5 \text{ V}, F_{OUT} = 32.768 \text{ kHz}$            | 40                    | 50                                                 | 60                                 | %         |

| XTAL FREQUENCY CHARAC                                         | CTERISTICS           |                                                                                     |                       |                                                    |                                    |           |

| Frequency accuracy                                            | ΔF/F                 | T <sub>A</sub> = 25°C                                                               |                       | ±5                                                 |                                    | ppm       |

| Frequency vs. temperature characteristics                     | ΔF/F <sub>TOPR</sub> | $T_{OPR} = -40^{\circ}\text{C to } +85^{\circ}\text{C}$<br>$V_{DD} = 3.0 \text{ V}$ | -0.035 <sup>ppr</sup> | <sup>n</sup> /∘ <sub>C</sub> ² (T <sub>OPR</sub> - | T <sub>0</sub> ) <sup>2</sup> ±10% | ppm       |

| Turnover temperature                                          | T <sub>0</sub>       |                                                                                     |                       | +25 ±5                                             |                                    | °C        |

| Aging first year max.                                         | ΔF/F                 | $T_A = 25^{\circ}C, V_{DD} = 3.0 V$                                                 |                       |                                                    | ±3                                 | ppm       |

| FREQUENCY OFFSET CORF                                         | RECTION              |                                                                                     |                       |                                                    |                                    |           |

| OFFSET correction: Min. corr. step (LSB) and Max. corr. Range | Δt/t                 | T <sub>A</sub> = -40°C to +85°C                                                     | ±0.954                |                                                    | +243.2/<br>-244.1                  | ppm       |

| Achievable time accuracy                                      | Δt/t                 | Calibrated at an initial temperature and voltage                                    | -0.48                 |                                                    | +0.48                              | ppm       |

Integrated Cxtal\_in and Cxtal\_out tolerance:  $C_{Xtal} \min = (0.9 * C_{Xtal} \text{ typ}) - 0.5$   $C_{Xtal} \max = (1.1 * C_{Xtal} \text{ typ}) + 0.5$

Crystal Reference: Micro Crystal CM7V-T1A

web: www.microcrystal.com

Figure 5-2 XTAL Frequency vs Temperature Characteristics

#### 5.5. TIMING CHARACTERISTICS

Unless otherwise specified: VDD = 1.2 to 5.5V, TA=-40 to +85°C for min max specifications and TA= 25°C and 3.0V for typical specifications

| PARAMETER                                                        | SYMBOL            | CONDITIONS   | MIN | TYP | MAX | UNIT |

|------------------------------------------------------------------|-------------------|--------------|-----|-----|-----|------|

| V <sub>DD</sub> rising slew rate at initial power on reset (POR) | $V_{\text{DDR1}}$ | FOUT enabled | 0.1 |     | 1   | V/ms |

| Oscillator start-up time at V <sub>DD</sub> = 3.0 V              | <b>t</b> start    | (CLKOE = 1)  |     | 0.5 | 3   | S    |

| First refreshment time                                           | t <sub>REFR</sub> | (            |     | 66  |     | ms   |

**Table 5 Timing Characteristics**

#### **5.5.1. POWER ON**

The following Figure describes the power on AC electrical characteristics for the FOUT pin. The clock output signal on FOUT pin is enabled by the CLKOE bit (EEPROM 35h), see also **Use of the Configuration EEPROM WITH RAM MIRROR Registers**.

## Power On AC Electrical Characteristics:

- (EEPROM 35h) after the start-up time tSTART = 0.5 s (FOUT can also be LOW, when selecting FD = 111).

- ② If the CLKOE bit (EEPROM 35h) was set to 0 beforehand (in EEPROM), the CLKOE bit in the RAM is set to 0 after the start-up time tSTART = 0.5 s and the first refreshment time t<sub>REFR</sub> = ~66 ms, and the FOUT signal goes LOW. Or else, if the CLKOE bit (EEPROM 35h) was set to 1 beforehand (in EEPROM), the CLKOE bit in the RAM is set to 1 after the start-up time tSTART = 0.5 s and the first refreshment time t<sub>REFR</sub> = ~66 ms, and the FOUT pin is driving the frequency selected by the FD field.

Figure 5-3 Power On Timing Diagram

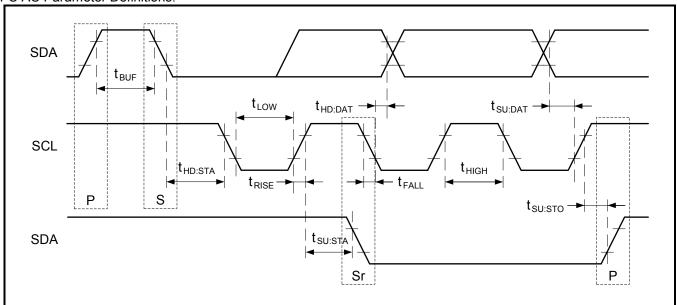

## 5.5.2. I<sup>2</sup>C-BUS CHARACTERISTICS

The following Figure and Table describe the I<sup>2</sup>C AC electrical parameters.

# I<sup>2</sup>C AC Parameter Definitions:

Figure 5-4 I<sup>2</sup>C BUS Timing Diagram

| PARAMETER                                    | SYMBOL              | CONDITIONS              | MIN | TYP | MAX  | UNIT  |

|----------------------------------------------|---------------------|-------------------------|-----|-----|------|-------|

| SCL input clock frequency                    | f <sub>SCL</sub>    | V <sub>DD</sub> ≥ 1.2 V | 0   |     | 100  | kHz   |

| Set input clock frequency                    | ISCL                | V <sub>DD</sub> ≥ 2.0 V | 0   |     | 400  | KI IZ |

| Low period of SCL clock                      | t <sub>LOW</sub>    | V <sub>DD</sub> ≥ 1.2 V | 4.7 |     |      | μs    |

| Low ported of CCL Glock                      | · LOVV              | V <sub>DD</sub> ≥ 2.0 V | 1.3 |     |      | μО    |

| High period of SCL clock                     | t <sub>HIGH</sub>   | V <sub>DD</sub> ≥ 1.2 V | 4.0 |     |      | μs    |

| Thigh period of OOL Glook                    | THIGH               | V <sub>DD</sub> ≥ 2.0 V | 0.6 |     |      | μο    |

| Rise time of SDA and SCL                     | t <sub>RISE</sub>   | V <sub>DD</sub> ≥ 1.2 V |     |     | 1000 | ns    |

|                                              | TRIOL               | V <sub>DD</sub> ≥ 2.0 V |     |     | 300  |       |

| Fall time of SDA and SCL                     | t <sub>FALL</sub>   | V <sub>DD</sub> ≥ 1.2 V |     |     | 300  | ns    |

|                                              | -1712               | V <sub>DD</sub> ≥ 2.0 V |     |     | 300  |       |

| START condition hold time                    | t <sub>HD:STA</sub> | V <sub>DD</sub> ≥ 1.2 V | 4.0 |     |      | μs    |

|                                              | 41.5.61.7           | V <sub>DD</sub> ≥ 2.0 V | 0.6 |     |      | 1 -   |

| START condition setup time                   | t <sub>SU:STA</sub> | V <sub>DD</sub> ≥ 1.2 V | 4.7 |     |      | μs    |

|                                              |                     | V <sub>DD</sub> ≥ 2.0 V | 0.6 |     |      | 1 -   |

| SDA setup time                               | <b>t</b> su:dat     | V <sub>DD</sub> ≥ 1.2 V | 250 |     |      | ns    |

|                                              |                     | V <sub>DD</sub> ≥ 2.0 V | 100 |     |      |       |

| SDA hold time                                | t <sub>HD:DAT</sub> | V <sub>DD</sub> ≥ 1.2 V | 0   |     |      | μs    |

|                                              |                     | V <sub>DD</sub> ≥ 2.0 V | 0   |     |      | 1 -   |

| STOP condition setup time                    | t <sub>su:sto</sub> | V <sub>DD</sub> ≥ 1.2 V | 4.0 |     |      | μs    |

|                                              | -55.510             | V <sub>DD</sub> ≥ 2.0 V | 0.6 |     |      | ļ , · |

| Bus free time before a new transmission      | t <sub>BUF</sub>    | V <sub>DD</sub> ≥ 1.2 V | 4.7 |     |      | μs    |

| S = Start condition, Sr = Repeated Start cor |                     | V <sub>DD</sub> ≥ 2.0 V | 1.3 |     |      | P     |

Table 6 5 I<sup>2</sup>C Timing Characteristics

#### Caution<sup>.</sup>

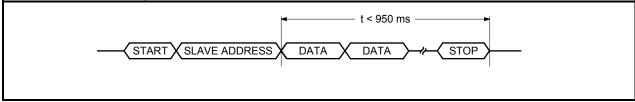

When accessing the EM3028, all communication from transmitting the Start condition to transmitting the Stop condition after access should be completed within 950 ms.

If such communication requires 950 ms or longer, the I<sup>2</sup>C bus interface is reset by the internal bus timeout function.

## 6. PRODUCT CONFIGURATION

#### **6.1. CLOCK REGISTERS**

00h - Seconds. This register holds the count of seconds, in two binary coded decimal (BCD) digits. Values will be from 00 to 59. Read: Always readable. Write: Can be write-protected by password.

|         |          |       |          |                                                                                                                                  |         | pa.ee. |            |       |       |       |  |

|---------|----------|-------|----------|----------------------------------------------------------------------------------------------------------------------------------|---------|--------|------------|-------|-------|-------|--|

| Address | Function | Conv. | Bit 7    | Bit 6                                                                                                                            | Bit 5   | Bit 4  | Bit 3      | Bit 2 | Bit 1 | Bit 0 |  |

| 00h     | Seconds  | R/WP  | 0        | 40                                                                                                                               | 20      | 10     | 8          | 4     | 2     | 1     |  |

| 0011    | Reset    |       | 0        | 0                                                                                                                                | 0       | 0      | 0          | 0     | 0     | 0     |  |

|         |          |       |          |                                                                                                                                  |         |        |            |       |       |       |  |

| Bit     | Symbol   |       | Value    |                                                                                                                                  |         | D      | escription |       |       |       |  |

| 7       | 0        |       | 0        | Read only. Al                                                                                                                    | ways 0. |        |            |       |       |       |  |

| 6:0     | Seconds  |       | 00 to 59 | Holds the count of seconds, coded in BCD format. When 1 is written to the RESET bit the Seconds register value remains unchanged |         |        |            |       |       |       |  |

Table 7 Seconds (0x00h).

01h - Minutes. This register holds the count of minutes, in two binary coded decimal (BCD) digits. Values will be from 00 to 59. Read: Always readable. Write: Can be write-protected by password.

| non ob to 55. Nead. Always readable. Write. Oan be write-protected by password. |          |       |          |                                                  |       |       |            |       |       |       |

|---------------------------------------------------------------------------------|----------|-------|----------|--------------------------------------------------|-------|-------|------------|-------|-------|-------|

| Address                                                                         | Function | Conv. | Bit 7    | Bit 6                                            | Bit 5 | Bit 4 | Bit 3      | Bit 2 | Bit 1 | Bit 0 |

| 01h                                                                             | Minutes  | R/WP  | 0        | 40                                               | 20    | 10    | 8          | 4     | 2     | 1     |

| 0111                                                                            | Reset    |       | 0        | 0                                                | 0     | 0     | 0          | 0     | 0     | 0     |