# **EM66xx IN-CIRCUIT EMULATOR**

# **HARDWARE DESCRIPTION**

# Version 3.0

December 2010

| 1. EM66xx Emulator hardware description       |    |

|-----------------------------------------------|----|

| 1.1. Warning                                  | 4  |

| 1.2. Front panel                              | 5  |

| 1.2.1. ICE connector pin-out                  |    |

| 1.2.2. LCD Connector pin-out **               |    |

| 1.3. Rear Panel                               |    |

| 1.4. Switch settings                          |    |

| 2. General operational points                 |    |

| 2.1. Using external clock                     | 9  |

| 2.2. Option Registers                         | 9  |

| 2.3. Watchdog timers                          |    |

| 2.4. Synchronous and asynchronous modes       | 9  |

| 3. Configuration resistors.                   | 10 |

| 3.1. Port Configuration                       | 10 |

| 3.2. Pull-up and Pull-down Resistor placement | 10 |

| 4. Emulator configurations                    | 11 |

| 4.1. EM6607                                   | 11 |

| 4.2. EM6621, EM6622, EM6625, EM6626           | 12 |

| 4.3. EM6627                                   | 13 |

| 4.4. EM6580, EM6680, EM6682                   | 14 |

| 5. EM66xx emulator upgrade procedure          | 18 |

# 1. EM66xx Emulator hardware description

# 1.1. Warning

When connecting or disconnecting the EM66xx emulator to the target system or when connecting headers or LCD's to the connectors on the front panel it is essential that the emulator is powered off. Failure to do this could result in damage to the emulator hardware, which would require the system being returned to EM Microelectronic for repair.

Please also be aware that when Port pins are set to input, any voltage greater that the V I/O level that has been set (See Below) can also damage the emulator. This includes transitory switching spikes as well as sustained over voltage conditions. It is recommended that any high levels driven onto the emulator port pins for sustained periods should be set to approximately 10 percent below the set V I/O level. So for example, if V I/O is set to 3.0V then to drive a high on to PortB the recommended level would be around 2.7V. Alternatively V I/O can be set above the switching level applied to the emulator to say 3.3V in the above example.

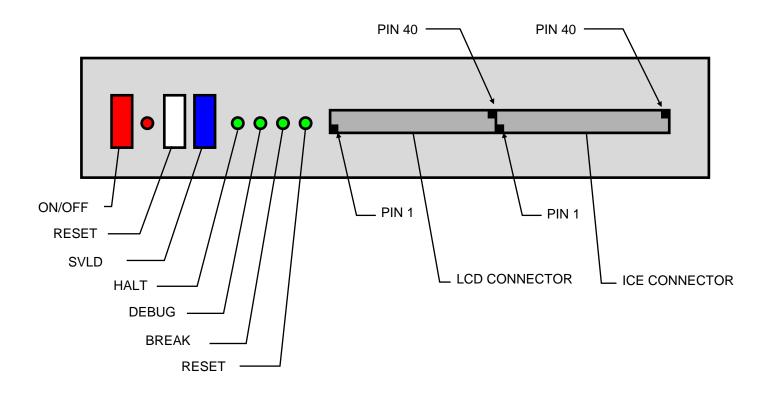

# 1.2. Front panel

The RESET switch will perform a hardware reset to the entire emulator, however it will not reinitialise peripheral RAM or trace and program memory. It will set peripheral registers to their reset values as specified in the respective microcontroller data sheets.

The SVLD (Supply Voltage Level Detect) switch will return a failing result during software control of the SVLD peripheral, i.e. simulating a battery or supply low condition.

The four green LED's indicate the following conditions. HALT LED will light when a HALT instruction is executed. DEBUG LED will light when connection to the host is made and the core is in a BREAK state. When the core is running this LED will go out. BREAK LED will light when the connection to the host has been made. If this LED in not illuminated then there is no communication with the monitor. RESET LED will light when a hardware reset is performed.

| 1.2.1. | ICE | connector | pin-out |

|--------|-----|-----------|---------|

|--------|-----|-----------|---------|

| PIN | SIGNAL             | PIN              | SIGNAL             |

|-----|--------------------|------------------|--------------------|

| 1   | PORTA 0            | 21               | BUZZER             |

| 2   | PORTA 1            | 22               | ADC VGND           |

| 3   | PORTA 2            | 23               | CLOCK OUT          |

| 4   | PORTA 3            | 24               | ADC VREF           |

| 5   | PORTB 0            | 25               | PORTS 3            |

| 6   | PORTB 1            | 26               | ADC Cin            |

| 7   | PORTB 2            | 27               | PORTS 0            |

| 8   | PORTB 3            | 28               | ADC Bin            |

| 9   | PORTC 0            | 29               |                    |

| 10  | PORTC 1            | PORTC 1 30 ADC A |                    |

| 11  | PORTC 2            | 31               |                    |

| 12  | PORTC 3            | 32               | GROUND             |

| 13  | PORTD 0            | 33               | OSC IN             |

| 14  | PORTD 1            | 34               | PORTS 1 / SWB CLK  |

| 15  | PORTD 2            | 35               | VIOSET             |

| 16  | PORTD 3            | 36               | PORTS 2 / SWB DATA |

| 17  | RESET IN           | 37               | PORTE 0            |

| 18  | GROUND             | 38               | PORTE 1            |

| 19  | STROBE / RESET OUT | 39               | PORTE 2            |

| 20  | ADC Din            | 40               | PORTE 3            |

# 1.2.2. LCD Connector pin-out \*\*

| PIN | SIGNAL        | PIN | SIGNAL |

|-----|---------------|-----|--------|

| 1   | NO CONNECTION | 21  | COL 13 |

| 2   | NO CONNECTION | 22  | COL 14 |

| 3   | ROW 4         | 23  | COL 15 |

| 4   | ROW 3         | 24  | COL 16 |

| 5   | ROW 2         | 25  | COL 17 |

| 6   | ROW 1         | 26  | COL 18 |

| 7   | GROUND        | 27  | COL 19 |

| 8   | NO CONNECTION | 28  | COL 20 |

| 9   | COL 1         | 29  | COL 21 |

| 10  | COL 2         | 30  | COL 22 |

| 11  | COL 3         | 31  | COL 23 |

| 12  | COL 4         | 32  | COL 24 |

| 13  | COL 5         | 33  | COL 25 |

| 14  | COL 6         | 34  | COL 26 |

| 15  | COL 7         | 35  | COL 27 |

| 16  | COL 8         | 36  | COL 28 |

| 17  | COL 9         | 37  | COL 29 |

| 18  | COL 10        | 38  | COL 30 |

| 19  | COL 11        | 39  | COL 31 |

| 20  | COL 12        | 40  | COL 32 |

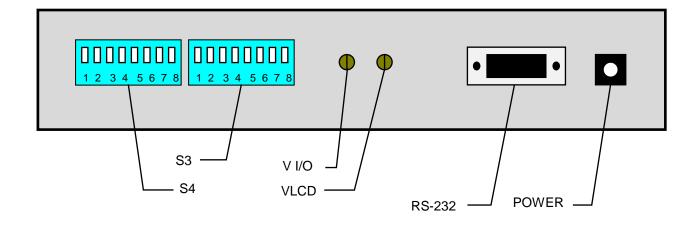

# 1.3. Rear Panel

The V I/O adjustment allows the user to change the output drive level and input switching level of the V66xx emulator. Thus, if it is required that the emulator operate in a system where the supply voltage is 0 to 3 volts, then the inputs and outputs can be easily configured for this. The input switching level is CMOS compatible and is around 0.5Vdd. So if V I/O is set to 3v then when input a Port will change from a logic 0 to a logic 1 at about 1.5V. In output mode a logic 0 will be approximately 0V and a logic 1 will be at approximately 3.0V.

In order to set V I/O it is necessary to do the following. Set an output line to drive a logic 1, e.g. PortB-1. Then connect a voltmeter between PortB-1 and Ground (emulator side), turning the V I/O with a pot trimmer will cause the output on the port pin to change, until the required level is obtained. It is possible to vary the output drive between 1.5V and 5.5V.

Adjustment of the LCD drive levels are also possible using the VLCD trimmer pot. The output levels can be set using a similar method to that outlined above, i.e. by setting a particular LCD column line high and measuring with a voltmeter. The VLCD level can also be changed dynamically such that when display data is being updated and the emulator is in RUN mode, it is possible to vary VLCD and observe what is happening to the contrast on the display.

# The POWER supply of the emulator is 12V DC/1A

# 1.4. Switch settings

When switch settings are changed an emulator hardware reset should be performed or the emulator should be powered off then on again.

| SWITCH | FUNCTION                        | DEFAULT      | POSITION |

|--------|---------------------------------|--------------|----------|

| S4-1   | RESERVED                        | RESERVED     | UP       |

| S4-2   | RESERVED                        | RESERVED     | UP       |

| S4-3   | RS-232 BAUD RATE (19.2K / 9.6K) | 19.2K        | UP       |

| S4-4   | WATCHDOG ENABLE                 | ENABLED      | UP       |

| S4-5   | BREAK PERIPHERY                 | DISABLED     | UP       |

| S4-6   | RESERVED                        | RESERVED     | UP       |

| S4-7   | RESERVED                        | RESERVED     | UP       |

| S4-8   | RESERVED                        | RESERVED     | UP       |

| S3-1   | CORE CLOCK                      | DISABLED     | UP       |

| S3-2   | OSCILLATOR 0                    | INTERNAL     | UP       |

| S3-3   | OSCILLATOR 1                    | OSCILLATOR   | UP       |

| S3-4   | CLOCK DIVIDER                   | DIVIDED BY 1 | UP       |

| S3-5   | CLOCK DIVIDER                   | DIVIDED BY 1 | UP       |

| S3-6   | RESERVED                        | RESERVED     | UP       |

| S3-7   | RESERVED                        | RESERVED     | UP       |

| S3-8   | INTERNAL BUZZER                 | DISABLED     | UP       |

Note the following:

During BREAK, if switch S4-5 is in the up position the core will stop execution of instructions but the peripheral components such as timers and serial interfaces will continue to run. If this switch is set down then all peripheral functions will stop when the Core BREAKs.

Switch S4-4 enables or disable the internal watchdog timer. This will also be disabled on BREAK if S4-5 is in the down position.

Switch S3-1 will output the internal core clock out to the target system if required. However, this switch should not be put into the down position on a no load situation.

Switch S3-8 will route the buzzer tone to an internal buzzer.

Switches S3-4 and S3-5 can be set to give a core clock frequency which is a division of the fundamental oscillator fitted in the emulator. Have a look into the specific emulator to find the clock table configuration.

Switches S3-2 and S3-3 can be set to select the clock mode. The following table shows the three available modes. The default mode is the internal oscillator.

| S3-2 | S3-3 | SELECTION           | EM66xx         |

|------|------|---------------------|----------------|

| UP   | UP   | INTERNAL OSCILLATOR | D <sub>3</sub> |

| DOWN | UP   | EXTERNAL CLOCK      | D <sub>3</sub> |

| UP   | DOWN | NOT AVAILABLE       |                |

| DOWN | DOWN | SYNTHESISER         |                |

# 2. General operational points.

# 2.1. Using external clock

An external clock can be used to control the EM66xx core (see previous table for switches selection). The clock signal must be between 0 to 5Volts and a 50% duty cycle.

# 2.2. Option Registers

The EM66xx range of microcontrollers has two methods of customising functions; mask options and option registers. In the emulator only some of these functions are directly implemented. For example the selection of pull-up and pulldown resistors at port pins is implemented directly on the emulator system board as outlined in the following section. The pull resistors can be disable by software (if the register exist in the memory map of the EM66xx microcontrollers).

However those functions that are internal (i.e. those not associated with I/O) such as interrupt edge selection, debouncer selection, etc, are implemented by manipulation of the corresponding option register as they would be in the normal operation of a microcontroller. Those option registers that change I/O characteristics still exist within the emulator and can be written and read as normal, but they will perform no function otherwise. The exception to this is the EM6622 emulation system, which due to system constraints, does not implement those option registers that change pull-up and pulldown selects. Reading these registers will always produce a value of '1111' on the data bus no matter what the written value was.

# 2.3. Watchdog timers

Only the logic watchdog is implemented in the EM66xx emulation system. This watchdog will generate a reset signal to the core every 2.5 - 3.5 seconds at a system clock of 32.768khz. If the watchdog is enabled on the emulator and the system is running in asynchronous mode then the core will be reset periodically. This will also be the case when the emulator is in BREAK mode, resulting in all internal registers being set to their default values as defined in the specification for each microcontroller.

If the watchdog switch is enabled and the emulator is in synchronous mode then during a BREAK the watchdog will not generate a reset since all peripheral timing functions are statically timed with the core. If the watchdog is disabled and the core is running asynchronously then no reset will be generated however all other timers will be active as normal during a BREAK.

The other watchdog in the EM range of microcontrollers is the analogue watchdog, which supervises the oscillator. If oscillation stops then a reset will be generated (see the appropriate microcontroller specification). This function is not implemented in the emulator.

# 2.4. Synchronous and asynchronous modes

As outlined above, if the switch enabling synchronous mode is activated then all peripheral functions will stop when the Core BREAKs. This is a useful feature if one wishes to examine the contents of counter registers for example. The exception to this is if a LCD controller is being emulated. Since a frame the emulator for the display generates clock then if the periphery is running synchronously with the core then the frame clock will also stop and the display will fade. It is recommended that when using the LCD controller that the periphery is run asynchronously from the core with the logic watchdog disabled.

# 3. Configuration resistors.

# 3.1. Port Configuration

The table below gives the reference designators on the emulator PCB of the pull-up and pulldown resistors for the port configurations on the EM66xx emulator. Any value can be fitted to give the desired configuration, but since these are 1206 SMD resistors it recommended that only EM Microelectronic personnel or someone qualified in SMD fabrication should attempt configuration. You should also find the location for each level shifters used for each ports.

|          |      | Level S | Shifters |      |      |      |      | Pull Re | sistors |      |      |      |

|----------|------|---------|----------|------|------|------|------|---------|---------|------|------|------|

|          | Bit3 | Bit2    | Bit1     | Bit0 | Bit3 | Bit3 | Bit2 | Bit2    | Bit1    | Bit1 | Bit0 | Bit0 |

|          |      |         |          |      | Up   | Down | Up   | Down    | Up      | Down | Up   | Down |

| PortA    | U63  | U62     | U61      | U60  | R4   | R20  | R3   | R19     | R1      | R17  | R2   | R18  |

| PortB    | U12  | U11     | U9       | U8   | R8   | R24  | R7   | R23     | R5      | R21  | R6   | R22  |

| PortC    | U15  | U15     | U14      | U14  | R12  | R28  | R11  | R27     | R9      | R25  | R10  | R26  |

| PortD    | U17  | U17     | U16      | U16  | R16  | R32  | R15  | R31     | R13     | R29  | R14  | R30  |

| PortE    | U58  | U57     | U56      | U55  | R152 | R156 | R151 | R155    | R150    | R154 | R149 | R153 |

| PortS/PP | U7   | U6      | U6       | U50  | R34  | R38  | R36  | R40     | R37     | R41  | R35  | R39  |

|          | N/A  |         |          |      |      | N/A  | N/A  | N/A     | N/A     | N/A  | N/A  | N/A  |

| STRB     | U18  | N/A     | N/A      | N/A  | N/A  | N/A  | N/A  | N/A     | N/A     | N/A  | N/A  | N/A  |

| RESET    | U19  | N/A     | N/A      | N/A  | N/A  | N/A  | N/A  | N/A     | N/A     | N/A  | N/A  | N/A  |

# 3.2. Pull-up and Pull-down Resistor placement.

The following representation shows the positions of the configuration resistors given in the table above. Reference designators are also shown on the silk screen of the PCB.

| 2  | R  |   | R  | R  | R   | R   | R   | R   | R  | R  |   | R  | ſ |

|----|----|---|----|----|-----|-----|-----|-----|----|----|---|----|---|

| 13 | 29 |   | 30 | 14 | 150 | 154 | 153 | 149 | 35 | 39 |   | 34 |   |

|    |    |   |    |    |     |     |     |     |    |    |   |    |   |

| R  | R  |   | R  | R  | R   | R   | R   | R   | R  | R  | ] | R  | I |

| 15 | 31 |   | 32 | 16 | 151 | 155 | 156 | 152 | 36 | 40 |   | 37 |   |

|    |    |   |    |    |     |     |     |     |    |    | _ |    |   |

| R  | R  |   | R  | R  | R   | R   | R   | R   | R  | R  |   | R  |   |

| 1  | 17 |   | 18 | 2  | 5   | 21  | 22  | 6   | 9  | 25 |   | 10 |   |

|    |    |   |    |    |     |     |     |     |    |    |   |    |   |

|    | [  | 1 |    | [  | ſ   | Γ   |     | [   |    | ſ  | 1 |    | T |

| R  | R  |   | R  | R  | R   | R   | R   | R   | R  | R  |   | R  |   |

| 19 | 3  |   | 20 | 4  | 7   | 23  | 24  | 8   | 11 | 27 |   | 12 |   |

# 4. Emulator configurations

# 4.1. EM6607

|            |           | Level S   | Shifters  |      |      |      |      | Pull Re | sistors |      |      |      |

|------------|-----------|-----------|-----------|------|------|------|------|---------|---------|------|------|------|

|            | Bit3      | Bit2      | Bit1      | Bit0 | Bit3 | Bit3 | Bit2 | Bit2    | Bit1    | Bit1 | Bit0 | Bit0 |

|            |           |           |           |      | Up   | Down | Up   | Down    | Up      | Down | Up   | Down |

| PortA      | U63       | U62       | U61       | U60  | R4   | R20  | R3   | R19     | R1      | R17  | R2   | R18  |

| PortB      | U12       | U11       | U9        | U8   | R8   | R24  | R7   | R23     | R5      | R21  | R6   | R22  |

| PortC      | U15       | U15       | U14       | U14  | R12  | R28  | R11  | R27     | R9      | R25  | R10  | R26  |

| PortD      | U17       | U17       | U16       | U16  | R16  | R32  | R15  | R31     | R13     | R29  | R14  | R30  |

| PortE      | U58       | U57       | U56       | U55  | R152 | R156 | R151 | R155    | R150    | R154 | R149 | R153 |

| PortS/PP   | N/A       | N/A       | N/A       | N/A  | N/A  | N/A  | N/A  | N/A     | N/A     | N/A  | N/A  | N/A  |

|            |           | N         | /A        |      | N/A  | N/A  | N/A  | N/A     | N/A     | N/A  | N/A  | N/A  |

| STRB       | U18       | N/A       | N/A       | N/A  | N/A  | N/A  | N/A  | N/A     | N/A     | N/A  | N/A  | N/A  |

| RESET      | U19       | N/A       | N/A       | N/A  | N/A  | N/A  | N/A  | N/A     | N/A     | N/A  | N/A  | N/A  |

| Note: Dofa | It mounte | d Deciete | r oro gro | ,    |      | •    | •    | •       | •       |      |      | •    |

Note: Default mounted Resistor are grey.

Components present on board are:

Jumpers

JP19 & JP20 on Pos. 1-2 JP30–JP35 on Pos. 1-2

### ADC

PAD8 on Pos. U54

Oscillator

U23 32,768KHz

#### Remark & Options:

Use the following table to set the input port A reset Combination option.

| Option | S3-6 S3-7 |      | Function                       |

|--------|-----------|------|--------------------------------|

| А      | Up        | Up   | No Inputs Reset                |

| В      | Down      | Up   | Reset = PA0 * PA1              |

| С      | Up        | Down | Reset = PA0 * PA1 * PA2        |

| D      | Down      | Down | Reset = PA0 * PA1 * PA2 * PA*3 |

SVLD Level implemented on the emulator are (01=1.3V), (10=2V), (11=2.3V). Use the input called SVLD on the ICE board to modify the SVLD level applied.

|             |           | Level S    | Shifters    |      |      | Pull Resistors |      |      |      |      |      |      |

|-------------|-----------|------------|-------------|------|------|----------------|------|------|------|------|------|------|

|             | Bit3      | Bit2       | Bit1        | Bit0 | Bit3 | Bit3           | Bit2 | Bit2 | Bit1 | Bit1 | Bit0 | Bit0 |

|             |           |            |             |      | Up   | Down           | Up   | Down | Up   | Down | Up   | Down |

| PortA       | U63       | U62        | U61         | U60  | R4   | R20            | R3   | R19  | R1   | R17  | R2   | R18  |

| PortB       | U12       | U11        | U9          | U8   | R8   | R24            | R7   | R23  | R5   | R21  | R6   | R22  |

| PortC       | N/A       | N/A        | N/A         | N/A  | N/A  | N/A            | N/A  | N/A  | N/A  | N/A  | N/A  | N/A  |

| PortD       | N/A       | N/A        | N/A         | N/A  | N/A  | N/A            | N/A  | N/A  | N/A  | N/A  | N/A  | N/A  |

| PortE       | N/A       | N/A        | N/A         | N/A  | N/A  | N/A            | N/A  | N/A  | N/A  | N/A  | N/A  | N/A  |

| PortS/PP    | U7        | U6         | U6          | U50  | R34  | R38            | R36  | R40  | R37  | R41  | R35  | R39  |

|             |           | N          | /A          |      | N/A  | N/A            | N/A  | N/A  | N/A  | N/A  | N/A  | N/A  |

| STRB        | U18       | N/A        | N/A         | N/A  | N/A  | N/A            | N/A  | N/A  | N/A  | N/A  | N/A  | N/A  |

| RESET       | U19       | N/A        | N/A         | N/A  | N/A  | N/A            | N/A  | N/A  | N/A  | N/A  | N/A  | N/A  |

| Note: Defau | It mounte | ed Resisto | or are grey | /.   |      |                |      |      |      |      |      |      |

# 4.2. EM6621, EM6622, EM6625, EM6626

Components present on board are:

Jumpers

JP19 & JP20 on Pos. 1-2 JP13 on Pos. 1-2 Oscillator U23 3,2768MHz 6621/22/25/26 U53 4,096 MHz 6625/26

#### Remark & Options:

Options OPTNchOpDPB & OPTNchOpDPS are implemented as follow:

As soon as OPTNchOpDPX[X] is set to 1 and RegXXData[X] value is 1, the port is set as input, the high state must be applied by the pull-up resistor. In case of low state of the RegXXData[X] the port is set as output low.

Due to hardware limitation on port S (only 3 level shifter for 4 pad), if any PortS[2:1] are set as Nchannel open drain with a data set to High, these two ports are configured to inputs.

It's possible to emulate the metal option "MDeb" by using the switch S3-7. CK[11] is used as debouncer clock when the switch is up, whereas CK14 is used when it's down.

On the EM6625 / EM6626, Peripheral Clock is automatically divided to 32kHz:

|      |      |      |      | EM6625 / EM6626 base clock |                 |                 |  |

|------|------|------|------|----------------------------|-----------------|-----------------|--|

| S3-2 | S3-3 | S3-4 | S3-5 | DIVISOR                    | U23 / 32,768KHz | U53 / 4,096 MHz |  |

| UP   | UP   | UP   | UP   | 1                          | 32,768kHz       | -               |  |

| DOWN | DOWN | UP   | DOWN | 2                          | -               | 32 kHz          |  |

| DOWN | DOWN | DOWN | UP   | 1                          | -               | 64 kHz          |  |

| DOWN | DOWN | DOWN | DOWN | 4                          | -               | 128 kHz         |  |

# 4.3. EM6627

|             | Level Shifters |            |             |      |      | Pull Resistors |      |      |      |      |      |      |

|-------------|----------------|------------|-------------|------|------|----------------|------|------|------|------|------|------|

|             | Bit3           | Bit2       | Bit1        | Bit0 | Bit3 | Bit3           | Bit2 | Bit2 | Bit1 | Bit1 | Bit0 | Bit0 |

|             |                |            |             |      | Up   | Down           | Up   | Down | Up   | Down | Up   | Down |

| PortA       | U63            | U62        | U61         | U60  | N/A  | R20            | N/A  | R19  | N/A  | R17  | N/A  | R18  |

| PortB       | U12            | U11        | U9          | U8   | N/A  | R24            | N/A  | R23  | N/A  | R21  | N/A  | R22  |

| PortC       | N/A            | N/A        | N/A         | N/A  | R12  | N/A            | R11  | N/A  | R9   | N/A  | R10  | N/A  |

| PortD       | N/A            | N/A        | N/A         | N/A  | R16  | N/A            | R15  | N/A  | R13  | N/A  | R14  | N/A  |

| PortE       | N/A            | N/A        | N/A         | N/A  | R152 | N/A            | R151 | N/A  | R150 | N/A  | R149 | N/A  |

| PortS/PP    | U7             | U6         | U6          | U50  | N/A  | R38            | N/A  | R40  | N/A  | R41  | N/A  | R39  |

|             |                | N          | /Α          |      | N/A  | N/A            | N/A  | N/A  | N/A  | N/A  | N/A  | N/A  |

| STRB        | U18            | N/A        | N/A         | N/A  | N/A  | N/A            | N/A  | N/A  | N/A  | N/A  | N/A  | N/A  |

| RESET       | U19            | N/A        | N/A         | N/A  | N/A  | N/A            | N/A  | N/A  | N/A  | N/A  | N/A  | N/A  |

| Note: Defau | ult mounte     | ed Resisto | or are grey | /.   |      |                |      |      |      |      |      |      |

Components present on board are:

Jumpers JP19 & JP20 on Pos. 1-2 JP13 on Pos. 1-2 Oscillator U23 3,2768MHz 6627 U53 4,096 MHz 6627

# Remark & Options:

Due to hardware limitation on port S (only 3 level shifter for 4 pad), if any PortS[2:1] are set as Nchannel open drain with a data set to High, these two ports are configured to inputs.

On the EM6627, Peripheral clock is set by the register RegRCSel, refer to EM6627 datasheet for more detail.

|      |      | EM6627 base clock |                 |  |  |  |  |

|------|------|-------------------|-----------------|--|--|--|--|

| S3-4 | S3-5 | U23 / 32,768KHz   | U53 / 4,096 MHz |  |  |  |  |

| UP   | UP   | 32,768kHz         | -               |  |  |  |  |

| UP   | DOWN | -                 | 32 kHz          |  |  |  |  |

| DOWN | UP   | -                 | 128 kHz         |  |  |  |  |

| DOWN | DOWN | -                 | 512 kHz         |  |  |  |  |

RC frequency selection: MRCFrequ

Three registers are used to show the content of the EEPROM value for verification (not applicable on the reel devices). The user should write the value of the desired address into the register 46H in the watch data window when the emulator is in break mode, directly after this write both registers 47H & 48H are updated with the value of the addressed EEprom location. The address writing operation is validated by the return key.

| 🚧 Watch    |      |      |   |   |    |     |       |            |       | × |

|------------|------|------|---|---|----|-----|-------|------------|-------|---|

| WATCH DATA |      |      |   |   |    |     |       | SYMBOLS    |       |   |

| Label      | Addr | Data | R | W | IO | Rel | Match | Label      | Value | ~ |

| Addr46     | 0046 | 0006 |   |   |    |     |       | BATTERY LO | 0006  |   |

| Addr47     | 0047 | 0005 |   |   |    |     |       | BCD HUNDR  | 0007  | - |

| Addr48     | 0048 | 0006 |   |   |    |     |       | BCDO       | 0012  |   |

|            |      |      |   |   |    |     |       | BCD1       | 0013  | × |

### 4.4. EM6580, EM6680, EM6682

|          |      | Level S | Pull Resistors |      |      |      |      |      |      |      |      |      |

|----------|------|---------|----------------|------|------|------|------|------|------|------|------|------|

|          | Bit3 | Bit2    | Bit1           | Bit0 | Bit3 | Bit3 | Bit2 | Bit2 | Bit1 | Bit1 | Bit0 | Bit0 |

|          |      |         |                |      | Up   | Down | Up   | Down | Up   | Down | Up   | Down |

| PortA    | U63  | U62     | U61            | U60  | R4   | R20  | R3   | R19  | R1   | R17  | R2   | R18  |

| PortB    | U12  | U11     | U9             | U8   | R8   | R24  | R7   | R23  | R5   | R21  | R6   | R22  |

| PortC    | U15  | U15     | U14            | U14  | R12  | R28  | R11  | R27  | R9   | R25  | R10  | R26  |

| PortD    | N/A  | N/A     | N/A            | N/A  | N/A  | N/A  | N/A  | N/A  | N/A  | N/A  | N/A  | N/A  |

| PortE    | N/A  | N/A     | N/A            | N/A  | N/A  | N/A  | N/A  | N/A  | N/A  | N/A  | N/A  | N/A  |

| PortS/PP | N/A  | N/A     | N/A            | N/A  | N/A  | N/A  | N/A  | N/A  | N/A  | N/A  | N/A  | N/A  |

|          |      | N       | /A             |      | N/A  |

| STRB     | U18  | N/A     | N/A            | N/A  | N/A  | N/A  | N/A  | N/A  | N/A  | N/A  | N/A  | N/A  |

| RESET    | U19  | N/A     | N/A            | N/A  | N/A  | N/A  | N/A  | N/A  | N/A  | N/A  | N/A  | N/A  |

Note: Default mounted Resistor are grey.

|             | Pull-Down     | Pull-Up |

|-------------|---------------|---------|

| PortA bit 0 | R28           | R2      |

| PortA bit 1 | R27           | R1      |

| PortA bit 2 | R25           | R3      |

| PortA bit 3 | R26           | R4      |

| PortA bit 4 | R24 (default) | R8      |

| PortA bit 5 | R23           | R5      |

Note: R24 or R8 not both at the same time.

#### Components present on board are:

#### Jumpers

JP19 & JP20 on Pos. 1-2 JP30-JP35 on Pos. 1-2

#### ADC

PAD8 on Pos. U54

Oscillator

| U23 | 4.096MHz |

|-----|----------|

| U53 | 8MHz     |

#### Remark & Options:

For the EM6x80, Two ways is available on the emulator to select the desired RC clock frequency. The first solution is by hardware switches which represent the metal option present on the EM6680. S3-6 is used to enable the switches metal option when it's down. Use the following table to select the core clock value:

| Pos. | S3-6 | S3-5 | S3-4 | S3-3 | S3-2 | S3-7 | <b>RC Frequency</b> |

|------|------|------|------|------|------|------|---------------------|

| 1    | Down | Down | Down | Up   | Up   | Х    | 512kHz              |

| 2    | Down | Down | Up   | Up   | Up   | Х    | 256kHz              |

| 3    | Down | Up   | Down | Up   | Up   | Х    | 128kHz              |

| 4    | Down | Up   | Up   | Up   | Up   | UP   | 32kHz               |

| 5    | Down | Up   | Up   | Up   | Up   | Down | 64kHz               |

| 6    | Down | Down | Down | Down | Down | Х    | 800kHz              |

| 7    | Down | Down | Up   | Down | Down | Х    | 400kHz              |

| 8    | Down | Up   | Down | Down | Down | Х    | 200kHz              |

| 9    | Down | Up   | Up   | Down | Down | Up   | 50kHz               |

| 10   | Down | Up   | Up   | Down | Down | Down | 100kHz              |

System clock is automatically set to base frequency like 32 or 50kHz.

The second solution is to keep each S3-6, S3-3, S3-4 in up position and to work only with the register RegMFP1 to adjust the desired RC frequency. If one of the switches is down it force a condition which cannot modify by the register.

| RegMFP1[3] | RegMFP1[2] | RegMFP1[1] | RegMFP1[0] | Frequency of RCclk | Unit |

|------------|------------|------------|------------|--------------------|------|

| Opt[7]     | Opt[6]     | Opt[5]     | Opt[4]     |                    |      |

| 0          | 0          | 0          | 0          | 32.00              | kHz  |

| 0          | 0          | 0          | 1          | 64.00              | kHz  |

| 0          | 0          | 1          | 0          | 128.00             | kHz  |

| 0          | 0          | 1          | 1          | 256.00             | kHz  |

| 0          | 1          | 0          | 0          | 512.00             | kHz  |

| 1          | 0          | 0          | 0          | 50.00              | kHz  |

| 1          | 0          | 0          | 1          | 100.00             | kHz  |

| 1          | 0          | 1          | 0          | 200.00             | kHz  |

| 1          | 0          | 1          | 1          | 400.00             | kHz  |

| 1          | 1          | 0          | 0          | 800.00             | kHz  |

### The following table is showing the possible selection:

RegMFP1[3] bit selects the base frequency, 512kHz or 800kHz.

RegMFP1[2:0] bit select the frequency divider rate, 1, 2, 4, 8, 16.

When the RC frequency is changed the system clock, sysClk, will be automatically close as possible to 32/50 kHz thanks to frequency dividers. It's possible to modify the RC CPU frequency on the fly from 32 to 800kHz.

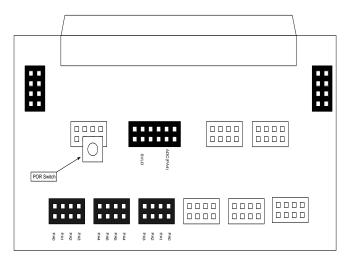

A special Power on Reset switch is implemented on the EME6680 emulator to be able to generate a POR of the device without disconnect the EME6680 from the PC. The Controller is fully reset like a POR, but you don't need to reconnect the emulator and reload the software on it.

Have a look on the following drawing to see where is situated the Switch for POR.

The following switches are used to select different metal options on EM6682.

| Switches | Options                              | Up pos.         | Down pos.    |

|----------|--------------------------------------|-----------------|--------------|

| S4-6     | Counter update option                | RC              | RC/2         |

| S4-7     | SVLD level selection                 | EM6681          | EM6680       |

| S4-8     | Power check selection                | After POR       | After Reset  |

| S3-6     | RC frequency selection mode          | Register option | Metal option |

|          |                                      | as EM6580       | as EM6680    |

| S3-7     | Metal option for frequency selection | 32/50kHz        | 64/100kHz    |

| S3-8     | Power check level selection          | Level 5         | Level 9      |

The ADC/SVLD levels are the following when Vbat is 3V.

| LEVEL  | EM6681     | EM6680     |

|--------|------------|------------|

| 0      | 0.36       | 0.5        |

| 1      | 0.49       | 0.65       |

| 2<br>3 | 0.49       | 0.8        |

| 3      | 0.58       | 0.95       |

| 4      | 0.68       | 1.1        |

| 5      | 0.77       | 1.25       |

| 6      | 0.829      | 1.4        |

| 7      | 0.922      | 1.55       |

| 8      | 1.02       | 1.7        |

| 9      | 1.11       | 1.85       |

| 10     | 1.2        | 2          |

| 11     | 1.3        | 2.15       |

| 12     | 1.39       | 2.30       |

| 13     | 1.48       | 2.45       |

| 14     | 1.57       | 2.60       |

| 15     | 1.66       | 2.75       |

| ADC F  | A4 ExtVche | eck on Din |

| S      | VLD on A   | Nin        |

The two following tables show the metal mask option of the EM6680 which are implemented in register like the EM6580.

| Regis | ter <b>RegMFP0</b> | @ addr | . 121 decin          | nal = 79 hex.                                   |

|-------|--------------------|--------|----------------------|-------------------------------------------------|

| Bit   | Name               | Reset  | eset R/W Description |                                                 |

| 3     | Opt[3]             | 0      | R/W                  | Debouncer clock select "0" = ck[11], "1"=ck[14] |

| 2     | Opt[2]             | 0      | R/W                  | Must be kept to "0"                             |

| 1     | Opt[1]             | 0      | R/W                  | Counter Clock source 7 selection                |

|       |                    |        |                      | "0" PA3/PA4, "1" RCclk/2                        |

| 0     | Opt[0]             | 0      | R/W                  | No effect                                       |

Note: PA4 Pull resistor is located on the EME66xx PCB at location R24 and R8. (Detail on page 22)

The ADC/SVLD Voltage level option is not implemented on the emulator, But to used Bit of the following register are use for emulate some specific metal options.

Bit3 of RegMFP2 is used to select the SCR timing value, IF '1' is set the EM6680 timing value are used, if '0' the EM6682 timing value are set.

Bit2 of RegMFP2 is used to select the length of the counter, If '0' value is set the 10 bits counter is used, if '1' the 9 bits counter is used.

| Regis | ter <b>RegMFP2</b> | @ addr | . 123 decin | nal = 7D hex.                                                                           |

|-------|--------------------|--------|-------------|-----------------------------------------------------------------------------------------|

| Bit   | Name               | Reset  | R/W         | Description                                                                             |

| 3     | Opt[11]            | 3      | R/W         | SCR Timing selection (not implemented on EM6580 silicon)                                |

| 2     | Opt[10]            | 2      | R/W         | Counter length selection '0' is 10bits '1' is 9bits (not implemented on EM6580 silicon) |

| 1     | Opt[9]             | ?      | R/W         | not used                                                                                |

| 0     | Opt[8]             | 0      | R/W         | ADC/SVLD voltage level#15: "0" 2.75v, "1" 3v (not implemented on the emulator)          |

The SCR Timing implemented on the emulator are the following:

| SCRSel [1:0] | OPT[11] set to high | OPT[11] set to low |

|--------------|---------------------|--------------------|

| 00           | 1.82S               | 10.3mS             |

| 01           | 224mS               | 102mS              |

| 10           | 25.6mS              | 910mS              |

| 11           | 2.6mS               | 7.24S              |

Keep Guard: The RegMFPX Registers cannot be used in final ROM version software for EM6680, All three registers are metal option on the EM6680. Please contact EMMicroeletronic for more details.

# 5. EM66xx emulator upgrade procedure

When changing from one emulator system to another or upgrading the emulator the following procedure should be performed.

- 1. Switch off power and remove power cable and RS-232 cable at the rear of the system.

- 2. Remove the four retaining screws on the front panel.

- 3. Remove front panel.

- 4. Slide emulator system board forward and out of the housing.

- 5. At the rear of the board is located an 8 pin DIP module at U42.

- 6. Carefully remove this device from its socket and replace it with the new ROM.

- 7. Slide board back into housing and replace front panel with retaining screws.

- 8. Reconnect power and RS-232 cables.

- 9. Switch on system and ensure that when the monitor connects to the emulator that both the DEBUG and BREAK LED's are illuminated.

- 10. The emulator should now be upgraded.

EM Microelectronic-Marin SA (EM) makes no warranty for the use of its products, other than those expressly contained in the Company's standard warranty which is detailed in EM's General Terms of Sale located on the Company's web site. EM assumes no responsibility for any errors which may appear in this document, reserves the right to change devices or specifications detailed herein at any time without notice, and does not make any commitment to update the information contained herein. No licenses to patents or other intellectual property of EM are granted in connection with the sale of EM products, expressly or by implications. EM's products are not authorized for use as components in life support devices or systems.