Title:

Application Note 608003

# STORAGE ELEMENTS STS/LTS SUPERVISING

Product Family:

Part Number: EM8500

Keywords: Harvesting, Solar, TEG, MPPT, Configuration, Setup, Super capacitors, Secondary Battery, Primary Battery

#### ABSTRACT

The EM8500 offers a NVM containing all the configuration parameters. This document describes how to setup the registers in NVM linked to the storage elements connected to STS & LTS:

EM850X

- Type of battery: rechargeable (secondary battery) or non-rechargeable (primary battery)

- Under voltage protection enabled or disabled

- Voltage level detection:

- o maximum/minimum battery level settings

- o maximum application voltage

- Voltage measurement timing settings

#### ABBREVIATIONS

| NVM     | Non-Volatile-Memory                                                                                                             |

|---------|---------------------------------------------------------------------------------------------------------------------------------|

| MCU     | Microcontroller Unit                                                                                                            |

| STS     | Short term storage element (capacitor connected to VDD_STS)                                                                     |

| LTS     | Long term storage element (rechargeable battery connected to VDD_LTS)                                                           |

| HRV     | Harvester, main source of energy (solar or TEG)                                                                                 |

| TEG     | Thermal Electrical Generator                                                                                                    |

| MPP     | (Maximum Power Point) This operating point is reached when the harvester delivers the maximum power (Pmpp) in a given condition |

| Vmpp    | HRV output voltage at MPP                                                                                                       |

| Vov     | HRV open voltage (when the EM8500 DCDC converter is disabled)                                                                   |

| BAT_LOW | Flag indicating that the battery is in under-voltage condition                                                                  |

| HRV_LOW | Flag indicating that the HRV is under the minimum power level (HRV low mode when at 1)                                          |

| VLD     | Voltage Level Detector                                                                                                          |

| Vref    | Voltage level detector reference level                                                                                          |

| Vivi    | Voltage level detector LSB (71.88mV)                                                                                            |

| Vbat    | Battery voltage connected to VDD_LTS                                                                                            |

| VSUP    | Main output supply for application                                                                                              |

| VAUX[i] | 2 independent auxiliary supplies for application                                                                                |

| Csup    | Decoupling capacitor on VSUP                                                                                                    |

| Caux[i] | 3 decoupling capacitors on VAUX[i]                                                                                              |

## 1 SCOPE

The EM8500 addresses two main types of mass storage elements connected to LTS:

- 1. Rechargeable

- a. secondary battery

- b. or super capacitor

- 2. Non-rechargeable for battery life time enhancement (so called primary cell mode)

- a. primary battery

On STS side, a standard capacitor in the range of 10 u F to few 100 u F is connected.

The EM8500 has several registers to setup the storage elements supervising:

- 1. Type of LTS used

- 2. Under and over voltage protection level of LTS settings

- 3. Regulation voltage level of STS when disconnected from LTS

- 4. Period of voltages measurement settings

| The following | radictore | are involved | for that action: |

|---------------|-----------|--------------|------------------|

| The following | registers | are involveu | IOI mai action.  |

| Register name        | Address | Description                                                                                                                                                                                                                                   |

|----------------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| reg_lts_cfg          | 0x06    | <i>prim_cell_connect</i> : force the connection of STS to LTS in primary cell<br>mode when at '1'<br><i>prim_cell</i> : set the device in primary cell mode when '1'<br><i>no_bat_protect</i> : under voltage protection disabled when at '1' |

| reg_v_bat_max_hi     | 0x07    | Absolute maximum voltage level of the battery                                                                                                                                                                                                 |

| reg_v_bat_max_lo     | 0x08    | Maximum voltage of the battery, form an hysteresis with v_bat_max_hi                                                                                                                                                                          |

| reg_v_bat_min_hi_dis | 0x09    | Minimum battery and application voltage when STS and LTS are disconnected, form an hysteresis with <b>v_bat_min_lo</b>                                                                                                                        |

| reg_v_bat_min_hi_con | 0x0A    | Minimum battery and application voltage when STS and LTS are connected, form an hysteresis with <b>v_bat_min_lo</b>                                                                                                                           |

| reg_v_bat_min_lo     | 0x0B    | Absolute minimum value of the battery and the application                                                                                                                                                                                     |

| reg_v_apl_max_hi     | 0x0C    | Absolute maximum voltage of the application                                                                                                                                                                                                   |

| reg_v_apl_max_lo     | 0x0D    | Maximum voltage of the application, form an hysteresis with<br>v_apl_max_hi                                                                                                                                                                   |

| reg_t_sts_period     | 0x02    | Period between two voltage level measurements of STS, used only when STS and LTS are disconnected                                                                                                                                             |

| reg_t_lts_period     | 0x03    | Period between two voltage level measurements of LTS                                                                                                                                                                                          |

| reg_t_hrv_low_cfg    | 0x17    | <i>t_lts_hrv_low_period</i> : Define the period between two voltage level measurements of LTS in HRV low mode                                                                                                                                 |

Table 1: List of Registers Related to Storage Elements Supervising

The default value after reset or start-up of the registers listed in Table 1 is contained in a NVM memory at the following related addresses:

| Register name        | Register<br>Address | Related add | ress in NVM |

|----------------------|---------------------|-------------|-------------|

| reg_lts_cfg          | 0x06                | eeprom6     | 0x46        |

| reg_v_bat_max_hi     | 0x07                | eeprom7     | 0x47        |

| reg_v_bat_max_lo     | 0x08                | eeprom8     | 0x48        |

| reg_v_bat_min_hi_dis | 0x09                | eeprom9     | 0x49        |

| reg_v_bat_min_hi_con | 0x0A                | eeprom10    | 0x4A        |

| reg_v_bat_min_lo     | 0x0B                | eeprom11    | 0x4B        |

| reg_v_apl_max_hi     | 0x0C                | eeprom12    | 0x4C        |

| reg_v_apl_max_lo     | 0x0D                | eeprom13    | 0x4D        |

| reg_t_sts_period     | 0x02                | eeprom2     | 0x42        |

| reg_t_lts_period     | 0x03                | eeprom3     | 0x43        |

| reg_t_hrv_low_cfg    | 0x17                | eeprom23    | 0x57        |

Table 2: Mapping of Registers in EEPROM

Note: offset between the register addresses and related address in NVM is 0x40

## 2 SUPERVISING REGISTERS SETTINGS SEQUENCE

We advise calculating the different parameters in the following order:

- 1. Chapter 4: The operating mode: rechargeable battery, primary cell mode, battery protection (reg\_lts\_cfg)

- 2. Chapter 5: The absolute min/max voltages (reg\_v\_bat\_max\_hi, reg\_v\_apl\_max\_hi, reg\_v\_bat\_min\_lo)

- 3. Chapter 6: The capacitor value connected on VDD\_STS (Csts).

- 4. Chapter 7: The VDD\_STS supervisory period Tsts\_period (*reg\_t\_sts\_period*)

- 5. Chapter 0: The v\_bat\_min hysteresis (reg\_v\_bat\_min\_hi\_dis, reg\_v\_bat\_min\_hi\_con)

- 6. Chapter 9: The value of **v\_apl\_max\_lo** (*reg\_v\_apl\_max\_lo*)

- 7. Chapter 10: The value of v\_bat\_max\_lo (reg\_v\_bat\_max\_lo)

- 8. Chapter 11: The VDD\_LTS supervisory period **Tlts\_period** and Tlts\_hrv\_low\_period (*reg\_t\_lts\_period*, *reg\_t\_hrv\_low\_cfg*)

# 3 VLD REFERENCE

The VLD is used to compare the current state of the voltages VDD\_STS or VDD\_LTS with a selected reference. The following registers select the references related to a voltage level:

- reg\_v\_bat\_max\_hi: reference v\_bat\_max\_hi

- reg\_v\_bat\_max\_lo: reference v\_bat\_max\_hi

- reg\_v\_bat\_min\_hi\_dis: reference v\_bat\_min\_hi when VDD\_STS & VDD\_LTS are disconnected

- reg\_v\_bat\_min\_hi\_con: reference v\_bat\_min\_hi when VDD\_STS & VDD\_LTS are connected

- reg\_v\_bat\_min\_lo: reference v\_bat\_min\_lo

- reg\_v\_apl\_max\_hi: reference v\_apl\_max\_hi

- reg\_v\_apl\_max\_lo: reference v\_apl\_max\_lo

These registers set the related reference level as follows:

$$V_{ref} = V_{lvl} \cdot (reg + 1)$$

## **Equation 1: VLD Reference Calculation**

The precision of VIvI is as follows:

|      | MIN <sub>(1)</sub> | ТҮР   | MAX <sub>(1)</sub> |

|------|--------------------|-------|--------------------|

| Vivi | 69 mV              | 73 mV | 76.2 mV            |

## **Table 3: VIvI Precision**

(1) These values are based on a typical spread of voltage level detector.

If the reference level is the maximum value of the hysteresis (\_hi), the maximum value of VIvI is used to calculate the related register.

If the reference level is the minimum value of the hysteresis (\_lo), the minimum value of VIvI is used to calculate the related register.

## 4 OPERATING MODE SETTINGS

## 4.1 Battery type

The first step is to set the type of battery used:

- Rechargeable (secondary cell battery; reg\_lts\_cfg.prim\_cell = '0')

- Non-rechargeable (primary cell battery; reg\_lts\_cfg.prim\_cell = '1')

### 4.2 Battery protection

By default the EM8500 checks the under voltage condition of the battery. It is possible to disable this function by setting the register *reg\_lts\_cfg.no\_bat\_protect* to '1'. In this condition, the EM8500 will try indefinitely to start-up on the battery voltage. If there is no energy from the HRV, the EM8500 will start-up by connecting VDD\_LTS to VDD\_STS, execute the boot sequence, as VDD\_LTS is lower than **v\_bat\_min\_lo** it will disconnect VDD\_STS and VDD\_LTS, then VDD\_STS will collapse and enter in power on reset. Therefore, the EM8500 will start-up again and loop in this sequence until energy is back from the HRV.

**Note:** We advise to avoid setting *reg\_lts\_cfg.no\_bat\_protect* to '1' with a rechargeable battery; it can damage the battery. It is preferable to do it only with a super capacitor.

### 4.3 Force connection of LTS to STS in primary cell mode

The register  $reg_lts_cfg.prim_cell_connect$  forces the connection of LTS to STS in primary cell mode ( $reg_lts_cfg.prim_cell = '1'$ ). If this bit is set to '1' in the NVM (address 0x46), the connection will be effective after the start-up sequence. This bit has no effect when  $reg_lts_cfg.prim_cell = '0'$  or if VDD\_LTS is lower than **v\_bat\_min\_lo**.

## 5 ABSOLUTE VALUES SETTINGS

There are 3 absolute values to set up in the EM8500:

- 1. The maximum battery voltage: v\_bat\_max\_hi

- 2. The maximum application voltage: v\_apl\_max\_hi

- 3. The minimum battery voltage (considered also as minimum application voltage): v\_bat\_min\_lo

#### 5.1 Maximum battery voltage

This is the absolute overvoltage limit of the battery. When the supply VDD\_LTS reaches this voltage, the EM8500 stops charging the battery. The register *reg\_v\_bat\_max\_hi* defines the absolute maximum battery voltage and is calculated as follows:

$$reg_v\_bat\_max\_hi = trunc\left(\frac{v\_bat\_max\_hi}{max(V_{lvl})} - 1\right) + 1$$

Equation 2: reg\_v\_bat\_max\_hi Calculation

#### 5.2 Maximum application voltage

This level is used when the maximum battery voltage is higher than the voltage the application can afford. If VDD\_STS is higher than this level, the EM8500 will automatically enable the LDO connected on VSUP to protect the application against overvoltage. The register *reg\_v\_apl\_max\_hi* defines the absolute maximum application voltage and is calculated as follows:

$$reg\_v\_apl\_max\_hi = trunc\left(\frac{v\_apl\_max\_hi}{max(V_{lvl})} - 1\right) + 1$$

Equation 3: *reg\_v\_apl\_max\_hi* Calculation

If the application maximum voltage is higher than the maximum battery voltage, *reg\_v\_apl\_max\_h* shall be set to 0x3F and *reg\_v\_apl\_max\_lo* shall be set to 0x3E. In this condition these two registers will be ignored.

#### 5.3 Minimum battery voltage

The absolute under voltage condition level of the battery is **v\_bat\_min\_lo**. When VDD\_LTS is below that level, the battery is in protected mode and the flag BAT\_LOW stays at '1' until VSUP is on. In that condition it is impossible to use the battery as source of energy, only the harvester can supply the application. The register *reg\_v\_bat\_min\_lo* defines this level as follows:

$$reg\_v\_bat\_min\_lo = trunc\left(\frac{v\_bat\_min\_lo}{\min(V_{lvl})} - 1\right)$$

Equation 4: reg\_v\_bat\_min\_lo Calculation

## 6 SHORT TERM STORAGE CAPACITOR SETTING

If the application is supposed to always run on LTS (VDD\_STS always connected to VDD\_LTS), we advise to use Csts= 10uF. But if STS supplies the application without the help of the battery or super capacitor, as it is the case in primary cell mode, the value of Csts shall be carefully calculated.

When VAUX[i] or VSUP is enabled, the decoupling capacitors Caux[i] or Csup is suddenly connected to Csts. Therefore the transfer of charges from Csts to the decoupling capacitor leads to a drop on VDD\_STS. We advise to avoid a drop higher than 10% of VDD\_STS.

Thus, Csts shall be 10 times bigger than the total amount of decoupling capacitors enabled in the same time. For instance if VSUP and all VAUX[i] are enabled in the same time:

$C_{STS} = 10 \cdot \left( C_{SUP} + C_{AUX[0]} + C_{AUX[1]} + C_{AUX[2]} \right)$

Equation 5: Csts Calculaton; all Decoupling Capacitors Enabled Together

## 7 STS SURVEY PERIOD

The survey period affects the power loss of the VLD during the measurement of STS. Longer this period, lower the power loss. The register *reg\_t\_sts\_period* is a number of t\_frame of 1ms and is calculated as follows:

$$T_{sts\_period} = \frac{P_{vld} \cdot t\_frame}{4 \cdot P_{in\_min} \cdot VLD_{loss}} = \frac{3 \cdot 10^{-9}}{4 \cdot P_{in\_min} \cdot VLD_{loss}}$$

Equation 6: STS Survey Period Calculation

The parameter PvId (in [W]) is the power dissipated by the VLD when enabled: 3uW (constant)

The parameter t\_frame (in [s]) is the minimum period between 2 measurements: 1ms (constant) The parameter Pin\_min (in [W]) is the minimum power the EM8500 can harvest before entering in HRV\_LOW mode.

The parameter VLDloss (without unit) is the rate of power the user accepts to lose in the VLD measurement of VDD\_STS.

**Important note:** when VDD\_STS is connected to VDD\_LTS Tsts\_period is not used anymore. The supervisory period is set by **Tlts\_period** instead (see chapter 11). Therefore, there is no VLDloss due to STS measurement in that condition.

The register reg\_t\_sts\_period shall be selected according to the following table to be the closest to Tsts\_period:

| reg_t_sts_period | Tsts_period |

|------------------|-------------|

| 000              | 1ms         |

| 001              | 2ms         |

| 010              | 8ms         |

| 011              | 16ms        |

| 100              | 32ms        |

| 101              | 64ms        |

| 110              | 128ms       |

| 111              | 256ms       |

Table 4: Tsts\_period Related Registers Selection

#### 7.1 Example of STS survey period calculation

Considering that the EM8500 has been configured to stop harvesting energy when the input power is below 2uW: Pin\_min = 2uW

We accept to lose 1% of power in the VLD measurement of VDD\_STS: VLDloss = 0.01

$$T_{sts\_period} = \frac{3 \cdot 10^{-9}}{4 \cdot 2 \cdot 10^{-6} \cdot 0.01} = 37.5 \cdot 10^{-3}$$

#### **Equation 7: Example of STS Survey Period Calculation**

According to the Table 4, the closest value to 37.5ms is 32ms, corresponding to  $reg_t_sts_period = "100"$ . In that condition the power loss in the VLD would be about 1.2%.

## 8 HYSTERESIS ON V\_BAT\_MIN SETTINGS

The voltage level **v\_bat\_min\_hi** defines an hysteresis with **v\_bat\_min\_lo**. It has a particular importance to supervise STS when VDD\_STS and VDD\_LTS are disconnected; in primary cell mode or when VDD\_LTS falls below **v\_bat\_min\_lo**.

#### 8.1 Level v\_bat\_min\_hi with VDD\_STS and VDD\_LTS disconnected

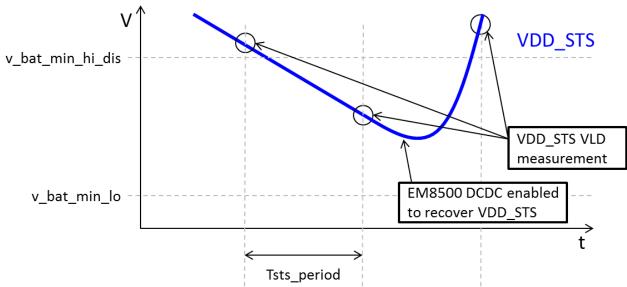

The level **v\_bat\_min\_hi** is set by the register *reg\_v\_bat\_min\_hi\_dis* when VDD\_STS and VDD\_LTS are disconnected. When the EM8500 DCDC converter does not charge Csts and VDD\_STS and VDD\_LTS are disconnected, Csts is the only source of energy for the application. Depending on the current consumption of the application in that condition, Csts will drop more or less quickly. If VDD\_STS falls below the level **v\_bat\_min\_lo**, the EM8500 will stop supplying the application; it will disable VSUP and VAUX[i]. As soon as the VLD measures VDD\_STS below **v\_bat\_min\_hi\_dis**, the EM8500 DCDC converter is enabled to recover VDD\_STS as shown in the following figures:

Figure 1: VDD\_STS Measurement Toward v\_bat\_min\_hi\_dis

The voltage difference between v\_bat\_min\_hi\_dis and v\_bat\_min\_lo shall be higher than the voltage drop on VDD\_STS between 2 Tsts\_period with the maximum current consumption. The following equation calculates v\_bat\_min\_hi\_dis:

$$v\_bat\_min\_hi\_dis = \frac{2 \cdot T_{sts\_period} \cdot I_{max}}{C_{sts}} + v\_bat\_min\_lo$$

#### Equation 8: v\_bat\_min\_hi\_dis Calculation

Imax (in [A]) is the maximum current consumption on application side. Tsts\_period (in [s]) is the period between 2 VDD\_STS VLD measurements defined in chapter 7. Csts (in [F]) is the capacitor connected to VDD\_STS.

## 8.2 Example of v\_bat\_min\_hi\_dis calculation

Considering that Tsts\_period is 32ms, Csts is 100uF, the maximum consumption of the application is 1mA and the absolute minimum battery voltage is 1.2V. According to the Equation 8, the value of  $v_bat_min_hi_dis$  shall be at least 1.84V.

The register *reg\_v\_bat\_min\_hi\_dis* is calculated as follows:

$$reg_v\_bat\_min\_hi\_dis = trund\left(\frac{v\_bat\_min\_hi\_dis}{\max(V_{lvl})} - 1\right) + 1$$

#### Equation 9: Register reg\_v\_bat\_min\_hi\_dis Calculation

In our example the value of reg\_v\_bat\_min\_hi\_dis = 24 (0x18 in hexadecimal)

## 8.3 Level v\_bat\_min\_hi with VDD\_STS and VDD\_LTS connected

The level **v\_bat\_min\_hi** is set by the register *reg\_v\_bat\_min\_hi\_con* when VDD\_STS and VDD\_LTS are connected. This level defines a hysteresis with **v\_bat\_min\_lo**. As LTS has a huge capacity compare to Csts, this parameter is less crucial than **v\_bat\_min\_hi\_dis**. This hysteresis delimitates the VDD\_LTS voltage range wherein the flag BAT\_LOW is set to '1' before stopping the supply of the application (disabling VSUP and VAUX[i]). The difference between **v\_bat\_min\_hi\_con** and **v\_bat\_min\_lo** is depending on the battery discharge curve. There is only one strict rule:

$reg_v_bat_min_hi_con \ge reg_v_bat_min_lo+1$

Equation 10: reg\_v\_bat\_min\_hi\_con Toward reg\_v\_bat\_min\_lo Conditions

## 9 LEVEL V\_APL\_MAX\_LO SETTINGS

As already written in chapter 5.2, the levels **v\_apl\_max\_lo** and **v\_apl\_max\_hi** shall be set to 0x3F if the application can afford the absolute maximum battery voltage. In that condition, these two levels are ignored. If it is not the case, and if VDD\_STS and VDD\_LTS are disconnected, the level **v\_apl\_max\_lo** calculation shall fulfill 2 conditions:

- 1. The difference between v\_apl\_max\_lo and v\_bat\_min\_hi\_dis shall be enough high to let the EM8500 DCDC charging LTS a minimum of time.

- 2. The hysteresis between v\_apl\_max\_lo and v\_apl\_max\_hi shall be enough high to ensure VDD\_STS will never rise above v\_apl\_max\_hi.

#### 9.1 Level v\_apl\_max\_lo toward v\_bat\_min\_hi

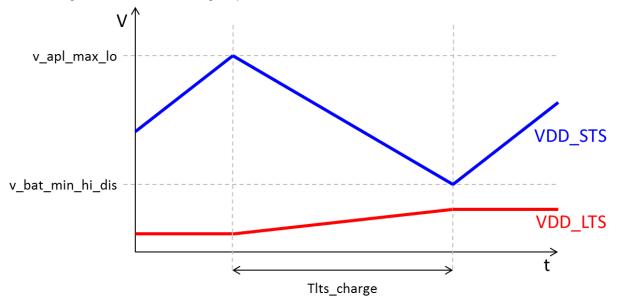

When VDD\_LTS and VDD\_STS are disconnected, the EM8500 DCDC charges alternatively STS and LTS. When the VLD detects that STS reached **v\_apl\_max\_lo**, the EM8500 DCDC stops charging STS and starts charging LTS. In that condition STS is the only source of energy of the application. It drops down to **v\_bat\_min\_hi\_dis** and then the EM8500 charges back STS. To charge the battery in an efficient way, the period during which the EM8500 DCDC charges LTS shall be as long as possible.

Figure 2: Effect of v\_apl\_max\_lo Level on VDD\_LTS Charge Phase Period

Considering Tlts\_charge\_min is the minimum period we want to guarantee, the condition **v\_apl\_max\_lo** level shall fulfill toward **v\_bat\_min\_hi\_dis** is the following:

$$v\_apl\_max\_lo \ge \frac{T_{lts\_charge\_min} \cdot I_{max}}{C_{sts}} + v\_bat\_min\_hi\_dis$$

Equation 11: v\_apl\_max\_lo toward v\_bat\_min\_hi\_dis Condition

## 9.2 Level v\_apl\_max\_lo toward v\_apl\_max\_hi

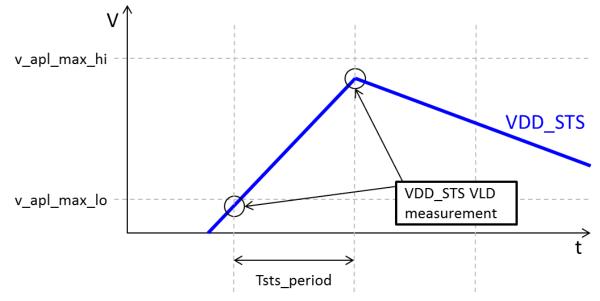

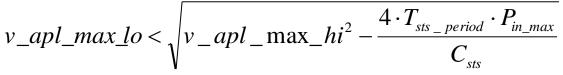

When the EM8500 DCDC charges STS at full power, VDD\_STS rising edge can be sharp and therefore, depending on Tsts\_period, rise above v\_apl\_max\_hi if there is not enough hysteresis between v\_apl\_max\_lo and v\_apl\_max\_hi.

Figure 3: VDD\_STS Measurement Toward v\_apl\_max\_lo

The sharpness of VDD\_STS rising edge is depending on the maximum power the EM8500 DCDC can harvest. To have enough margins, we consider that the EM8500 DCDC has an ideal efficiency of 100%. When the EM8500 DCDC converter charges STS, the maximum power that the EM8500 DCDC can deliver is limited even if the HRV can potentially deliver more power (when charging LTS there is no such limitation). The maximum power Pin\_max that the DCDC converters can deliver to STS depends mainly on Vmpp in best case conditions, meaning at maximum luminescence for a solar cell for instance. Pin\_max is calculated as follows:

$$P_{in\_max} = 6.65 \cdot 10^{-3} \cdot Vmpp^2$$

Equation 12: Pin\_max Caclulation

**Note:** the chapter 2 of the document *e8500\_app\_note\_hrv\_param.pdf* describes how to calculate Vmpp. The level **v\_apl\_max\_lo** shall fulfill the following equation to ensure VDD\_STS will never rise above **v\_apl\_max\_hi** when the DCDC converter charges STS.

Equation 13: v\_apl\_max\_lo toward v\_apl\_max\_hi Condition

## 9.3 Level v\_apl\_max\_lo adjustment

The level **v\_apl\_max\_lo** shall fulfill both Equation 11 and Equation 13. If it is not the case, there are two main ways to correct it:

- 1. Reduce Tsts\_period: it impacts the efficiency at very low power range; it is in the majority of the cases negligible. The value of VLDloss shall be reconsidered in Equation 6.

- 2. Increase Csts: it can impacts the mechanical size of the component and its cost. The solution 1 is preferable.

## 9.4 Level v\_apl\_max\_lo with VDD\_STS and VDD\_LTS connected

If VDD\_LTS and VDD\_STS are **always** connected, the calculation of **v\_apl\_max\_lo** is less critical and shall only fulfill the following rule:

$reg_v_apl_max_lo \le reg_v_apl_max_hi-1$

Equation 14: reg\_v\_apl\_max\_lo toward reg\_v\_apl\_max\_hi Condition

## 10 LEVEL V\_BAT\_MAX\_LO SETTINGS

If the application can afford the maximum battery voltage, **v\_apl\_max\_lo** and **v\_apl\_max\_hi** are set to 0x3F and respectively 0x3E and not used. In that case, the conditions defined by the Equation 11 and Equation 13 shall be applied to **v\_bat\_max\_lo** as follows:

$\frac{T_{lts\_charge\_min} \cdot I_{max}}{Csts} + v\_bat\_min\_hi\_dis \le v\_bat\_max\_lo < \sqrt{v\_bat\_max\_hi^2} - \frac{4 \cdot T_{sts\_period} \cdot P_{in\_max}}{C_{sts}}$

#### Equation 15: v\_bat\_max\_lo Conditions; v\_apl\_max\_lo and v\_apl\_max\_hi not Used

If both conditions of Equation 15 cannot be fulfilled, the corrective actions are the same then the one defined in chapter 9.3.

### 10.1 Level v\_bat\_max\_lo with VDD\_STS and VDD\_LTS connected

If VDD\_LTS and VDD\_STS are **always** connected or if **v\_apl\_max\_lo** and **v\_apl\_max\_hi** are used, the calculation of **v\_bat\_max\_lo** is less critical and shall only fulfill the following rule:

$reg_v_bat_max_lo \le reg_v_bat_max_hi-1$

Equation 16: reg\_v\_bat\_max\_lo toward reg\_v\_bat\_max\_hi Condition

## 11 LTS SURVEY PERIOD

As LTS is huge compare to STS, the LTS survey period **Tlts\_period** is not critical at all. It could be set to a high value without any impact. The power consumption of LTS survey, when **Tlts\_period** is 1s, is less than 1nW. In HRV\_LOW mode, this period (**Tlts\_period\_hrv\_low**) is set by *reg\_t\_hrv\_low\_cfg.t\_lts\_hrv\_low\_period* to a different value, but as in operating the impact is negligible. We advise the user to set **Tlts\_period** to 1s and **Tlts\_period\_hrv\_low** to 2s as follows:

$reg_t_lts_period = 101$

reg\_t\_hrv\_low\_cfg.t\_lts\_hrv\_low\_period = 101

**Tits\_period** is set by the registers reg\_t\_lts\_period and reg\_t\_hrv\_low\_cfg.t\_lts\_hrv\_low\_period as follows:

|           | Tlts_period                    | TIts_period in HRV_LOW mode                          |

|-----------|--------------------------------|------------------------------------------------------|

| Reg value | register :<br>reg_t_lts_period | register :<br>reg_t_hrv_low_cfg.t_lts_hrv_low_period |

| 000       | 1ms                            | 2ms                                                  |

| 001       | 4ms                            | 8ms                                                  |

| 010       | 16ms                           | 32ms                                                 |

| 011       | 64ms                           | 128ms                                                |

| 100       | 256ms                          | 512ms                                                |

| 101       | 1s                             | 2s                                                   |

| 110       | 4s                             | 8s                                                   |

| 111       | 16s                            | 32s                                                  |

Table 5: Tlts\_period and Tlts\_period\_hrv\_low Related Registers Selection

**Note:** At start-up the EM8500 waits **Tits\_period** before to enable VSUP. Usually this is not critical as the start-up is executed one time in the life of the product.

16

# **TABLE OF CONTENTS**

| Storage elements STS/LTS supervising                         | 1  |

|--------------------------------------------------------------|----|

| ABSTRACT                                                     | 1  |

| ABBREVIATIONS                                                | 1  |

| 1 Scope                                                      | 2  |

| 2 Supervising registers settings sequence                    | 4  |

| 3 VLD reference                                              | 5  |

| 4 Operating mode settings                                    | 6  |

| 4.1 Battery type                                             | 6  |

| 4.2 Battery protection                                       | 6  |

| 4.3 Force connection of LTS to STS in primary cell mode      | 6  |

| 5 Absolute values settings                                   | 7  |

| 5.1 Maximum battery voltage                                  | 7  |

| 5.2 Maximum application voltage                              | 7  |

| 5.3 Minimum battery voltage                                  | 7  |

| 6 Short term storage capacitor setting                       | 8  |

| 7 STS survey period                                          | 9  |

| 7.1 Example of STS survey period calculation                 | 9  |

| 8 Hysteresis on v_bat_min settings                           | 10 |

| 8.1 Level v_bat_min_hi with VDD_STS and VDD_LTS disconnected | 10 |

| 8.2 Example of v_bat_min_hi_dis calculation                  | 10 |

| 8.3 Level v_bat_min_hi with VDD_STS and VDD_LTS connected    | 11 |

| 9 Level v_apl_max_lo settings                                | 12 |

| 9.1 Level v_apl_max_lo toward v_bat_min_hi                   | 12 |

| 9.2 Level v_apl_max_lo toward v_apl_max_hi                   | 13 |

| 9.3 Level v_apl_max_lo adjustment                            | 13 |

| 9.4 Level v_apl_max_lo with VDD_STS and VDD_LTS connected    | 14 |

| 10 Level v_bat_max_lo settings                               | 15 |

| 10.1 Level v_bat_max_lo with VDD_STS and VDD_LTS connected   | 15 |

| 11 LTS survey period                                         | 16 |

## LIST OF TABLES

| Table 1: List of Registers Related to Storage Elements Supervising       | 2  |

|--------------------------------------------------------------------------|----|

| Table 2: Mapping of Registers in EEPROM                                  |    |

| Table 3: VIvI Precision                                                  | 5  |

| Table 4: Tsts_period Related Registers Selection                         | 9  |

| Table 5: Tlts_period and Tlts_period_hrv_low Related Registers Selection | 16 |

# **LIST OF FIGURES**

| Figure 1: VDD_STS Measurement Toward v_bat_min_hi_dis                | 10 |

|----------------------------------------------------------------------|----|

| Figure 2: Effect of v_apl_max_lo Level on VDD_LTS Charge Phase Delay | 12 |

| Figure 3: VDD_STS Measurement Toward v_apl_max_lo                    | 13 |

## LIST OF EQUATIONS

EM Microelectronic-Marin SA ("EM") makes no warranties for the use of EM products, other than those expressly contained in EM's applicable General Terms of Sale, located at http://www.emmicroelectronic.com. EM assumes no responsibility for any errors which may have crept into this document, reserves the right to change devices or specifications detailed herein at any time without notice, and does not make any commitment to update the information contained herein.

No licenses to patents or other intellectual property rights of EM are granted in connection with the sale of EM products, neither expressly nor implicitly.

In respect of the intended use of EM products by customer, customer is solely responsible for observing existing patents and other intellectual property rights of third parties and for obtaining, as the case may be, the necessary licenses.

Important note: The use of EM products as components in medical devices and/or medical applications, including but not limited to, safety and life supporting systems, where malfunction of such EM products might result in damage to and/or injury or death of persons is expressly prohibited, as EM products are neither destined nor qualified for use as components in such medical devices and/or medical applications. The prohibited use of EM products in such medical devices and/or medical applications is exclusively at the risk of the customer