# SUPPLY OUTPUTS VSUP / VAUX / VAUX\_GND CONTROL

Product Family:

Part Number: EM8500

Keywords: Harvesting, Solar, TEG, MPPT, Configuration, Setup, Super capacitors, Secondary Battery, Primary Battery, LDO

#### ABSTRACT

The EM8500 offers a NVM containing all the configuration parameters. This document describes how to setup the registers in NVM linked to the control of the supply outputs VSUP, VAUX[2:0], VAUX\_GND[2:0]:

EM850X

• Enable and disable the supply outputs

- Configure direct or regulated supply outputs

- Configure the sleep mode and wake-up system

- Configure the supply outputs behavior in HRV\_LOW mode

#### **ABBREVIATIONS**

| NVM                  | Non-Volatile-Memory                                                                                                                                                                          |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MCU                  | Microcontroller Unit                                                                                                                                                                         |

| STS                  | Short term storage element (capacitor connected to VDD_STS)                                                                                                                                  |

| LTS                  | Long term storage element (rechargeable battery connected to VDD_LTS)                                                                                                                        |

| HRV                  | Harvester, main source of energy (solar or TEG)                                                                                                                                              |

| TEG                  | Thermal Electrical Generator                                                                                                                                                                 |

| BAT_LOW              | Flag indicating that the battery is in under-voltage condition                                                                                                                               |

| HRV_LOW              | Flag indicating that the HRV is under the minimum power level (HRV low mode when at 1)                                                                                                       |

| VSUP                 | Main output supply for application                                                                                                                                                           |

| VAUX[ <i>i</i> ]     | 3 independent auxiliary supplies for application ( <i>i</i> is in the range 0 to 2)                                                                                                          |

| VAUX_GND[ <i>i</i> ] | 3 independent switches to ground ( <i>i</i> is in the range 0 to 2)                                                                                                                          |

| ULP LDO              | LDO dedicated to VSUP                                                                                                                                                                        |

| v_ulp_ldo            | ULP LDO voltage level in [V]                                                                                                                                                                 |

| VAUX LDO             | LDO common to all VAUX[i]                                                                                                                                                                    |

| v_aux_ldo            | VAUX LDO voltage level in [V]                                                                                                                                                                |

| Csup                 | Decoupling capacitor on VSUP                                                                                                                                                                 |

| Caux[ <i>i</i> ]     | 3 decoupling capacitors on VAUX[ <i>i</i> ] ( <i>i</i> is in the range 0 to 2)                                                                                                               |

| Sleep                | VSUP is disabled when the sleep mode is active                                                                                                                                               |

| v_apl_max_hi         | Absolute maximum application voltage                                                                                                                                                         |

| v_apl_max_lo         | Maximum voltage of the application, form an hysteresis with v_apl_max_hi                                                                                                                     |

| v_bat_min_hi         | Minimum battery and application voltage define by v_bat_min_hi_dis when STS and LTS are disconnected; otherwise it is defined by v_bat_min_hi_con. It forms an hysteresis with v_bat_min_lo. |

| v_bat_min_lo         | Absolute minimum value of the battery and the application                                                                                                                                    |

# 1 SCOPE

The EM8500 generates 4 supply outputs for external application:

- VSUP: main supply output, used usually to supply the main MCU

- Can be directly connected to VDD\_STS or regulated by ULP\_LDO

- Can be configured to be disabled in HRV\_LOW mode

- $\circ$   $\,$  Can be disabled (sleep mode) for a predefine duration

- Wake-up pin can force VSUP out of sleep mode

- Can be configured to be tied to ground or floating when disabled

- VAUX[*i*]: 3 independent supply outputs for peripherals such as RF transmitters, sensors etc...

- Can be directly connected to VDD\_STS or regulated independently by VAUX LDO

- o Can be configured to be disabled in HRV\_LOW mode independently

- o Can be disabled / enabled independently

- o Can be configured to be tied to ground or floating when disabled independently

- VAUX\_GND[/]: 3 independents switches to ground

- Can cut the ground of a peripheral; for instance to avoid current leakage through the pull-up of an I<sup>2</sup>C line

- o Can be disabled / enabled independently

| Register name    | Address    | Description                                                                                                                                                                         |

|------------------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                  | 0x0E       | <pre>vsup_tied_low:<br/>In sleep mode VSUP is connected to ground if vsup_tied_low = '1'<br/>In sleep mode VSUP is floating if vsup_tied_low = '0'</pre>                            |

| reg_ldo_cfg      |            | v_vaux_ldo[2:0]: Regulation level of VAUX LDO                                                                                                                                       |

|                  |            | <pre>frc_ulp_ldo: VSUP is always regulated by ULP_LDO when enabled</pre>                                                                                                            |

|                  |            | v_ulp_ldo[2:0]: Regulation level of ULP_LDO                                                                                                                                         |

|                  | 0x0F       | <pre>dis_vaux_gnd[i]_hrv_low: VAUX_GND[i] is disabled in HRV_LOW mode when at '1'</pre>                                                                                             |

| reg_pwr_cfg      |            | <pre>dis_vaux[i]_hrv_low: VAUX[i] is disabled in HRV_LOW mode when at '1'</pre>                                                                                                     |

|                  |            | <pre>dis_vsup_hrv_low: VSUP is disabled in HRV_LOW mode when at '1'</pre>                                                                                                           |

|                  | 0x10       | <pre>vaux[i]_cfg[1:0]:<br/>When "00": Configure VAUX[i] to be connected to VDD_STS when enabled<br/>When "01": Configure VAUX[i] to be connected to VAUX LDO when<br/>enabled</pre> |

| reg_vaux_cfg     |            | When "10": Configure VAUX[ <i>i</i> ] to be connected to VAUX LDO only when VDD_STS is above <b>v_apl_max_hi</b> , VAUX[ <i>i</i> ] is floating when disabled                       |

|                  |            | When "11": Configure VAUX[ <i>i</i> ] to be connected to VAUX LDO only when VDD_STS is above <b>v_apl_max_hi</b> , VAUX[ <i>i</i> ] is connected to ground when disabled            |

|                  | d_cfg 0x11 | <pre>vaux_gnd[i]_cfg:<br/>When '0': Configure VAUX_GND[i] to be always connected to ground when</pre>                                                                               |

| reg_vaux_gnd_cfg |            | enabled                                                                                                                                                                             |

|                  |            | When '1': Configure VAUX_GND[ <i>i</i> ] to be connected to ground only when enabled and VDD_STS is lower than <b>v_apl_max_hi</b>                                                  |

The following registers are involved for that action:

## **APPLICATION NOTE | EM8500**

Subject to change without notice 608001, Version 1.0, 21-July-2015 Copyright @ 2015, www.emmicroelectronic.com

| Register name        | Address | Description                                                                                                                                                                                                                                                                                                                                                                                                            |  |

|----------------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| reg_ext_cfg          | 0x13    | <ul> <li>wake_up_deb_en: debouncer is connected to the pin wake-up when at '1'</li> <li>wake_up_edge_cfg[1:0]:</li> <li>When "00": wake-up pin is sensitive to no edge (wake-up disabled)</li> <li>When "01": wake-up pin is sensitive to the falling edge</li> <li>When "10": wake-up pin is sensitive to the rising edge</li> <li>When "11": wake-up pin is sensitive to the falling and the rising edges</li> </ul> |  |

| reg_t_sleep_vsup_lo  | 0x14    | Sleep wake-up counter duration coded over 3 bytes:<br>reg_t_sleep_vsup[23:0] = reg_t_sleep_vsup_hi & reg_t_sleep_vsup_mid &<br>reg_t_sleep_vsup_lo                                                                                                                                                                                                                                                                     |  |

| reg_t_sleep_vsup_mid | 0x15    |                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| reg_t_sleep_vsup_hi  | 0x16    |                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| reg_pwr_mgt          | 0x19    | <pre>frc_prim_dcdc_dis: force the EM8500 DCDC off when at '1' vaux_gnd[i]_en: connects VAUX_GND[i] to ground when at '1' vaux[i]_en: enable VAUX supply when at '1' sleep_vsup: set VSUP in sleep mode when at '1'</pre>                                                                                                                                                                                               |  |

Table 1: List of Registers Related to Supply Outputs Control

The default value after reset or start-up of the registers listed in

8

is contained in a NVM memory at the following related addresses:

| Register name        | Register<br>Address | Related add | ress in NVM |

|----------------------|---------------------|-------------|-------------|

| reg_ldo_cfg          | 0x0E                | eeprom14    | 0x4E        |

| reg_pwr_cfg          | 0x0F                | eeprom15    | 0x4F        |

| reg_vaux_cfg         | 0x10                | eeprom16    | 0x50        |

| reg_vaux_gnd_cfg     | 0x11                | eeprom17    | 0x51        |

| reg_ext_cfg          | 0x13                | eeprom19    | 0x53        |

| reg_t_sleep_vsup_lo  | 0x14                | eeprom20    | 0x54        |

| reg_t_sleep_vsup_mid | 0x15                | eeprom21    | 0x55        |

| reg_t_sleep_vsup_hi  | 0x16                | eeprom22    | 0x56        |

| reg_pwr_mgt          | 0x19                | eeprom25    | 0x59        |

#### Table 2: Relation between Register and Corresponding NVM Address

Note: offset between the register addresses and related address in NVM is 0x40

## 2 VSUP SETTINGS

VSUP is the main supply output used to supply the main MCU of the application. VSUP is enabled by default and, with one exception, cannot be permanently disabled. The user can set VSUP in sleep mode; this action disables VSUP for a predefined duration to reduce the consumption of the system as much as possible. The pin wake-up stops the sleep mode at any time.

It is possible to permanently disable VSUP only in HRV\_LOW mode. But we strongly advise never to use this option; the system can enter into a dead lock.

The voltage VDD\_STS supplies VSUP directly or through the ULP LDO. The ULP LDO ensures that VSUP never rises above **v\_apl\_max\_hi**. The user can force the ULP LDO even if VDD\_STS is lower than **v\_apl\_max\_hi**.

#### 2.1 VSUP enable conditions

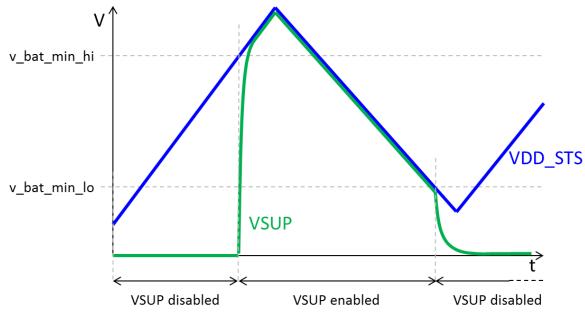

The EM8500 enables VSUP as soon as VDD\_STS rises above **v\_bat\_min\_hi** and disables VSUP when VDD\_STS falls below **v\_bat\_min\_lo**.

Figure 1: VSUP Enable Condition Dependence on VDD\_STS

The following conditions also disable VSUP:

- In "VSUP sleep mode", when the bit register *reg\_pwr\_mgt.sleep\_vsup* is set to '1'

- The bit register *reg\_pwr\_cfg.dis\_vsup\_hrv\_low* is set to '1' and the EM8500 in HRV\_LOW mode

## 2.2 VSUP disabled

If the register *reg\_ldo\_cfg.vsup\_tied\_low* = '1', the EM8500 connects VSUP to the ground in disabled state, otherwise VSUP is floating in disabled state.

As shown in chapter 2.1, VSUP is disabled when *reg\_pwr\_cfg.dis\_vsup\_hrv\_low* is set to '1' and the EM8500 in HRV\_LOW mode. This register shall be carefully handled, when it is at '1' it is not possible to recover the supply output VSUP as long as there is no energy from the harvester. **We strongly advise never to set** *reg\_pwr\_cfg.dis\_vsup\_hrv\_low* to '1'.

#### 2.3 VSUP sleep mode

When the bit register *reg\_pwr\_mgt.sleep\_vsup* is set to '1', the EM8500 enters in "VSUP sleep mode" and disables VSUP and thus stops supplying the main application MCU. In such mode, a counter automatically starts and restores VSUP only when it reaches the value t\_sleep\_vsup set in the register *reg\_t\_sleep\_vsup[23:0]*. This register is a concatenation of the 3 registers *reg\_t\_sleep\_vsup\_hi* & *reg\_t\_sleep\_vsup\_mid* & *reg\_t\_sleep\_vsup\_lo*:

reg t sleep vsup[23:0] = t sleep  $vsup[s] \cdot 1000$

#### Equation 1: t\_sleep\_vsup Calculation

The maximum t\_sleep\_vsup duration is 0xFFFFFF \* 1ms ≈ 4h 39min 37s.

## 2.4 Wake-up pin

The pin WAKE\_UP restores VSUP from sleep mode and resets the sleep counter. It is possible to select on which edge the pin WAKE\_UP is sensitive with the register *reg\_ext\_cfg.wake\_up\_edge\_cfg[1:0]* as follows:

| reg_ext_cfg.wake_up_edge_cfg[1:0] | wake-up edge selection         |

|-----------------------------------|--------------------------------|

| 00                                | No edge (wake-up pin disabled) |

| 01                                | Falling edge                   |

| 10                                | Rising edge                    |

| 11                                | Both edges                     |

#### Table 3: WAKE\_UP Edge Selection

The bit register *reg\_ext\_cfg.wake\_up\_deb\_en* enables a debouncer on the pin WAKE\_UP when it is at '1'. The state of WAKE\_UP shall be stable during at least 171ms to take effect. If the debouncer is disabled, the latency of the pin WAKE\_UP is 1us on the rising edge and 100us on the falling edge.

## 2.5 ULP LDO

The level **v\_apl\_max\_hi** is the maximum value the application can afford. If VDD\_STS rises above this level, the EM8500 disconnects VSUP from VDD\_STS and enables the ULP LDO to regulate VSUP. To reduce the noise on VSUP or to get a stable DC voltage on VSUP, it is possible to force VSUP to always be connected to the ULP LDO. When the register *reg\_ldo\_cfg.frc\_ulp\_ldo* = '1', ULP LDO always regulates VSUP when it is enabled. The register *reg\_ldo\_cfg.v\_ulp\_ldo[2:0]* selects the ULP LDO voltage level **v\_ulp\_ldo** as follows:

| reg_ldo_cfg.v_ulp_ldo[2:0] | v_ulp_ldo [V] |

|----------------------------|---------------|

| 000                        | 1.2           |

| 001                        | 1.55          |

| 010                        | 1.65          |

| 011                        | 1.8           |

| 100                        | 2             |

| 101                        | 2.2           |

| 110                        | 2.4           |

| 111                        | 2.6           |

#### Table 4: ULP LDO Voltage Level Selection

#### 2.6 VSUP output capability

When VSUP is connected to VDD\_STS, the connection through the switch has a typical resistor of 7.40hm. The VSUP LDO has an output capability of 10mA at a maximum drop of 100mV.

## 3 VAUX SETTINGS

VAUX[2:0] are 3 independent supply outputs. They usually supply peripherals such as RF transmitter, sensors etc... The user can set each of them independently to be disabled, connected to VDD\_STS or regulated by the common VAUX LDO.

## 3.1 VAUX enable conditions

The user can enable any VAUX[*i*] as soon as VDD\_STS rises above **v\_bat\_min\_hi**. The EM8500 disables all VAUX[2:0] when VDD\_STS falls below **v\_bat\_min\_lo**.

- Setting the register reg\_pwr\_mgt.vaux0\_en to '1' enables VAUX[0]

- Setting the register *reg\_pwr\_mgt.vaux1\_en* to '1' enables VAUX[1]

- Setting the register reg\_pwr\_mgt.vaux2\_en to '1' enables VAUX[2]

Each VAUX[*i*] can be configured independently with the register *reg\_vaux\_cfg.vaux[i]\_cfg[1:0]* as follows:

| reg_vaux_cfg.vaux[i]_cfg[1:0] | v_ulp_ldo [V]                                                                                                                                                 |

|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 00                            | Connect VAUX[/] to VDD_STS when enabled                                                                                                                       |

| 01                            | Connects VAUX[/] to VAUX LDO when enabled                                                                                                                     |

| 10                            | Connect VAUX[ <i>i</i> ] automatically to VAUX LDO when VDD_STS is above <b>v_apl_max_hi</b> , VAUX[ <i>i</i> ] is floating when disabled                     |

| 11                            | Configure VAUX[ <i>i</i> ] to be connected to VAUX LDO only when VDD_STS is above <b>v_apl_max_hi</b> , VAUX[ <i>i</i> ] is connected to ground when disabled |

## Table 5: VAUX[i] Configuration

When the register *reg\_pwr\_cfg.dis\_vaux[i]\_hrv\_low* = '1', the related VAUX[*i*] is automatically disabled when the EM8500 is in HRV\_LOW mode.

## 3.2 VAUX LDO

Unlike VSUP, VAUX can be connected to VDD\_STS even if VDD\_STS is above **v\_apl\_max\_hi** as defined in Table 5. The VAUX LDO is common to all VAUX[2:0], but each VAUX[*i*] can be independently connected to VAUX LDO. The register *reg\_ldo\_cfg.v\_vaux\_ldo*[2:0] selects the VAUX LDO voltage level **v\_aux\_ldo** as follows:

| reg_ldo_cfg.v_vaux_ldo[2:0] | v_aux_ldo [V] |

|-----------------------------|---------------|

| 000                         | 1.2           |

| 001                         | 1.55          |

| 010                         | 1.65          |

| 011                         | 1.8           |

| 100                         | 2             |

| 101                         | 2.2           |

| 110                         | 2.4           |

| 111                         | 2.6           |

Table 6: VAUX LDO Voltage Level Selection

## 4 VAUX\_GND SETTINGS

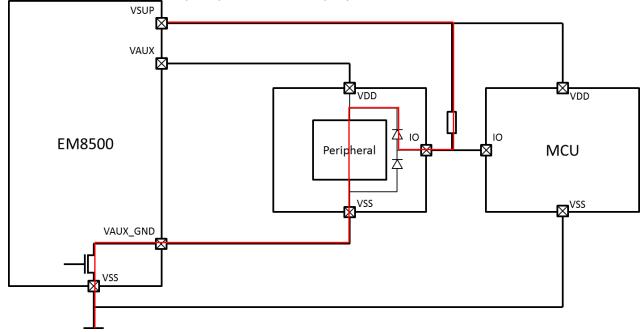

When VAUX[*i*] supplies a peripheral it could be necessary to cut the connection to the ground of that peripheral when VAUX[*i*] is disabled. In particular, if VSUP communicates with that peripheral through an I2C interface, it avoids drawing a current from the pull-up resistor into the peripheral.

#### Figure 2: Peripheral Supplied Through IO Protection Diodes

In the Figure 2, if VAUX\_GND is connected to the ground, the peripheral is supplied through the pull-up and the positive protection diode of IO pad, when VAUX is disabled. If VAUX\_GND is disabled, no current can flow through that path.

#### 4.1 VAUX\_GND enable conditions

The user can enable any VAUX\_GND[*i*] as soon as VDD\_STS rises above **v\_bat\_min\_hi**. The EM8500 disables all VAUX\_GND[2:0] when VDD\_STS falls below **v\_bat\_min\_lo**.

- Setting the register reg\_pwr\_mgt.vaux\_gnd0\_en to '1' connects VAUX\_GND[0] to VSS

- Setting the register reg\_pwr\_mgt.vaux\_gnd1\_en to '1' connects VAUX\_GND[1] to VSS

- Setting the register reg\_pwr\_mgt.vaux\_gnd2\_en to '1' connects VAUX\_GND[2] to VSS

Each VAUX\_GND[*i*] can be configured independently with the register *reg\_vaux\_gnd\_cfg.vaux\_gnd[i]\_cfg* as follows:

| reg_vaux_gnd_cfg.vaux_gnd[i]_cfg | v_ulp_ldo [V]                                                                                    |

|----------------------------------|--------------------------------------------------------------------------------------------------|

| 0                                | Connect VAUX_GND[ <i>i</i> ] to ground even if VDD_STS is above <b>v_apl_max_hi</b> when enabled |

| 1                                | Disconnect VAUX_GND[ <i>i</i> ] when VDD_STS is above <b>v_apl_max_hi</b> when enabled           |

## Table 7: VAUX\_GND[*i*] Configuration

When the register *reg\_pwr\_cfg.dis\_vaux\_gnd[i]\_hrv\_low* = '1', the related VAUX\_GND[*i*] is automatically disabled when the EM8500 is in HRV\_LOW mode.

Subject to change without notice 608001, Version 1.0, 21-July-2015 Copyright @ 2015, www.emmicroelectronic.com

#### 5 **NOISE REDUCTION**

The EM8500 DCDC generates noise that can disturb sensitive devices such as sensors. Setting the register

reg\_pwr\_mgr.frc\_prim\_dcdc\_dis to '1' will stop the DCDC conversion.

If VDD\_STS falls below v\_bat\_min\_hi, the register reg\_pwr\_mgr.frc\_prim\_dcdc\_dis is automatically reset to '0', thus the DCDC is reactivated.

# **TABLE OF CONTENTS**

| 1 | Sc  | ope                        | .2 |

|---|-----|----------------------------|----|

| 2 | VS  | UP settings                | .4 |

|   |     | VSUP enable conditions     |    |

|   | 2.2 | VSUP disabled              | .4 |

|   | 2.3 | VSUP sleep mode            | .4 |

|   | 2.4 | Wake-up pin                | .5 |

|   | 2.5 | ULP LDO                    | .5 |

|   | 2.6 | VSUP output capability     | .5 |

| 3 | VA  | UX settings                | .6 |

|   | 3.1 | VAUX enable conditions     | .6 |

|   |     | VAUX LDO                   |    |

| 4 | VA  | UX_GND settings            | .7 |

|   | 4.1 | VAUX_GND enable conditions | .7 |

| 5 | No  | ise reduction              | .8 |

## APPLICATION NOTE I EM8500

Subject to change without notice 608001, Version 1.0, 21-July-2015 Copyright @ 2015, www.emmicroelectronic.com

## LIST OF TABLES

| 3 |

|---|

| 3 |

| 5 |

| 5 |

| 6 |

| 6 |

| 7 |

| - |

# **LIST OF FIGURES**

| Figure 1: VSUP Enable Condition Dependence on VDD_STS      | 4 |

|------------------------------------------------------------|---|

| Figure 2: Peripheral Supplied Through IO Protection Diodes | 7 |

## LIST OF EQUATIONS

| Equation 1: t sleep vsup Calculation |  | ł |

|--------------------------------------|--|---|

|--------------------------------------|--|---|

EM Microelectronic-Marin SA ("EM") makes no warranties for the use of EM products, other than those expressly contained in EM's applicable General Terms of Sale, located at http://www.emmicroelectronic.com. EM assumes no responsibility for any errors which may have crept into this document, reserves the right to change devices or specifications detailed herein at any time without notice, and does not make any commitment to update the information contained herein.

No licenses to patents or other intellectual property rights of EM are granted in connection with the sale of EM products, neither expressly nor implicitly.

In respect of the intended use of EM products by customer, customer is solely responsible for observing existing patents and other intellectual property rights of third parties and for obtaining, as the case may be, the necessary licenses.

Important note: The use of EM products as components in medical devices and/or medical applications, including but not limited to, safety and life supporting systems, where malfunction of such EM products might result in damage to and/or injury or death of persons is expressly prohibited, as EM products are neither destined nor qualified for use as components in such medical devices and/or medical applications. The prohibited use of EM products in such medical devices and/or medical applications is exclusively at the risk of the customer